摘要:简要从硬件和软件两方面介绍一种嵌入式的多协议串行通信设计方案。该设计方案采用多协议串行通信控制器Z85C30及外围电路开发,通过软件编程,可满足各种串行通信要求,如异步、按字节同步、按位同步等通信格式。

关键词:嵌入式系统 串行通信控制器(SCC) Z85C30

引言

我们在嵌入式系统的开发过程中,经常需要设计串行通信口,用以同其它设备或计算机网络交换数据。针对不同的应用场合及不同的通信格式,在硬件设计方面有许多不同的芯片可供选择,如Intel 8251A、Intel 8274、Intel 82530等。采用ZILOG公司的串行通信控制器Z85C30进行设计,和其它器件相比,具有功能强、速度快、外部逻辑少等优点。

1 串行通信控制器Z85C30介绍

Z85C30是ZILOG公司推出的一种串行通信控制器(SCC)。它具有双通道,适用于8位、16位处理器的系统,能够完成串行到并行、并行到串行的转换。Z85C30能够处理诸如异步格式、面向字节的同步规程(如IBM双同步规程)、面向比特的同步规程(如HDLC、SDLC);能够产生、检查CRC循环冗余检验码。

Z85C30每个通道有14个写寄存器、7个读寄存器。通过对其编程,可将通信控制器配置满足各种格式,如数据长度、停止位的位数、有无奇偶检验等。

1.1 Z850C30主要性能

①同步速率。16MHz时钟下,传输速率达4Mb/s;使用16MHz时钟,传输速率达1Mb/s(FM编码);使用16MHz时钟,传输速率达500Kb/s(NRZI编码)。

②异步性能。每个字符5、6、7或8位;1/2或2位停止位;奇或偶校验;1、16、32、64倍时钟格式;断点产生和测试;奇偶、超载和帧出错测试。

③按字节同步性能。内同步或外同步;1或2个同步字符;自动CRC产生、测试。

④SDLC/HDLC性能。异常中止序列的产生和检测;“0”的自动插入和删除,报文间标志的自动插入,地址段的识别,信息段剩余管理,CRC产生、测试;具有EOP识别/循不入口和出口的SDLC方式;可选NRZ、NRZI、曼彻斯特或FM编/解码;具有时钟恢复能力的数字锁相环;具有自动回波和局部回送的诊断能力。

另外,Z85C30能在SDLC/HDLC方式下更高效地工作,如果有10%26;#215;19位SDLC/HDLC帧状态FIFO,14位SDLC/HDLC帧计数器,自动SDLC/HDLC标志发送,自动复位SDLC/HDLC Underrun/EOM标志,自动预置SDLC/HDLC CRC等。

1.2 Z85C30主要引脚简介

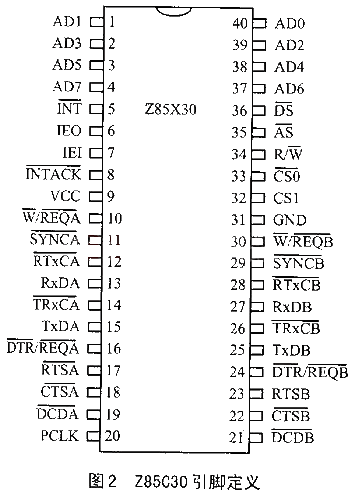

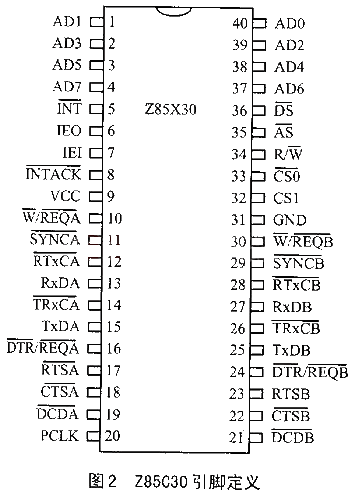

Z85C30引脚按功能分为7组:数据地址总线、总线时序和复位、控制引脚、中断控制、串行数据、通道控制引脚和时钟引脚,如图1所示。Z85C30引脚定义如图2所示。

D7~D0:数据地址总线,用于传送命令和数据。

RD、WR:读、写信号,用于对Z85C30的寄存器操作,低电平有效。

CE:片选信号。

A/B:A、B通道选择,低电平表示选择B通道,高电平选择A通道。

D/C:数据/控制选择,高电平表示与85C30之间传输的是数据,低电平表示与85C30间传输的是命令信号。

INT:中断请求,低电平有效,当SCC需要申请中断时,该信号有效。

INTACK:中断响应,低电平有效。

IEI:中断允许输入。输入,高电平有效。当有多个中断源时,IEI和IEO一起组成中断顺序链优先级排队电路。

IEO:中断允许输出。输出,高电平有效。

PCLK:时钟输入,用来同步内部信号,是标准的TTL电平信号。

TxD、RxD:发送、接收数据,分A、B两个通道。

TRxC、RTxC:通道时钟,它们能被编程为几种不同的操作械。RTxC能提供接收时钟或传送时钟(在输入方式),能提供传输时钟计数器输出(数据锁相器)、晶体振荡器输出、波特率发生器输出和输入时钟输出(它们都是在输出方式)。RTxC能提供接收时钟、传送时钟、波特率发生器时钟、数字锁相环时钟。

1.3 Z85C30的接口时序

1.2 Z85C30主要引脚简介

Z85C30引脚按功能分为7组:数据地址总线、总线时序和复位、控制引脚、中断控制、串行数据、通道控制引脚和时钟引脚,如图1所示。Z85C30引脚定义如图2所示。

D7~D0:数据地址总线,用于传送命令和数据。

RD、WR:读、写信号,用于对Z85C30的寄存器操作,低电平有效。

CE:片选信号。

A/B:A、B通道选择,低电平表示选择B通道,高电平选择A通道。

D/C:数据/控制选择,高电平表示与85C30之间传输的是数据,低电平表示与85C30间传输的是命令信号。

INT:中断请求,低电平有效,当SCC需要申请中断时,该信号有效。

INTACK:中断响应,低电平有效。

IEI:中断允许输入。输入,高电平有效。当有多个中断源时,IEI和IEO一起组成中断顺序链优先级排队电路。

IEO:中断允许输出。输出,高电平有效。

PCLK:时钟输入,用来同步内部信号,是标准的TTL电平信号。

TxD、RxD:发送、接收数据,分A、B两个通道。

TRxC、RTxC:通道时钟,它们能被编程为几种不同的操作械。RTxC能提供接收时钟或传送时钟(在输入方式),能提供传输时钟计数器输出(数据锁相器)、晶体振荡器输出、波特率发生器输出和输入时钟输出(它们都是在输出方式)。RTxC能提供接收时钟、传送时钟、波特率发生器时钟、数字锁相环时钟。

1.3 Z85C30的接口时序

RD和WR是总线传输的两个控制信号。CE、D/C、A/B和INTACK用于控制总线传输的类型。总线上传输的地址在有效后,RD和WR才变低。CE、WR和CE、RD锁存地址的时序是一致的。

(1)读周期时序

在RD和CE有效时,A/B和D/C上的地址被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。Z85X30的总线驱动设备只有在RD和CE都有效地才使能。在读操作用D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完成后,指针复位到0。

(2)写周期时序

在CE和WR有效时,A/B、D/C和数据D7~D0同时被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。在写操作且D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完毕后,指针复位到0。

(3)中断响应周期

当INTACK为低时,进入中断响应周期。这个A/B、D/C、CE、WR信号都被忽略。

1.4 Z85X30寄存器访问

访问寄存器有两个步骤,是使用寄存器指针来完成寻址的。为寻址一个指定的寄存器,先通过写入WR0的指针位来指定寄存器。因为Z85X30只有唯一的寄存器设置存在,因此,可以从两个通道中的任意一个将指针写入。当指针写入后,再次的读或写周期(当D/C为低时)将存取刚才指定的寄存器。在读和写周期结束时,指针被复位到0。

对RR8(接收数据缓冲FIFO)的读及对WR8(传送数据缓冲FIFO)的写操作,可以按以上方法进行,也可以在D/C为高时进行存取。当D/C为高时,可以直接对相应的数据寄存器进行存取,并且指针的状态为独立的。这样,允许在一个周期内寻址数据寄存器,并且不影响指针的状态。

2 Z85C30与CPU的接口

以下介绍以8051作CPU与Z85C30的接口电路,如图3所示。

Z85C30的时钟选用7.0728MHz。54LS373用来锁存片选信号和Z85C30的地址(用来区分命令、数据寄存器)。因为Z85C30的写时序在数据有效后,才应出现WR的下降沿;在数据无效之前,应出现WR上升沿。用1片D触发器54LS74和2个反相器件来延迟送到Z85C30的WR。由于电路设计为TTL电路,在实际的应用,还需加入TTL-RS232转换电路芯片。

3 软件设计

3.1 Z85Z30的I/O操作

X85C30有三种基本的I/O操作形式:查询、中断、块操作。这三种I/O操作在初始化和数据传送时涉及到寄存器操作。

查询方式依靠软件查询串行控制器,从而决定什么时候数据应从串行控制器输入或输出。在此模式中,主中断使能位和WAIT/DMA请求位都应编程为0,从而清除任何中断或DMA请求。查询是通过对RR0的状态检测进行的。在此模式中,中断功能失效。在转入数据处理前,必须对RR0读分析,以决定进入怎样的例程。

中断方式中,串行控制器的每一个通道包括三个中断源:接收器中断、发送器中断和外部/状态中断。

块操作方式可将W/REQ输出与WR1中的就绪/请求位配合。通过编程,W/REQ输出在块操作方式中能被定义为WAIT信号,在DMA方式中可作为REQ信号。

3.2 软件的编写

不同的应用场合,对Z85C30的初始化流程不同,这就需要对Z85C30的写寄存器赋予相应的初值。

图3 8051与Z85C30的接口电路

在SCC初始化完成后,即可进行通信。传送缓冲区和接收缓冲区全部为空。软件把第1个传送字符写到传送缓冲器,中断才会产生。第1个传送字符到了SCC的移位寄存器,传送中断产生。然后,SCC继续判断中断,直到报文结束。报文结束时,应执行复位发送中断赋值命令,用来禁止发送请求中断。SCC检测到最后一个字符,中断将停止,直到另外的报文写到传送缓冲器。

寄存器RR2用来说明中断矢量和状态,它从B信道读取。RR3是中断赋值寄存器,用来指示中断的类型,它从A信道读取。看网络补充版(www.dpj.com.cn)中列出了Z85C30的中断流程。

外部/状态中断源包括:断点/异常中断、发送欠载/报文结束中断、CTS中断、同步/搜索中断、DCD中断、零计数中断。它由WR1和WR15设置,只有WR1中外部/状态中断允许位置和WR15中的相应控制位置位后,外部/状态条件才会产生中断。

结语

采用该设计方案,能够满足不同通信格式的要求,软件编程可根据实际情况选用查询方式、中断方式、DMA传送方式,如需要可以加MODEM控制方式。由于Z85C30功能强大,在许多嵌入式系统、网络设计方面,选用Z85C30作为通信控制器进行开发,完全能够实现其预期的功能。

RD和WR是总线传输的两个控制信号。CE、D/C、A/B和INTACK用于控制总线传输的类型。总线上传输的地址在有效后,RD和WR才变低。CE、WR和CE、RD锁存地址的时序是一致的。

(1)读周期时序

在RD和CE有效时,A/B和D/C上的地址被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。Z85X30的总线驱动设备只有在RD和CE都有效地才使能。在读操作用D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完成后,指针复位到0。

(2)写周期时序

在CE和WR有效时,A/B、D/C和数据D7~D0同时被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。在写操作且D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完毕后,指针复位到0。

(3)中断响应周期

当INTACK为低时,进入中断响应周期。这个A/B、D/C、CE、WR信号都被忽略。

1.4 Z85X30寄存器访问

访问寄存器有两个步骤,是使用寄存器指针来完成寻址的。为寻址一个指定的寄存器,先通过写入WR0的指针位来指定寄存器。因为Z85X30只有唯一的寄存器设置存在,因此,可以从两个通道中的任意一个将指针写入。当指针写入后,再次的读或写周期(当D/C为低时)将存取刚才指定的寄存器。在读和写周期结束时,指针被复位到0。

对RR8(接收数据缓冲FIFO)的读及对WR8(传送数据缓冲FIFO)的写操作,可以按以上方法进行,也可以在D/C为高时进行存取。当D/C为高时,可以直接对相应的数据寄存器进行存取,并且指针的状态为独立的。这样,允许在一个周期内寻址数据寄存器,并且不影响指针的状态。

2 Z85C30与CPU的接口

以下介绍以8051作CPU与Z85C30的接口电路,如图3所示。

Z85C30的时钟选用7.0728MHz。54LS373用来锁存片选信号和Z85C30的地址(用来区分命令、数据寄存器)。因为Z85C30的写时序在数据有效后,才应出现WR的下降沿;在数据无效之前,应出现WR上升沿。用1片D触发器54LS74和2个反相器件来延迟送到Z85C30的WR。由于电路设计为TTL电路,在实际的应用,还需加入TTL-RS232转换电路芯片。

3 软件设计

3.1 Z85Z30的I/O操作

X85C30有三种基本的I/O操作形式:查询、中断、块操作。这三种I/O操作在初始化和数据传送时涉及到寄存器操作。

查询方式依靠软件查询串行控制器,从而决定什么时候数据应从串行控制器输入或输出。在此模式中,主中断使能位和WAIT/DMA请求位都应编程为0,从而清除任何中断或DMA请求。查询是通过对RR0的状态检测进行的。在此模式中,中断功能失效。在转入数据处理前,必须对RR0读分析,以决定进入怎样的例程。

中断方式中,串行控制器的每一个通道包括三个中断源:接收器中断、发送器中断和外部/状态中断。

块操作方式可将W/REQ输出与WR1中的就绪/请求位配合。通过编程,W/REQ输出在块操作方式中能被定义为WAIT信号,在DMA方式中可作为REQ信号。

3.2 软件的编写

不同的应用场合,对Z85C30的初始化流程不同,这就需要对Z85C30的写寄存器赋予相应的初值。

图3 8051与Z85C30的接口电路

在SCC初始化完成后,即可进行通信。传送缓冲区和接收缓冲区全部为空。软件把第1个传送字符写到传送缓冲器,中断才会产生。第1个传送字符到了SCC的移位寄存器,传送中断产生。然后,SCC继续判断中断,直到报文结束。报文结束时,应执行复位发送中断赋值命令,用来禁止发送请求中断。SCC检测到最后一个字符,中断将停止,直到另外的报文写到传送缓冲器。

寄存器RR2用来说明中断矢量和状态,它从B信道读取。RR3是中断赋值寄存器,用来指示中断的类型,它从A信道读取。看网络补充版(www.dpj.com.cn)中列出了Z85C30的中断流程。

外部/状态中断源包括:断点/异常中断、发送欠载/报文结束中断、CTS中断、同步/搜索中断、DCD中断、零计数中断。它由WR1和WR15设置,只有WR1中外部/状态中断允许位置和WR15中的相应控制位置位后,外部/状态条件才会产生中断。

结语

采用该设计方案,能够满足不同通信格式的要求,软件编程可根据实际情况选用查询方式、中断方式、DMA传送方式,如需要可以加MODEM控制方式。由于Z85C30功能强大,在许多嵌入式系统、网络设计方面,选用Z85C30作为通信控制器进行开发,完全能够实现其预期的功能。

引用地址:基于Z85C30的多协议串行通信设计

1.2 Z85C30主要引脚简介

Z85C30引脚按功能分为7组:数据地址总线、总线时序和复位、控制引脚、中断控制、串行数据、通道控制引脚和时钟引脚,如图1所示。Z85C30引脚定义如图2所示。

D7~D0:数据地址总线,用于传送命令和数据。

RD、WR:读、写信号,用于对Z85C30的寄存器操作,低电平有效。

CE:片选信号。

A/B:A、B通道选择,低电平表示选择B通道,高电平选择A通道。

D/C:数据/控制选择,高电平表示与85C30之间传输的是数据,低电平表示与85C30间传输的是命令信号。

INT:中断请求,低电平有效,当SCC需要申请中断时,该信号有效。

INTACK:中断响应,低电平有效。

IEI:中断允许输入。输入,高电平有效。当有多个中断源时,IEI和IEO一起组成中断顺序链优先级排队电路。

IEO:中断允许输出。输出,高电平有效。

PCLK:时钟输入,用来同步内部信号,是标准的TTL电平信号。

TxD、RxD:发送、接收数据,分A、B两个通道。

TRxC、RTxC:通道时钟,它们能被编程为几种不同的操作械。RTxC能提供接收时钟或传送时钟(在输入方式),能提供传输时钟计数器输出(数据锁相器)、晶体振荡器输出、波特率发生器输出和输入时钟输出(它们都是在输出方式)。RTxC能提供接收时钟、传送时钟、波特率发生器时钟、数字锁相环时钟。

1.3 Z85C30的接口时序

1.2 Z85C30主要引脚简介

Z85C30引脚按功能分为7组:数据地址总线、总线时序和复位、控制引脚、中断控制、串行数据、通道控制引脚和时钟引脚,如图1所示。Z85C30引脚定义如图2所示。

D7~D0:数据地址总线,用于传送命令和数据。

RD、WR:读、写信号,用于对Z85C30的寄存器操作,低电平有效。

CE:片选信号。

A/B:A、B通道选择,低电平表示选择B通道,高电平选择A通道。

D/C:数据/控制选择,高电平表示与85C30之间传输的是数据,低电平表示与85C30间传输的是命令信号。

INT:中断请求,低电平有效,当SCC需要申请中断时,该信号有效。

INTACK:中断响应,低电平有效。

IEI:中断允许输入。输入,高电平有效。当有多个中断源时,IEI和IEO一起组成中断顺序链优先级排队电路。

IEO:中断允许输出。输出,高电平有效。

PCLK:时钟输入,用来同步内部信号,是标准的TTL电平信号。

TxD、RxD:发送、接收数据,分A、B两个通道。

TRxC、RTxC:通道时钟,它们能被编程为几种不同的操作械。RTxC能提供接收时钟或传送时钟(在输入方式),能提供传输时钟计数器输出(数据锁相器)、晶体振荡器输出、波特率发生器输出和输入时钟输出(它们都是在输出方式)。RTxC能提供接收时钟、传送时钟、波特率发生器时钟、数字锁相环时钟。

1.3 Z85C30的接口时序

RD和WR是总线传输的两个控制信号。CE、D/C、A/B和INTACK用于控制总线传输的类型。总线上传输的地址在有效后,RD和WR才变低。CE、WR和CE、RD锁存地址的时序是一致的。

(1)读周期时序

在RD和CE有效时,A/B和D/C上的地址被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。Z85X30的总线驱动设备只有在RD和CE都有效地才使能。在读操作用D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完成后,指针复位到0。

(2)写周期时序

在CE和WR有效时,A/B、D/C和数据D7~D0同时被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。在写操作且D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完毕后,指针复位到0。

(3)中断响应周期

当INTACK为低时,进入中断响应周期。这个A/B、D/C、CE、WR信号都被忽略。

1.4 Z85X30寄存器访问

访问寄存器有两个步骤,是使用寄存器指针来完成寻址的。为寻址一个指定的寄存器,先通过写入WR0的指针位来指定寄存器。因为Z85X30只有唯一的寄存器设置存在,因此,可以从两个通道中的任意一个将指针写入。当指针写入后,再次的读或写周期(当D/C为低时)将存取刚才指定的寄存器。在读和写周期结束时,指针被复位到0。

对RR8(接收数据缓冲FIFO)的读及对WR8(传送数据缓冲FIFO)的写操作,可以按以上方法进行,也可以在D/C为高时进行存取。当D/C为高时,可以直接对相应的数据寄存器进行存取,并且指针的状态为独立的。这样,允许在一个周期内寻址数据寄存器,并且不影响指针的状态。

2 Z85C30与CPU的接口

以下介绍以8051作CPU与Z85C30的接口电路,如图3所示。

Z85C30的时钟选用7.0728MHz。54LS373用来锁存片选信号和Z85C30的地址(用来区分命令、数据寄存器)。因为Z85C30的写时序在数据有效后,才应出现WR的下降沿;在数据无效之前,应出现WR上升沿。用1片D触发器54LS74和2个反相器件来延迟送到Z85C30的WR。由于电路设计为TTL电路,在实际的应用,还需加入TTL-RS232转换电路芯片。

3 软件设计

3.1 Z85Z30的I/O操作

X85C30有三种基本的I/O操作形式:查询、中断、块操作。这三种I/O操作在初始化和数据传送时涉及到寄存器操作。

查询方式依靠软件查询串行控制器,从而决定什么时候数据应从串行控制器输入或输出。在此模式中,主中断使能位和WAIT/DMA请求位都应编程为0,从而清除任何中断或DMA请求。查询是通过对RR0的状态检测进行的。在此模式中,中断功能失效。在转入数据处理前,必须对RR0读分析,以决定进入怎样的例程。

中断方式中,串行控制器的每一个通道包括三个中断源:接收器中断、发送器中断和外部/状态中断。

块操作方式可将W/REQ输出与WR1中的就绪/请求位配合。通过编程,W/REQ输出在块操作方式中能被定义为WAIT信号,在DMA方式中可作为REQ信号。

3.2 软件的编写

不同的应用场合,对Z85C30的初始化流程不同,这就需要对Z85C30的写寄存器赋予相应的初值。

图3 8051与Z85C30的接口电路

在SCC初始化完成后,即可进行通信。传送缓冲区和接收缓冲区全部为空。软件把第1个传送字符写到传送缓冲器,中断才会产生。第1个传送字符到了SCC的移位寄存器,传送中断产生。然后,SCC继续判断中断,直到报文结束。报文结束时,应执行复位发送中断赋值命令,用来禁止发送请求中断。SCC检测到最后一个字符,中断将停止,直到另外的报文写到传送缓冲器。

寄存器RR2用来说明中断矢量和状态,它从B信道读取。RR3是中断赋值寄存器,用来指示中断的类型,它从A信道读取。看网络补充版(www.dpj.com.cn)中列出了Z85C30的中断流程。

外部/状态中断源包括:断点/异常中断、发送欠载/报文结束中断、CTS中断、同步/搜索中断、DCD中断、零计数中断。它由WR1和WR15设置,只有WR1中外部/状态中断允许位置和WR15中的相应控制位置位后,外部/状态条件才会产生中断。

结语

采用该设计方案,能够满足不同通信格式的要求,软件编程可根据实际情况选用查询方式、中断方式、DMA传送方式,如需要可以加MODEM控制方式。由于Z85C30功能强大,在许多嵌入式系统、网络设计方面,选用Z85C30作为通信控制器进行开发,完全能够实现其预期的功能。

RD和WR是总线传输的两个控制信号。CE、D/C、A/B和INTACK用于控制总线传输的类型。总线上传输的地址在有效后,RD和WR才变低。CE、WR和CE、RD锁存地址的时序是一致的。

(1)读周期时序

在RD和CE有效时,A/B和D/C上的地址被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。Z85X30的总线驱动设备只有在RD和CE都有效地才使能。在读操作用D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完成后,指针复位到0。

(2)写周期时序

在CE和WR有效时,A/B、D/C和数据D7~D0同时被锁存。在此周期内CE必须保持低,并且INTACK必须保持高。在写操作且D/C为高时,不会影响指针的状态。当D/C为低且在内部操作完毕后,指针复位到0。

(3)中断响应周期

当INTACK为低时,进入中断响应周期。这个A/B、D/C、CE、WR信号都被忽略。

1.4 Z85X30寄存器访问

访问寄存器有两个步骤,是使用寄存器指针来完成寻址的。为寻址一个指定的寄存器,先通过写入WR0的指针位来指定寄存器。因为Z85X30只有唯一的寄存器设置存在,因此,可以从两个通道中的任意一个将指针写入。当指针写入后,再次的读或写周期(当D/C为低时)将存取刚才指定的寄存器。在读和写周期结束时,指针被复位到0。

对RR8(接收数据缓冲FIFO)的读及对WR8(传送数据缓冲FIFO)的写操作,可以按以上方法进行,也可以在D/C为高时进行存取。当D/C为高时,可以直接对相应的数据寄存器进行存取,并且指针的状态为独立的。这样,允许在一个周期内寻址数据寄存器,并且不影响指针的状态。

2 Z85C30与CPU的接口

以下介绍以8051作CPU与Z85C30的接口电路,如图3所示。

Z85C30的时钟选用7.0728MHz。54LS373用来锁存片选信号和Z85C30的地址(用来区分命令、数据寄存器)。因为Z85C30的写时序在数据有效后,才应出现WR的下降沿;在数据无效之前,应出现WR上升沿。用1片D触发器54LS74和2个反相器件来延迟送到Z85C30的WR。由于电路设计为TTL电路,在实际的应用,还需加入TTL-RS232转换电路芯片。

3 软件设计

3.1 Z85Z30的I/O操作

X85C30有三种基本的I/O操作形式:查询、中断、块操作。这三种I/O操作在初始化和数据传送时涉及到寄存器操作。

查询方式依靠软件查询串行控制器,从而决定什么时候数据应从串行控制器输入或输出。在此模式中,主中断使能位和WAIT/DMA请求位都应编程为0,从而清除任何中断或DMA请求。查询是通过对RR0的状态检测进行的。在此模式中,中断功能失效。在转入数据处理前,必须对RR0读分析,以决定进入怎样的例程。

中断方式中,串行控制器的每一个通道包括三个中断源:接收器中断、发送器中断和外部/状态中断。

块操作方式可将W/REQ输出与WR1中的就绪/请求位配合。通过编程,W/REQ输出在块操作方式中能被定义为WAIT信号,在DMA方式中可作为REQ信号。

3.2 软件的编写

不同的应用场合,对Z85C30的初始化流程不同,这就需要对Z85C30的写寄存器赋予相应的初值。

图3 8051与Z85C30的接口电路

在SCC初始化完成后,即可进行通信。传送缓冲区和接收缓冲区全部为空。软件把第1个传送字符写到传送缓冲器,中断才会产生。第1个传送字符到了SCC的移位寄存器,传送中断产生。然后,SCC继续判断中断,直到报文结束。报文结束时,应执行复位发送中断赋值命令,用来禁止发送请求中断。SCC检测到最后一个字符,中断将停止,直到另外的报文写到传送缓冲器。

寄存器RR2用来说明中断矢量和状态,它从B信道读取。RR3是中断赋值寄存器,用来指示中断的类型,它从A信道读取。看网络补充版(www.dpj.com.cn)中列出了Z85C30的中断流程。

外部/状态中断源包括:断点/异常中断、发送欠载/报文结束中断、CTS中断、同步/搜索中断、DCD中断、零计数中断。它由WR1和WR15设置,只有WR1中外部/状态中断允许位置和WR15中的相应控制位置位后,外部/状态条件才会产生中断。

结语

采用该设计方案,能够满足不同通信格式的要求,软件编程可根据实际情况选用查询方式、中断方式、DMA传送方式,如需要可以加MODEM控制方式。由于Z85C30功能强大,在许多嵌入式系统、网络设计方面,选用Z85C30作为通信控制器进行开发,完全能够实现其预期的功能。

上一篇:IEEE1394视频视觉系统中DSP控制处理器的软硬件设计

下一篇:USB连接技术在测量和控制中的应用

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TC52N4340ECTRT

TC52N4340ECTRT

京公网安备 11010802033920号

京公网安备 11010802033920号