[b]引言

[/b]

在小规模图形液晶显示模块上使用液晶显示驱动控制器组成液晶显示驱动和控制系统,是当今低成本,低功耗,高集成化设计的最好选择,SED1520是当前最常用的一种液晶显示驱动控制器,这类图形液晶显示模块的规模为32行,本文用到的液晶模块CM12232即是内置SED1520的液晶显示模块,该模块的驱动控制系统由两片SED1520组成。

FPGA即现场可编程门阵列器件,这是一种超大规模集成电路,具有在电路可重配置的能力(in circuit reconfigurable,ICR)。设计者设计的逻辑可在编译、适配后变成网络表下载到FPGA芯片上之后,FPGA即可执行设计的逻辑功能。因此,FPGA在芯片控制、接口逻辑设计等各个方面的应用越来越广泛。

系统硬件设计

本方案采用的FPGA为Alter公司的ACEX1K30芯片,它可提供系统的时钟及读写控制,ACEX系列的FPGA由逻辑阵列块LAB(Logic array block)、嵌入式阵列块EAB(embedded array block)、快速互联以及IO单元构成,每个逻辑阵列块包含8个逻辑单元LE(logic element)和一个局部互联[1]。每个逻辑单元则由一个4输入查找表(LUT)、一个可编程触发器、快速进位链、级连链组成,多个LAB和多个EAB则可通过快速通道互相连接。EAB是ACEX系列器件在结构设计上的一个重要部件,他是输入端口和输出端口都带有触发器的一种灵活的RAM块,其主要功能是实现一些规模不太大的FIFO、ROM、RAM和双端口RAM等。在本液晶显示接口电路中,EAB主要用宏功能模块实现片上ROM。它通过调用FPGA上的EAB资源来实现汉字的显示和字符的存储,并根据控制信号产生的地址值从ROM中读取字符值,然后送LCD显示器进行显示。

由于所用的图形点阵液晶块内置有SED1520控制器,所以,其电路特性实际上就是SED1520的电路特性。SED1520的主要特性如下[2]:

具有液晶显示行驱动器,具有16路行驱动输出,并可级联实现32行驱动。

具有液晶显示列驱动器,共有61路列驱动输出。

内置时序发生器,其占空比可设置为1/16和1/32两种。

内藏显示存储器,显示存储器内的数据可直接显示,"1"为显示,"0"为不显示。

接口总线时序可适配8080系列或M6800系列,并可直接与计算机接口。

操作简单,有13条控制指令。

采用CMOS工艺,可在电压低至2.4-7.0V时正常工作,功耗仅30μW。

本设计所用的字符液晶模块CM12232由两块SED1520级连驱动,其中一个工作在主工作方式下,另一个工作在从方式下,主工作方式SED1520负责上半屏16行的驱动和左半屏的61列驱动,从工作方式的SED1520则负责下半屏16行的驱动和右半屏的61列驱动,使能信号E1、E2用来区分具体控制的是那一片SED1520,其系统的硬件连接图如图1所示。

由图1可见,该系统的硬件部分连接十分简单,其中FPGA部分没画出,而液晶与FPGA的接口则可直接以网表的形式给出,将它们直接与FPGA的普通I/O引脚相连即可。

[b]系统的软件接口实现

[/b]

具体实现的重点是如何从存放有字符的ROM块中读出数据,并按照液晶的时序正确的写入,在介绍具体实现方法前,首先要熟悉SED1520的指令。

SED1520的控制指令表

SED1520的几种主要的控制指令格式如下:

(1)复位格式(Reset)

SED1520的几种主要的控制指令格式如下:

(1)复位格式(Reset)

该指令用于实现SED1520的软件复位。该指令执行时,显示起始行寄存器清零,接着列地址指针清零,之后页地址寄存器置为"3"。

(2)休闲状态设置(Statis drive ON/OFF)

该指令用于实现SED1520的软件复位。该指令执行时,显示起始行寄存器清零,接着列地址指针清零,之后页地址寄存器置为"3"。

(2)休闲状态设置(Statis drive ON/OFF)

该指令是休闲状态的软件开关,当S=1时,SED1520进入休闲状态;当S=0时,SED1520将中止或退出休闲状态。

(3)占空比设置(Slect duty)

该指令是休闲状态的软件开关,当S=1时,SED1520进入休闲状态;当S=0时,SED1520将中止或退出休闲状态。

(3)占空比设置(Slect duty)

该指令用于设置SED1520的占空比,Du=0时为1/16占空比,Du为1时为1/32占空比。

(4)ADC选择指令(Selet ADC)

该指令用于设置SED1520的占空比,Du=0时为1/16占空比,Du为1时为1/32占空比。

(4)ADC选择指令(Selet ADC)

该指令用于设置显示存储器中单元的地址所对应的显示驱动输出的顺序。A=0时,顺时针显示;A=1时,逆时针显示。

(5)显示起始行设置(Display start line)

该指令用于设置显示存储器中单元的地址所对应的显示驱动输出的顺序。A=0时,顺时针显示;A=1时,逆时针显示。

(5)显示起始行设置(Display start line)

该指令可用于设置显示屏上第一行(行驱动输出COMO所对应的显示行)所对应的显示存储器的行号,由此行顺序下延可得到对应显示屏上的显示效果,L=0-31(1FH),对应表示显示存储器的第1-32行。

(6)显示开/关设置(Display ON/OFF)

该指令可用于设置显示屏上第一行(行驱动输出COMO所对应的显示行)所对应的显示存储器的行号,由此行顺序下延可得到对应显示屏上的显示效果,L=0-31(1FH),对应表示显示存储器的第1-32行。

(6)显示开/关设置(Display ON/OFF)

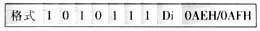

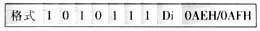

该指令控制着显示驱动器的输出。当Di=0时,显示关,当Di=1时,显示开。

(7)页面显示存储的设置

该指令控制着显示驱动器的输出。当Di=0时,显示关,当Di=1时,显示开。

(7)页面显示存储的设置

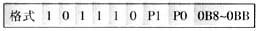

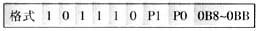

SED1520将显示存储器分为4个页面(0-3页)。每个页面都有80个字节。页面管理可由2位页地址寄存器控制,该指令就是设置页地址寄存器的内容,以选择相应的显示寄存器的页面。P=0-3,对应代表0-3页。

(8)列地址设置(Set column(segment)address)

SED1520将显示存储器分为4个页面(0-3页)。每个页面都有80个字节。页面管理可由2位页地址寄存器控制,该指令就是设置页地址寄存器的内容,以选择相应的显示寄存器的页面。P=0-3,对应代表0-3页。

(8)列地址设置(Set column(segment)address)

SED1520的显示存储器的每个页面上都有80个字节,每个字节中的8位数据对应着显示屏上同一列的8点行,列地址指针就是管理这80个字节单元的,列地址指针是一个7位加一计数器,由它和页地址寄存器组合,可唯一指定显示存储器的某一个单元,列地址指针在计算机对显示存储器的每次操后都将自动加一。该指令就是设置列地址指针内容的。当CY=0-4FH,分别对应于1-80单元的地址。

顶层设计大批量

本设计具体实现的顶层设计原理图如图2所示。

SED1520的显示存储器的每个页面上都有80个字节,每个字节中的8位数据对应着显示屏上同一列的8点行,列地址指针就是管理这80个字节单元的,列地址指针是一个7位加一计数器,由它和页地址寄存器组合,可唯一指定显示存储器的某一个单元,列地址指针在计算机对显示存储器的每次操后都将自动加一。该指令就是设置列地址指针内容的。当CY=0-4FH,分别对应于1-80单元的地址。

顶层设计大批量

本设计具体实现的顶层设计原理图如图2所示。

图2中lpm_rom模块是利用FPGA的宏功能模块产生的片上ROM块[3],用以存放要显示的字符数据。ctrl模块则为控制从ROM中取出数据后液晶上显示的核心控制模块,其功能包括控制数据的读写时序、液晶屏的分屏显示控制、分页显示控制等。

控制模块程序代码

ctrl模块的程序核心代码如下:

architecture Behavioral of ctrl is

signal divcnt:std_logic_vector(11 downto 0);--系数计数

signal data:std_logic_vecdor(9 downto 0);--地址输出

Signal clk1,clk2,a01,cs11,cs21,flag,csflag:std_logic;

data<=divcnt(11 downto 2);--最高10位为地址

process3(clk2)

begin

if clk2'event and clk2=`1'then case conv_integer (data)is

when 0|2|4|6|8|10|12|13|138|139|264|265|390|391=>A01<=`0';cs11<=`0';cs21<=`1';

when 1|3|5|7|9|11|75|76|201|202|327|328|453|454=>A01<=`0';cs11<=`1';cs21<=`0';

when 14 to 74=>A01<=`1';cs11<=`0';cs21<=`1';

when 140 to 200=>A01<=`1';cs11<=`0';cs21<=1';

when 266 to 326=>A01<=`1';cs11<=`0';cs21<=`1';

when 392 to 452=>A01<=`1';cs11<=`0';cs21<=`1';

when 77 to 137=>A01<=`1';cs11<=`1';cs21<=`0';

when 203 to 263=>A01<=`1';cs11>=`1';cs21<=`0';

when 329 to 389=>A01<=`1';cs11<=`1';cs21<=`0';

when 455 to 515=>A01<=`1';cs11<=`1';cs21<=`0';

when others=>A01<=`0';cs11<=`1';cs21<=`1';

end case;

end if;

end process3;

a0<=a01;

cs1<=cs11 or csflag;

cs2<=cs21 or csflag;

ad<=data;

end Behavioral;

其中的关键程序为Process3;在该过程中,A01负责该数据写到液晶数据线上显示还是写到液晶的控制寄存器进行控制,A01为0时为写命令,A01为1时为写数据。

程序中,ROM地址的前13个单元均为写命令,根据SED1520的控制命令字,ROM表中的0、2、4、6、8、10单元依次是E2、A4、A9、A0、C0、AF,主要用于实现对CSI主工作的SED1520复位、退出休闲状态、设置占空比为1/32、顺时针显示数据RAM中的内容、显示起始对应显示存储器的0行、显示开这一系列的初始化工作;而1,3,5,7,9,11单元则写入到CS2(即从工作的SED1520)实现其初始化[4]。第13单元放的是B8(即页地址设置为0),从14-74单元,A01=1为写数据,此时片选CS1有效,ROM表中连续放入"武汉理工"4个汉字的上半部分字模(本方案共显示16个汉字"武汉理工大学自动化学院重点实验室"分两行,每行8个字显示);之后,75、76单元为写命令,ROM中的数据为B8,00表示设置显示页为0页,该页的列地址从0开始[5]。从77-137单元地址向CS2(即从动工作方式的SED1520)写数据即"大学自动"的前半部分字模,接下来的138、139单元为写命令,ROM中的数据为B9,00即表示页地址设置为1列,地址为0,140-200单元放入"武汉理工"的下半部分字模,201、202单元为写命令,ROM中的数据为B9、00表示页地址设置为1列,地址为0,203-263中为"大学自动"的下半部分字模,之后,8个字的写入过程与前8个字的写入过程相同,写命令单元用于控制要写的页。

结束语

本方案以FPGA为控制核心实现了对字符点阵液晶的控制,该方案硬件电路简单,软件程序简洁,对液晶的控制简单而且稳定,且可灵活改动,若要改变液晶显示的汉字,只需改变ROM表中的字模即可,实践证明,该设计是对液晶应用的一种行之有效的方法。

图2中lpm_rom模块是利用FPGA的宏功能模块产生的片上ROM块[3],用以存放要显示的字符数据。ctrl模块则为控制从ROM中取出数据后液晶上显示的核心控制模块,其功能包括控制数据的读写时序、液晶屏的分屏显示控制、分页显示控制等。

控制模块程序代码

ctrl模块的程序核心代码如下:

architecture Behavioral of ctrl is

signal divcnt:std_logic_vector(11 downto 0);--系数计数

signal data:std_logic_vecdor(9 downto 0);--地址输出

Signal clk1,clk2,a01,cs11,cs21,flag,csflag:std_logic;

data<=divcnt(11 downto 2);--最高10位为地址

process3(clk2)

begin

if clk2'event and clk2=`1'then case conv_integer (data)is

when 0|2|4|6|8|10|12|13|138|139|264|265|390|391=>A01<=`0';cs11<=`0';cs21<=`1';

when 1|3|5|7|9|11|75|76|201|202|327|328|453|454=>A01<=`0';cs11<=`1';cs21<=`0';

when 14 to 74=>A01<=`1';cs11<=`0';cs21<=`1';

when 140 to 200=>A01<=`1';cs11<=`0';cs21<=1';

when 266 to 326=>A01<=`1';cs11<=`0';cs21<=`1';

when 392 to 452=>A01<=`1';cs11<=`0';cs21<=`1';

when 77 to 137=>A01<=`1';cs11<=`1';cs21<=`0';

when 203 to 263=>A01<=`1';cs11>=`1';cs21<=`0';

when 329 to 389=>A01<=`1';cs11<=`1';cs21<=`0';

when 455 to 515=>A01<=`1';cs11<=`1';cs21<=`0';

when others=>A01<=`0';cs11<=`1';cs21<=`1';

end case;

end if;

end process3;

a0<=a01;

cs1<=cs11 or csflag;

cs2<=cs21 or csflag;

ad<=data;

end Behavioral;

其中的关键程序为Process3;在该过程中,A01负责该数据写到液晶数据线上显示还是写到液晶的控制寄存器进行控制,A01为0时为写命令,A01为1时为写数据。

程序中,ROM地址的前13个单元均为写命令,根据SED1520的控制命令字,ROM表中的0、2、4、6、8、10单元依次是E2、A4、A9、A0、C0、AF,主要用于实现对CSI主工作的SED1520复位、退出休闲状态、设置占空比为1/32、顺时针显示数据RAM中的内容、显示起始对应显示存储器的0行、显示开这一系列的初始化工作;而1,3,5,7,9,11单元则写入到CS2(即从工作的SED1520)实现其初始化[4]。第13单元放的是B8(即页地址设置为0),从14-74单元,A01=1为写数据,此时片选CS1有效,ROM表中连续放入"武汉理工"4个汉字的上半部分字模(本方案共显示16个汉字"武汉理工大学自动化学院重点实验室"分两行,每行8个字显示);之后,75、76单元为写命令,ROM中的数据为B8,00表示设置显示页为0页,该页的列地址从0开始[5]。从77-137单元地址向CS2(即从动工作方式的SED1520)写数据即"大学自动"的前半部分字模,接下来的138、139单元为写命令,ROM中的数据为B9,00即表示页地址设置为1列,地址为0,140-200单元放入"武汉理工"的下半部分字模,201、202单元为写命令,ROM中的数据为B9、00表示页地址设置为1列,地址为0,203-263中为"大学自动"的下半部分字模,之后,8个字的写入过程与前8个字的写入过程相同,写命令单元用于控制要写的页。

结束语

本方案以FPGA为控制核心实现了对字符点阵液晶的控制,该方案硬件电路简单,软件程序简洁,对液晶的控制简单而且稳定,且可灵活改动,若要改变液晶显示的汉字,只需改变ROM表中的字模即可,实践证明,该设计是对液晶应用的一种行之有效的方法。

引用地址:基于FPGA的液晶显示接口设计

SED1520的几种主要的控制指令格式如下:

(1)复位格式(Reset)

SED1520的几种主要的控制指令格式如下:

(1)复位格式(Reset)

该指令用于实现SED1520的软件复位。该指令执行时,显示起始行寄存器清零,接着列地址指针清零,之后页地址寄存器置为"3"。

(2)休闲状态设置(Statis drive ON/OFF)

该指令用于实现SED1520的软件复位。该指令执行时,显示起始行寄存器清零,接着列地址指针清零,之后页地址寄存器置为"3"。

(2)休闲状态设置(Statis drive ON/OFF)

该指令是休闲状态的软件开关,当S=1时,SED1520进入休闲状态;当S=0时,SED1520将中止或退出休闲状态。

(3)占空比设置(Slect duty)

该指令是休闲状态的软件开关,当S=1时,SED1520进入休闲状态;当S=0时,SED1520将中止或退出休闲状态。

(3)占空比设置(Slect duty)

该指令用于设置SED1520的占空比,Du=0时为1/16占空比,Du为1时为1/32占空比。

(4)ADC选择指令(Selet ADC)

该指令用于设置SED1520的占空比,Du=0时为1/16占空比,Du为1时为1/32占空比。

(4)ADC选择指令(Selet ADC)

该指令用于设置显示存储器中单元的地址所对应的显示驱动输出的顺序。A=0时,顺时针显示;A=1时,逆时针显示。

(5)显示起始行设置(Display start line)

该指令用于设置显示存储器中单元的地址所对应的显示驱动输出的顺序。A=0时,顺时针显示;A=1时,逆时针显示。

(5)显示起始行设置(Display start line)

该指令可用于设置显示屏上第一行(行驱动输出COMO所对应的显示行)所对应的显示存储器的行号,由此行顺序下延可得到对应显示屏上的显示效果,L=0-31(1FH),对应表示显示存储器的第1-32行。

(6)显示开/关设置(Display ON/OFF)

该指令可用于设置显示屏上第一行(行驱动输出COMO所对应的显示行)所对应的显示存储器的行号,由此行顺序下延可得到对应显示屏上的显示效果,L=0-31(1FH),对应表示显示存储器的第1-32行。

(6)显示开/关设置(Display ON/OFF)

该指令控制着显示驱动器的输出。当Di=0时,显示关,当Di=1时,显示开。

(7)页面显示存储的设置

该指令控制着显示驱动器的输出。当Di=0时,显示关,当Di=1时,显示开。

(7)页面显示存储的设置

SED1520将显示存储器分为4个页面(0-3页)。每个页面都有80个字节。页面管理可由2位页地址寄存器控制,该指令就是设置页地址寄存器的内容,以选择相应的显示寄存器的页面。P=0-3,对应代表0-3页。

(8)列地址设置(Set column(segment)address)

SED1520将显示存储器分为4个页面(0-3页)。每个页面都有80个字节。页面管理可由2位页地址寄存器控制,该指令就是设置页地址寄存器的内容,以选择相应的显示寄存器的页面。P=0-3,对应代表0-3页。

(8)列地址设置(Set column(segment)address)

SED1520的显示存储器的每个页面上都有80个字节,每个字节中的8位数据对应着显示屏上同一列的8点行,列地址指针就是管理这80个字节单元的,列地址指针是一个7位加一计数器,由它和页地址寄存器组合,可唯一指定显示存储器的某一个单元,列地址指针在计算机对显示存储器的每次操后都将自动加一。该指令就是设置列地址指针内容的。当CY=0-4FH,分别对应于1-80单元的地址。

顶层设计大批量

本设计具体实现的顶层设计原理图如图2所示。

SED1520的显示存储器的每个页面上都有80个字节,每个字节中的8位数据对应着显示屏上同一列的8点行,列地址指针就是管理这80个字节单元的,列地址指针是一个7位加一计数器,由它和页地址寄存器组合,可唯一指定显示存储器的某一个单元,列地址指针在计算机对显示存储器的每次操后都将自动加一。该指令就是设置列地址指针内容的。当CY=0-4FH,分别对应于1-80单元的地址。

顶层设计大批量

本设计具体实现的顶层设计原理图如图2所示。

图2中lpm_rom模块是利用FPGA的宏功能模块产生的片上ROM块[3],用以存放要显示的字符数据。ctrl模块则为控制从ROM中取出数据后液晶上显示的核心控制模块,其功能包括控制数据的读写时序、液晶屏的分屏显示控制、分页显示控制等。

控制模块程序代码

ctrl模块的程序核心代码如下:

architecture Behavioral of ctrl is

signal divcnt:std_logic_vector(11 downto 0);--系数计数

signal data:std_logic_vecdor(9 downto 0);--地址输出

Signal clk1,clk2,a01,cs11,cs21,flag,csflag:std_logic;

data<=divcnt(11 downto 2);--最高10位为地址

process3(clk2)

begin

if clk2'event and clk2=`1'then case conv_integer (data)is

when 0|2|4|6|8|10|12|13|138|139|264|265|390|391=>A01<=`0';cs11<=`0';cs21<=`1';

when 1|3|5|7|9|11|75|76|201|202|327|328|453|454=>A01<=`0';cs11<=`1';cs21<=`0';

when 14 to 74=>A01<=`1';cs11<=`0';cs21<=`1';

when 140 to 200=>A01<=`1';cs11<=`0';cs21<=1';

when 266 to 326=>A01<=`1';cs11<=`0';cs21<=`1';

when 392 to 452=>A01<=`1';cs11<=`0';cs21<=`1';

when 77 to 137=>A01<=`1';cs11<=`1';cs21<=`0';

when 203 to 263=>A01<=`1';cs11>=`1';cs21<=`0';

when 329 to 389=>A01<=`1';cs11<=`1';cs21<=`0';

when 455 to 515=>A01<=`1';cs11<=`1';cs21<=`0';

when others=>A01<=`0';cs11<=`1';cs21<=`1';

end case;

end if;

end process3;

a0<=a01;

cs1<=cs11 or csflag;

cs2<=cs21 or csflag;

ad<=data;

end Behavioral;

其中的关键程序为Process3;在该过程中,A01负责该数据写到液晶数据线上显示还是写到液晶的控制寄存器进行控制,A01为0时为写命令,A01为1时为写数据。

程序中,ROM地址的前13个单元均为写命令,根据SED1520的控制命令字,ROM表中的0、2、4、6、8、10单元依次是E2、A4、A9、A0、C0、AF,主要用于实现对CSI主工作的SED1520复位、退出休闲状态、设置占空比为1/32、顺时针显示数据RAM中的内容、显示起始对应显示存储器的0行、显示开这一系列的初始化工作;而1,3,5,7,9,11单元则写入到CS2(即从工作的SED1520)实现其初始化[4]。第13单元放的是B8(即页地址设置为0),从14-74单元,A01=1为写数据,此时片选CS1有效,ROM表中连续放入"武汉理工"4个汉字的上半部分字模(本方案共显示16个汉字"武汉理工大学自动化学院重点实验室"分两行,每行8个字显示);之后,75、76单元为写命令,ROM中的数据为B8,00表示设置显示页为0页,该页的列地址从0开始[5]。从77-137单元地址向CS2(即从动工作方式的SED1520)写数据即"大学自动"的前半部分字模,接下来的138、139单元为写命令,ROM中的数据为B9,00即表示页地址设置为1列,地址为0,140-200单元放入"武汉理工"的下半部分字模,201、202单元为写命令,ROM中的数据为B9、00表示页地址设置为1列,地址为0,203-263中为"大学自动"的下半部分字模,之后,8个字的写入过程与前8个字的写入过程相同,写命令单元用于控制要写的页。

结束语

本方案以FPGA为控制核心实现了对字符点阵液晶的控制,该方案硬件电路简单,软件程序简洁,对液晶的控制简单而且稳定,且可灵活改动,若要改变液晶显示的汉字,只需改变ROM表中的字模即可,实践证明,该设计是对液晶应用的一种行之有效的方法。

图2中lpm_rom模块是利用FPGA的宏功能模块产生的片上ROM块[3],用以存放要显示的字符数据。ctrl模块则为控制从ROM中取出数据后液晶上显示的核心控制模块,其功能包括控制数据的读写时序、液晶屏的分屏显示控制、分页显示控制等。

控制模块程序代码

ctrl模块的程序核心代码如下:

architecture Behavioral of ctrl is

signal divcnt:std_logic_vector(11 downto 0);--系数计数

signal data:std_logic_vecdor(9 downto 0);--地址输出

Signal clk1,clk2,a01,cs11,cs21,flag,csflag:std_logic;

data<=divcnt(11 downto 2);--最高10位为地址

process3(clk2)

begin

if clk2'event and clk2=`1'then case conv_integer (data)is

when 0|2|4|6|8|10|12|13|138|139|264|265|390|391=>A01<=`0';cs11<=`0';cs21<=`1';

when 1|3|5|7|9|11|75|76|201|202|327|328|453|454=>A01<=`0';cs11<=`1';cs21<=`0';

when 14 to 74=>A01<=`1';cs11<=`0';cs21<=`1';

when 140 to 200=>A01<=`1';cs11<=`0';cs21<=1';

when 266 to 326=>A01<=`1';cs11<=`0';cs21<=`1';

when 392 to 452=>A01<=`1';cs11<=`0';cs21<=`1';

when 77 to 137=>A01<=`1';cs11<=`1';cs21<=`0';

when 203 to 263=>A01<=`1';cs11>=`1';cs21<=`0';

when 329 to 389=>A01<=`1';cs11<=`1';cs21<=`0';

when 455 to 515=>A01<=`1';cs11<=`1';cs21<=`0';

when others=>A01<=`0';cs11<=`1';cs21<=`1';

end case;

end if;

end process3;

a0<=a01;

cs1<=cs11 or csflag;

cs2<=cs21 or csflag;

ad<=data;

end Behavioral;

其中的关键程序为Process3;在该过程中,A01负责该数据写到液晶数据线上显示还是写到液晶的控制寄存器进行控制,A01为0时为写命令,A01为1时为写数据。

程序中,ROM地址的前13个单元均为写命令,根据SED1520的控制命令字,ROM表中的0、2、4、6、8、10单元依次是E2、A4、A9、A0、C0、AF,主要用于实现对CSI主工作的SED1520复位、退出休闲状态、设置占空比为1/32、顺时针显示数据RAM中的内容、显示起始对应显示存储器的0行、显示开这一系列的初始化工作;而1,3,5,7,9,11单元则写入到CS2(即从工作的SED1520)实现其初始化[4]。第13单元放的是B8(即页地址设置为0),从14-74单元,A01=1为写数据,此时片选CS1有效,ROM表中连续放入"武汉理工"4个汉字的上半部分字模(本方案共显示16个汉字"武汉理工大学自动化学院重点实验室"分两行,每行8个字显示);之后,75、76单元为写命令,ROM中的数据为B8,00表示设置显示页为0页,该页的列地址从0开始[5]。从77-137单元地址向CS2(即从动工作方式的SED1520)写数据即"大学自动"的前半部分字模,接下来的138、139单元为写命令,ROM中的数据为B9,00即表示页地址设置为1列,地址为0,140-200单元放入"武汉理工"的下半部分字模,201、202单元为写命令,ROM中的数据为B9、00表示页地址设置为1列,地址为0,203-263中为"大学自动"的下半部分字模,之后,8个字的写入过程与前8个字的写入过程相同,写命令单元用于控制要写的页。

结束语

本方案以FPGA为控制核心实现了对字符点阵液晶的控制,该方案硬件电路简单,软件程序简洁,对液晶的控制简单而且稳定,且可灵活改动,若要改变液晶显示的汉字,只需改变ROM表中的字模即可,实践证明,该设计是对液晶应用的一种行之有效的方法。

上一篇:基于USB的通用无线传输接口设计

下一篇:一种异步FIFO的设计方法

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新应用文章

更多精选电路图

更多热门文章

更多每日新闻

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

- 村田推出高精度汽车用6轴惯性传感器

- 福特获得预充电报警专利 有助于节约成本和应对紧急情况

更多往期活动

- 4月26日上午10:00邀您观看 基于TI Sitara™AM5708的工业派开源平台介绍 有奖直播

- 4月TI两场EP直播,都挺好:超声气体流量计量创新方案+SimpleLink平台小鲜肉CC13X2/CC26X2专场

- 【EEWORLD第三十四届】2012年01月社区明星人物揭晓!

- 新年新挑战:ST蓝牙开发板免费申请评测+挑战赛(littleshrimp带队)

- 国产FPGA有奖直播:安路全新FPSoC产品SF1系列(FPGA+MCU),Demo板介绍和案例解析

- 恩智浦无线MCU应用征集+100套开发套件申请

- TI 技术大咖带你领略独一无二的MCU世界 推荐、抢楼全有礼!

- 推荐有礼,分享有你!DSP学习季开学了,推荐你最喜欢的TI DSP资料!

- 暑期酷学,专为在校生打造!!!

- 有奖直播:基于TI Jacinto™ 的深度学习平台介绍

11月16日历史上的今天

厂商技术中心

MAX439MJA

MAX439MJA

京公网安备 11010802033920号

京公网安备 11010802033920号