好马配好鞍:第10代&EM1130

系统设计时,创新的基石是什么?很多工程师会说:处理器。确实,即使有再多好的想法,编写最智能的算法,没有好的处理器去承载,也无从做起。而随着系统核心器件,如FPGA、MCU等性能不断增加,其所消耗的功耗越来越大,例如高性能FPFA内核电流动辄几十安培,电压却很低。因此电源管理的重要性被提到了前所未有的高度,其好坏直接关系到复杂、精密的系统能否使用。

从去年开始,Altera一直励志为自己打造第4个十年的好开端,相继发布了3款“第10代”FPGA及SoC产品系列:Arria 10、Stratix 10以及MAX 10。所谓“好马配好鞍”,性能优异的“第10代”器件也需要搭配更好的电源解决方案,以让其能够更好地在系统中运行。在2013年Altera就收购了电源技术创新者Enpirion公司,回头看这个事件,就知道原来这都是在为Altera高性能FPGA及其在高端领域的应用布局。

近日,Altera推出了EM1130,它是负载电流为30 A高度集成的电源模组,也是Enpirion电源解决方案产品的第一款数字PowerSoC DC-DC降压转换器。其适用于Altera的第10代FPGA和SoC——特别是Arria 10和Stratix 10 FPGA内核以及收发器电源轨,是Altera致力于为可编程逻辑市场带来前所未有的最优电源解决方案的重要里程碑。Altera公司全球业务总监Patrick Wadden先生从风雪交加的美国波士顿来到马上要春暖花开的北京,与Altera中国区Enpirion产品高级业务经理张伟超先生一起向记者介绍了EM1130的特别之处。

图1 Altera公司全球业务总监Patrick Wadden先生(左)

与Altera中国区Enpirion产品高级业务经理张伟超先生(右)

满足复杂系统需求:效率、精度、波纹

Wadden先生表示:“FPGA和SoC不断发展,在可编程架构中增加了混合信号功能,实现了以前无法企及的系统级性能。设计人员的挑战包括,能否满足严格的FPGA电源轨需求,满足系统功耗和散热预算的限制,构建鲁棒而又可靠的系统,符合预算要求按时完成项目,满足电路板和系统对功能和性能的要求。EM1139在效率、精度、波纹、尺寸、散热性等方便都满足了系统的需求,甚至超越了需求。”

EM1139的效率高达89%,其转换效率是同类产品中最高的,其效率比其他方案高3%~6%,系统功耗降低了1 W以上。Wadden先生解释到:“效率提高1%相当于节省270 mW的功耗,而如果节省1 W的功耗,一年的运营成本最多将节省30美元。对于大的数据中心而言,一年就可以节省百万美元。”

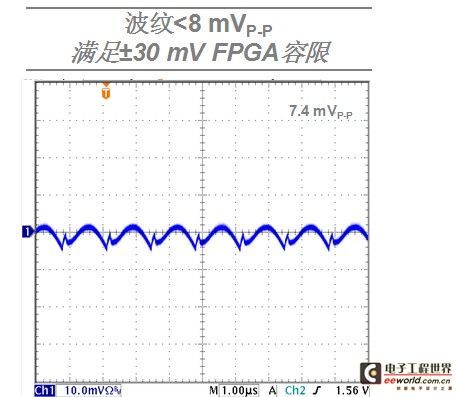

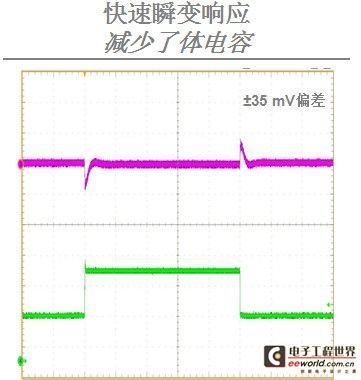

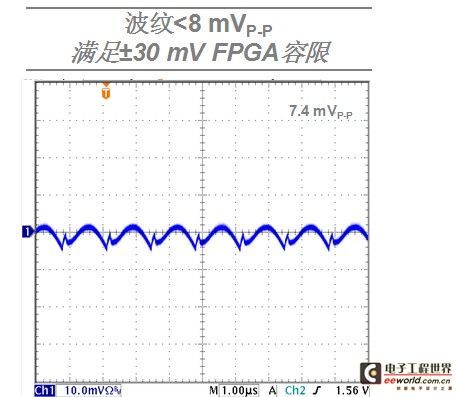

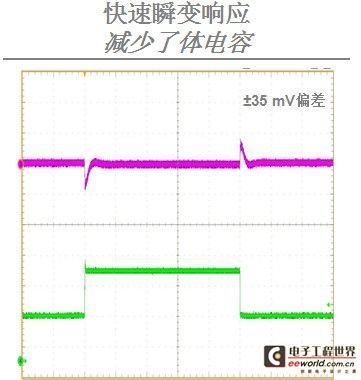

Altera高性能FPGA与竞争对手相比的一个最大优势是高速接口,而高速接口除了对电流有要求,对波纹要求也很高。下一代工艺节点(如20 nm、16 nm)使得内核电压下降到1 V,精度对内存、处理器是很重要的指标。EM1130输出波纹小于8 mVP-P,满足±30 mV FPGA容限,EM1130的输出精度小于0.5%,极低的输出波纹与输出精度相结合,保证了无缝工作, 也正好满足了Arria 10、Stratix 10等高性能FPGA高速接口的需求。此外,EM1130支持快速瞬变响应,去掉了大体积而且昂贵的体电容,偏差在±35 mV,且不会影响FPGA速度。

张伟超先生补充到:“ EM1130有一个均流总线(CSB),其速度高达500 Mb/s,而竞争对手的产品一般只有250 Mb/s,这满足了快速动态响应的需求。”

图2 EM1130的波纹和快速瞬变响应仿真图

下一代系统的天作之合

由于是针对Altera高性能FPGA/SoC器件而设计的,因此在已有的低功耗特性基础上,如果再使用EM1130就会有更加出色的表现。Wadden先生举例到:“Arria 10内部有一个叫做SmartVoltage ID(SmartVID,即最佳工作电压)的标签,当EM1130与Arria 10接通时,会自动读取SmartVID的值,实现最佳核电压供电,精度达0.5%,从而实现更好的低功耗特性。同样的Arria 10,在使用EM1130后,功耗降低40%。而传统的方法是手动设置最佳工作电压。由于工艺、封装、尺寸的不同,不同的Altera FPGA有不同的最佳工作电压,EM1130都能精确自动读取。”

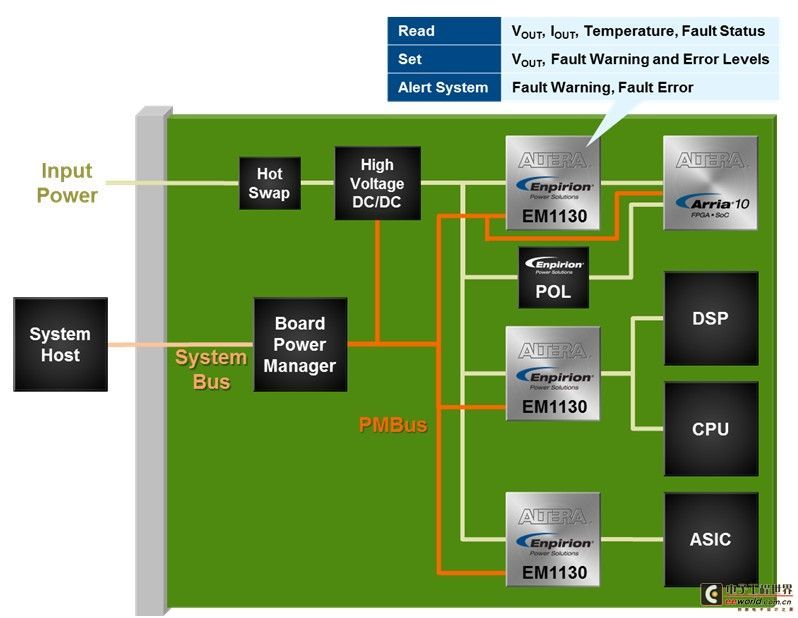

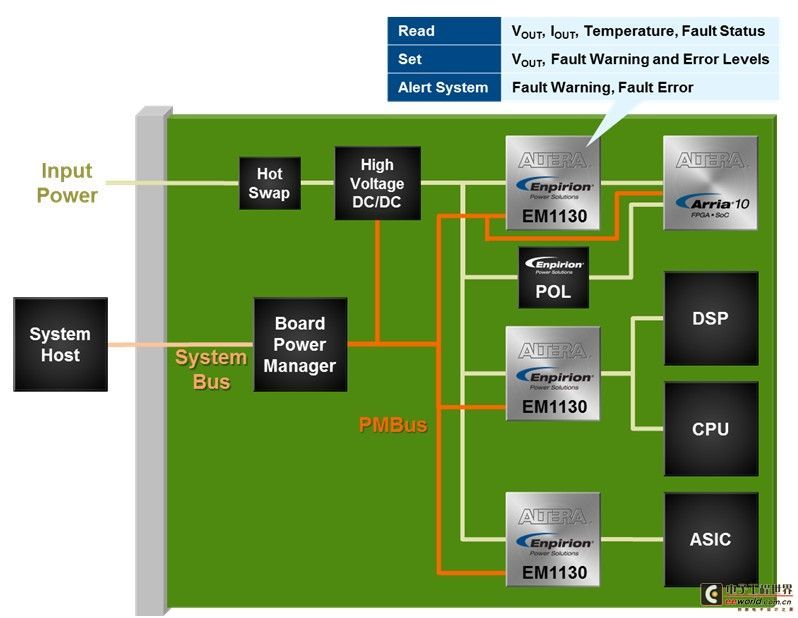

Altera支持智能系统以峰值性能工作。下图是一个典型的智能系统架构图,EM1130能读取输出电压/电流、温度和故障状态,设置输出电压、故障报警和错误水平,提高了系统可靠性,缩短了停机时间。而竞争产品需要加外部组件才能做到。EM1130的远程监测和PMBus兼容接口进一步优化了系统,可实现高精度远程监测,相对于DCR监测提高了4倍。Wadden先生说到:“Altera解决方案简化了系统管理,而精度越高,设计人员的信心也倍增,这也很重要。”

图3 智能系统架构图

灵活的小帮手

EM1130采用Dr MOS技术(驱动+MOSFET),内部有4层,每层都敷了一层铜,以实现很好的散热性。EM1130实现了密度最高的集成引脚布局,面积不到其他解决方案的一半,总面积只有360 mm2 。它是一个完整的解决方案,在系统中使用时,唯一需要的就是一个输入和输出电容,能帮助用户减少40%的板上面积。

EM1130可以在提供可靠性的同时简化设计。其提供了最先进而且使用非常方便的数字可编程和控制功能。其自动数字环路补偿功能弥补了由于模拟器件性能不断下降而带来的影响,不论工作条件怎样变化,都能够提供鲁棒的解决方案。此外,图形用户界面(GUI)简化了测试和配置,支持更快更简单的开发过程。用户几分钟就可以完成EM1130的测试和配置,或者从8个预设的个性化设置中选择一个。

Wadden先生表示EM1130的设计灵活性是难以置信的:“扩展解决方案支持EM1130并行运行,最多可连接6个EM1130,这样最大内核逻辑电流就达到180 A(30 A×6),实现一种解决方案满足多种需求和平台。”

下一代复杂系统用传统模拟器件提供电源将越来越难,极端情况下可能导致系统不能开启,EM1130完全有能力替代之前的器件。Wadden先生透露:“让FPGA系统更好,让FPGA设计过程更简单,让参考设计更易于使用,这三点是Altera推出EM1130的初衷。我们对于计算、存储和通信市场这类高端应用有很高的期望,希望EM1130在这些领域能够被客户大规模采用。即使这些客户的主控制器是MCU或者其他ASIC,也能够享受EM1130带来的高效和低功耗等卓越性能。”

FPGA快速系统原型设计权威指南_(美国)

FPGA快速系统原型设计权威指南_(美国) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号