Mentor, a Siemens Business, 总裁兼CEO Walden C. Rhines近日在中国集成电路设计业2018年会暨珠海集成电路产业创新发展高峰论坛上发表了题为《为何半导体行业内的设计不断加快?》主题演讲。

Mentor, a Siemens Business, 总裁兼CEO Walden C. Rhines

四大方向看半导体设计业加速

Rhines表示,从四大方向来看,半导体产业都在经历着加速:1,在经历了几年3%的年增长率之后,2017年半导体产业年增幅达到了22%的年增长率;2,整合已变得无关紧要;3,2017年研发投入增长9.8%;4,VC们对于IC设计公司投入急剧增加,从几年前的平均不到4亿美元上升至2018年的27亿美元,年投入已超过2000年网络泡沫时期的25亿美元。

IC设计领域新玩家

Rhines强调,此轮的巨大投入,最明显的特征就是众多重量级系统公司进入IC领域,其中包括Facebook、Apple、亚马逊、谷歌、特斯拉、博世等国际巨头,同时也包括华为、小米、ZTE等中国公司。

Rhines援引特斯拉CEO马斯克2018年所宣布的:“我们正在增加我们的芯片设计团队,通过针对自动驾驶系统的定制处理器取代通用GPU,从而使得处理速度提高10倍。”

除了国际系统公司巨头投入之外,中国玩家实力正在显著成长。

中国政府对半导体投资的激励不能小觑,2014年大基金投入了一期200亿美元,同时带动了将近1000亿美元地方政府及各类资本的投入,而今根据5月份华尔街日报报道,3000亿大基金的二期募资也接近完成,能带动的投资效应更是无法估量。

Rhines说道:“中国半导体的崛起加速了新创企业的组建,尤其是从2016年起,中国的IC设计企业数量一下子提升了1倍,变成接近1400家。同样相比10年前,Fabless公司的企业规模也逐步扩大,有接近一半的公司拥有100名以上员工,500名以上员工公司数更是达到了6.1%。”

新的“特定领域”架构是未来增长主浪潮

Rhines分析了从2012到2018年对于芯片领域的风险投资发现,AI&机器学习是投资者最青睐的领域,超过17亿美元,之后是数字货币的4.6亿美元,第三则是5G及通信,约为3.4亿美元。

但是,Rhines表示,人工智能并不是新趋势,早在1986年,HIGH TECHNOLOGY上就刊登了人工智能的封面,左面就是年轻时代的Rhines。

“当时人工智能没有大规模的发展主要有四大原因,1. 没有网络或IoT收集大量数据,从而缺乏大数据分析;2. 当时芯片架构和制程等影响计算芯片性能;3, 算法比较落后;4,缺少杀手级应用领域。”

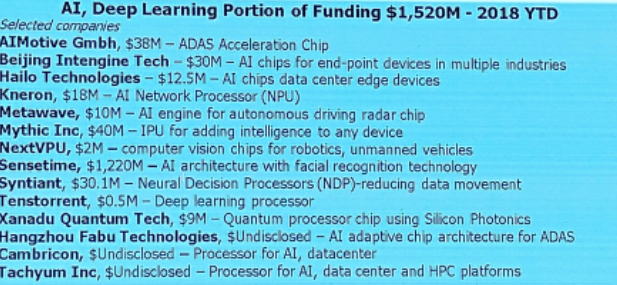

如果再将投资统计细分,2018年共有14家AI公司获得风投。

Rhines同时强调,中国Fabless前期资金量已经明显超越额美国。

针对目前特定领域AI/深度学习控制器来说,图像识别,语音/语意/声音模式识别、自动驾驶/ADAS、数据中心/云AI/HPC、边缘计算、深度学习等领域是如今相对热门的领域。

特定领域体系结构需要新的设计方法学

Rhines强调,AI&机器学习需要更高级的设计抽象和功耗分析,其中最重要的原因就是因为随着AI芯片设计复杂度越来越高,但与此同时企业产品的上市时间又要不断被压缩,同时也需要随时调整芯片spec,因此给与验证和Debug的时间及成本越来越少,就需要越来越快的工具。

高级综合(HLS)方法现如今被证实为是相比VHDL或Verilog更具效率的工具实践表明,HLS的结果不比手动编写的RTL差,甚至更强,同时能平均缩短4倍时间。Rhines强调,HLS非常容易重映射到多种技术,同样的C语言既可用于FPGA,同时也可用于28nm、16nm等不同制程的ASIC芯片。

Walden Rhines以NVIDIA TegraX1中的千万级门规模视频编码器为例,通过采用HLS将验证成本降低了80%,效率提升了50%。以前传统RTL需要3个月/1000 CPU,通过使用HLS C++只需要2星期/14 CPU。此外,将VP9/H.265编码器从8bit color提升到10bit color只需要数周,从20nm/500MHz到28nm/800MHz的IP重优化更是缩短到了3天。

机器学习加速IC设计验证

Rhines表示,除了引入HLS概念,实际上,EDA公司早已将机器学习技术融入到软件工具中,从而提高设计验证效率。

传统的机器学习加速模型是采用手动筛除数据的方式进行,但实现效率非常差,而通过循环中具有数据采集功能的自适应机器学习,具有自动验证功能并将其结果返还至数据筛除步骤,以此往复,可以极大加速效率,尤其是对于新工艺或新芯片等缺乏足够数据量的时候。

同时,利用大数据的仿真和验证也是芯片设计加速的重要原因,以前没有数据参数提取,没办法进行测试。而现如今,通过对天气,行人,路况等路况数据的提取,以及针对摄像头、雷达、LiDAR、超声波、GPS等传感器模型库的建立,使得基于数据的虚拟测试成为可能,这样芯片的验证就不再需要大量的实测而是仅仅通过计算机仿真即可。

通过包括VECTOR、dSPACE、TASS、MATLAB、以及Mentor的Catapult、Vista Virtual Prototyping等系统框架的集成系统模拟仿真和验证,可以加速车用ECU的电气性能和机器性能的验证过程。

半导体市场成熟了吗?

芯片业如今的快速成长,是否意味着即将到达了顶点呢?Rhines表示,完全不需要对此担忧。

Rhines介绍了姜氏曲线概念,又名戈珀兹(Gompertz)曲线,当经济变量的发展变化表现为初期增长速度缓慢,随后增长速度逐渐加,达到一定程度后又逐渐减慢,最后达到饱和状态这种趋势时,可以用姜氏曲线来描述,它适用于商品寿命周期中市场容量或普及率的预测。

实际上目前手机增长趋缓正是完全符合姜氏曲线的特点。

但是对于晶体管来说,如今还处于增长速度缓慢的初期,而根据曲线拟合,大约2040年之前,之后晶体管增长率会下降,替代品则会出现。

正是因此,Rhines给出了IC设计正在迅速增加的总结。2017年半导体收入增长突然加速,随着2018年、2019年存储器市场下行,非存储器市场的增长将变得活跃,这主要原因是由于:1.引入“特定域处理器”;2.IC设计业有新参与者;3.初创企业活动的加速;4.中国对半导体的投资。特定域架构和学习曲线将实现下一波增长,带来低功耗、高性能、低成本,同时减少设计时间和设计成本。

上一篇:Mentor CEO:在西门子的协助下,Mentor可以更多支持中国2025

下一篇:华为致全球供应商的一封信:无惧美国制裁

推荐阅读最新更新时间:2023-10-13 10:40

- 意法半导体披露 2027-2028 年财务模型及2030年目标实现路径

- 创实技术electronica 2024首秀:加速国内分销商海外拓展之路

- 欧洲三大芯片巨头,重新审视供应链

- 一场IC设计业盛宴!10场论坛 200位演讲嘉宾,300+展商亮相2万平米专业展会!

- 富昌电子于杭州举办技术日活动,聚焦新能源“芯”机遇

- 消息称铠侠最快明天获上市批准,市值有望达 7500 亿日元

- 美国政府敲定对格芯 15 亿美元《CHIPS》法案补贴,支持后者提升在美产能

- SK 海力士宣布量产全球最高的 321 层 1Tb TLC 4D NAND 闪存,计划 2025 上半年对外出货

- 三星电子 NRD-K 半导体研发综合体进机,将导入 ASML High NA EUV 光刻设备

Mentor Xpedition从零开始做工程之高速PCB设计

Mentor Xpedition从零开始做工程之高速PCB设计 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号