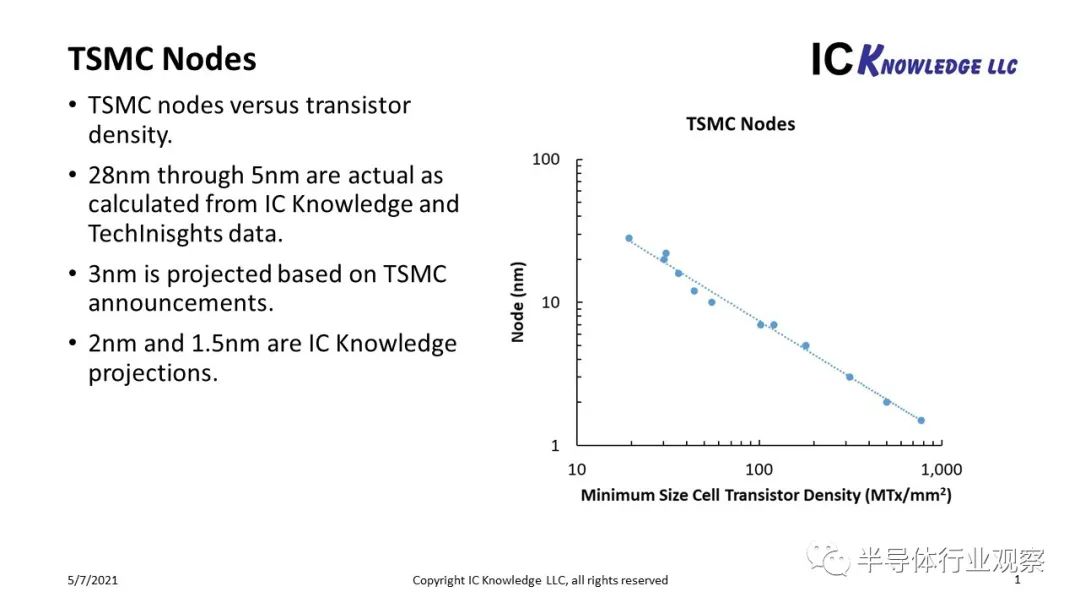

众所周知,IBM最近发布了2nm芯片,按照他们的说法,这个芯片的密度为3.33亿个晶体管/平方毫米(MTx / mm 2);栅极长度为12nm的44nm接触式多节距(CPP);基于IBM正在使用水平纳米片(HNS)的横截面,Gate All Around(GAA)可以采用多种方法进行GAA;HNS叠层构建在氧化物层之上;与最先进的7nm芯片相比,性能提高45%,功耗降低75%;EUV图案用于前端,可让HNS片材宽度在15nm至70nm之间变化。这对于调整电路的各个区域以实现低功耗或高性能以及SRAM单元非常有用;sheet为5nm厚,堆叠为三层高。但这真的是“ 2nm”吗?台积电是目前生产工艺技术的领导者。我们绘制了TSMC节点名称与晶体管密度的关系图,并拟合了0.99 R2值的曲线,见图1。使用曲线拟合,我们可以将晶体管密度转换为TSMC等效节点(TEN)。使用曲线拟合,对于IBM宣布的333MTx / mm 2,我们得到2.9nm的TEN 。我们认为这使公告成为3nm节点,而不是2nm节点。为了更详细地将IBM公告与之前宣布的3nm工艺和预计的2nm工艺进行比较,我们需要进行一些估算。从公告中我们知道CPP为44nm。我们假设一个单扩散中断(SDB)将导致最密集的过程。查看公告中的横截面,我们看不到埋入式电源导轨(BPR),需要BPR才能将HNS轨道高度降低到5.0,因此我们假设该过程为6.0。为了达到333MTx / mm 2,最小金属间距必须为18nm,这是一个非常具有挑战性的值,可能需要EUV多图案。

图2将IBM 2nm设计与我们对三星和台积电3nm工艺的估计进行了比较。我们知道三星也在制造HNS,而台积电则选择了3nm的FinFET。三星和台积电都宣布将3nm工艺的密度提高,因此我们知道这三家公司的晶体管密度,并且可以计算出这三家公司的TEN。如前所述,IBM的TEN为2.9,我们现在看到三星的TEN为4.7,台积电的TEN为3.0,再次证明IBM 2nm就像台积电3nm,而三星则落后于台积电。估计图2中红色的数字达到了宣布的密度。我们假设所有公司均为SDB。台积电的 track height最小,因为FinFET可以不带BPR地达到5.0的 track height,但是HNS需要BPR才能达到5.0,而BPR尚未准备好。

如图3,我们还预测了三星和台积电2nm工艺。我们预计两家公司都将使用BPR(BPR尚未准备好,但很可能是三星和台积电在2023/2024左右推出2nm工艺时搞定)。我们还假设三星和台积电将利用forksheet NHS,HNS(FS)架构能达到4.33的track height ,从而放松了其他一些微缩要求,然后根据该公司最近的微缩趋势预测了CPP和MMP。

在今年的ISS上,我通过一些附加的英特尔性能数据,按节点估算了三星和台积电的相对功耗和性能。逐节点趋势是基于两家公司宣布的功率和性能缩放估计与14nm / 16nm的可用比较得出的。由于IBM将其功耗和性能改进与领先的7nm性能进行了比较,因此我可以将IBM的功率和性能放在我先前介绍的相同趋势图上,见图4。IBM对HNS的使用大大降低了功耗,并使2nm制程比三星或台积电(TSMC)的3nm制程更省电,尽管我们相信,一旦台积电在2nm上采用HNS,它们在功耗上将与IBM相同或更好。为了提高性能,我们估计台积电的3nm工艺将胜过IBM 2nm工艺。正如ISS文章中所讨论的那样,这些趋势仅是估计值,并基于许多假设,但这是我们可以汇总的最佳预测。由此可见,在分析了IBM的公告之后,我们认为从密度的角度来看,他们的“ 2nm”工艺更像是TSMC的3nm工艺,虽然功耗更高但性能却较差。IBM的声明令人印象深刻,但它是一种研究设备,与台积电的3nm制程相比,只有明显的优势,而台积电3nm的风险将在今年晚些时候开始,并于明年开始量产。我们进一步相信,当台积电工艺在2023/2024左右投产时,它将在2nm的密度,功耗和性能方面处于领导地位。

IBM在新闻稿中表示,新工艺将在指甲大小的芯片上生产约500亿个晶体管。它还将带来比今天的7纳米芯片高出75%的效率或快45%的芯片。从表面上看,IBM似乎在顶级芯片技术的竞争中跃居了遥遥领先的地位。英特尔的最新芯片使用10纳米工艺,而台积电则使用7纳米工艺。该公司在这里取得了一些非常出色的成就。但是比较芯片很复杂。因此,值得更多地剖析新闻,以更好地了解大局。

长期以来,计算机芯片的进步一直以纳米级的步伐进行衡量。每一步降低都会产生更多的组件(最著名的是晶体管)被封装到同一区域中。在过去的几十年中,有一段时间纳米命名法确实与某些芯片元件的尺寸匹配。但是那段时间已经过去了。随着芯片技术的进步,对芯片组件的测量与每一代的命名约定分离。十多年前,当芯片成为FinFET的最后一次重大飞跃时(形状像鳍的3D晶体管设计),该行业的节点数量几乎毫无意义。它与芯片上的任何尺寸都没有关系。当前正在争论哪种新数字或数字组合可以更好地反映进度。并且尽管这也被证明相当复杂,但一位规范专家提出的是每平方毫米的晶体管密度。要了解旧的命名约定如何造成混淆,请将英特尔的10纳米芯片与台积电的7纳米芯片进行比较。两者实际上具有大致相等的晶体管密度,英特尔的每平方英寸1亿个晶体管实际上要比台积电的每平方毫米9千1百万个晶体管小。(如下图有一个方便的表格,用于比较工艺尺寸和芯片的晶体管密度。)IBM没有明确宣布其芯片的晶体管密度。但是在伸手弄清楚他们指的是什么尺寸的“指甲”之后(该公司的代表说大约为150平方毫米),该出版物AnandTech计算出IBM的新工艺每平方毫米将产生约3.33亿个晶体管。的确,这超出了现在已经生产中的任何芯片。也就是说,台积电为苹果生产的3纳米芯片每平方毫米可以拥有近3亿个晶体管,并有望在明年投入生产。

也许更重要的消息是晶体管本身的设计。IBM的新技术被称为纳米片或全能门晶体管,是当今FinFET晶体管期待已久的后续产品。自2017年以来,该公司一直在研究这项技术。FinFET晶体管由一个鳍形沟道组成,该沟道在三侧被“门”围绕,该“门”控制电子的流动。但是,IBM的纳米片(或全能门)晶体管具有分层的通道。这些层被堆叠在彼此的顶部上,并且由栅极包围上所有侧面。最后一点是最关键的部分。环绕栅晶体管可更好地控制通过沟道的电流,防止泄漏并提高效率。麻省理工学院专门研究新型晶体管技术的教授Jesúsdel Alamo告诉《连线》杂志:“这是一项令人兴奋的技术。” “这是一个全新的设计,可以推动未来的芯片路线图。” 尽管IBM可能是第一个在此级别上展示该技术的公司,但它们可能不会是最后一个。三星和台积电可能会效仿。现在要对现在的生产芯片和使用IBM新晶体管的未来芯片进行认真的性能比较还为时过早,但是可以肯定地说它们将提供显着的改进。分析公司VLSI Research的首席执行官Dan Hutcheson告诉《连线》, IBM估计的性能改进实际上似乎是保守的,并将这项工作称为“行业里程碑”。

您什么时候可以购买带有这些芯片之一的设备?可能不会。尽管IBM仍在设计芯片,但它在2014年出售了其芯片制造业务。这项新技术来自其位于纽约州奥尔巴尼市的研究机构,它是一个demo,而不是可用于生产的芯片。在未来的几年中,IBM将完成该过程,届时它可能会通过与英特尔和三星等合作伙伴的许可协议进入生产芯片。该行业在此期间不太可能会停滞不前。目前,芯片行业正在复兴。不再仅仅花费数十亿美元从传统芯片上拧干几滴。充满活力和创新的产业焕发了活力,并为特殊目的(如AI)带来了一系列奇特的设计。其中大部分发生在大公司之外。多年来,风险资本再次涌入新兴芯片公司,实际上,仅在2020年,就有超过120亿美元流入了400多家芯片公司。因此,即使在今年的芯片缺货严重,但季风似乎仍在聚集。

集成电路设计中的电源管理技术 (陈科宏)

集成电路设计中的电源管理技术 (陈科宏) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号