摘要:介绍XC2V1000型现场可编程门阵列(FPGA)的主要特性和FIR抽取滤波器的工作原理,重点阐述用XC2V1000实现FIR抽取滤波器的方法,并给出仿真波形和设计特点。

关键词:FIR抽取滤波器;流水线操作;XC2V1000;现场可编程门阵列

1 引言

抽取滤波器广泛应用在数字接收领域,是数字下变频器的核心部分。目前,抽取滤波器的实现方法有3种:单片通用数字滤波器集成电路、DSP和可编程逻辑器件。使用单片通用数字滤波器很方便,但字长和阶数的规格较少,不能完全满足实际需要。使用DSP虽然简单,但程序要顺序执行,执行速度必然慢。现场可编程门阵列(FPGA)有着规整的内部逻辑阵列和丰富的连线资源,特别适用于数字信号处理,但长期以来,用FPGA实现抽取滤波器比较复杂,其原因主要是FPGA中缺乏实现乘法运算的有效结构。现在,FPGA集成了乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍用Xilinx公司的XC2V1000型FPGA实现FIR抽取滤波器的设计方法。

2 XC2V1000简介

Virtex-Ⅱ系列是Xilinx公司近几年研发的具有高性能、高速度和低功耗特点的新一代FPGA,一经问世就备受界内人士的青睐。该系列FPGA基于IP核和专用模块设计,能够为电信、无线电、网络、视频和数字信号处理领域的应用提供完整的解决方案。XC2V1000是Virtex-Ⅱ家族的一员,具有如下主要特点:

●100万个系统门;

●40%26;#215;32个可配置逻辑单元(5120个slice);

●40个18%26;#215;18 bits乘法器,1个工作时钟内即可完成乘法运算;

●720Kbits RAM,可灵活配置(单口、双口、有使能或无使能等);

●8个DCM(Digital Clock Manager)模块;

●328个用户I/O。

此外,Xilinx公司还提供了功能强大的开发平台(ISE),开发者可通过该平台完成全部设计。

3 抽取滤波器的工作原理

抽取滤波器的工作原理是在滤波过程中实现抽取。对于抽取率为N的抽取滤波器而言,不是每进入1个新数据就完成1次滤波运算,然后再抽取,而是当进来N个数据时滤波器才完成1次滤波运算,输出1次滤波结果。抽取滤波器的结果和先滤波后抽取的结果是一致的,只是对于同样的数据,进行滤波运算的次数大大减少。在数字系统中采用抽取滤波器的最大优点是增加了每次滤波的可处理时间,从而达到实现高速输入数据的目的。下面以抽取率为2的具有线性相位的3阶FIR抽取滤波器为例介绍抽取滤波器的实现过程。

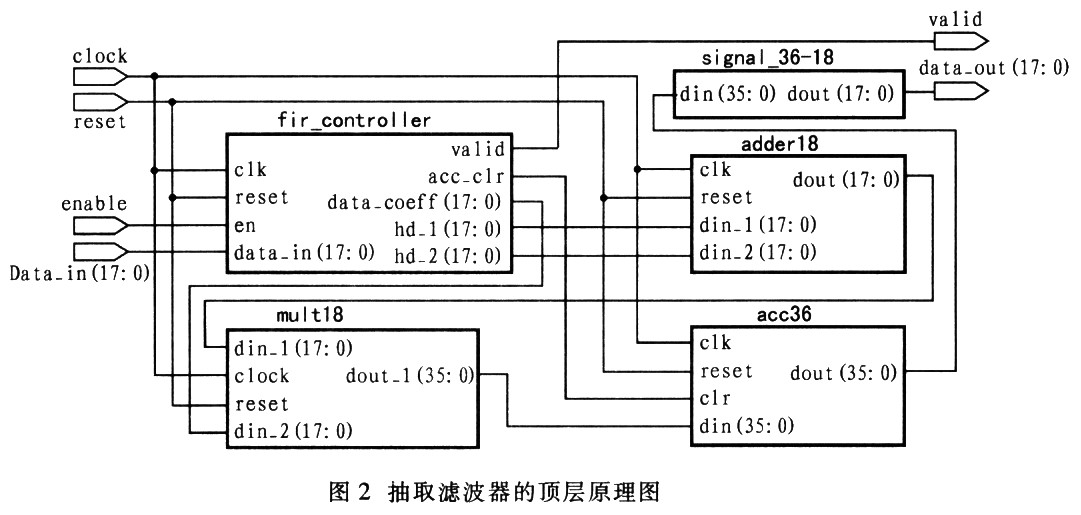

线性相位的FIR滤波器的系数具有某种对称的性质[1],3阶Ⅱ类FIR线性相位滤波器在数学上可以表示为

线性相位的FIR滤波器的系数具有某种对称的性质[1],3阶Ⅱ类FIR线性相位滤波器在数学上可以表示为

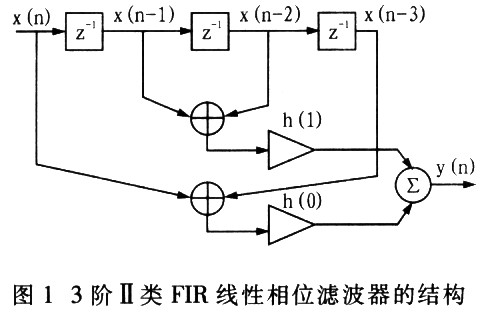

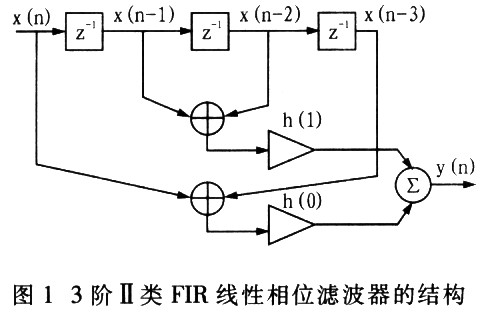

其中,h(0)=h(3),h(1)=h(2)。其结构如图1所示。由图1可见,具有4个系数的3阶Ⅱ类FIR线性相位滤波器只需2次加法、2次乘法和2次累加就可以完成1次滤波运算。如果IPGA工作时钟为80MHz,输入x(n)的数据率也为80MHz,那么经2倍抽取后输出y(n)为40MHz。也就是说,抽取滤波器每完成1次滤波运算,需要2个工作时钟。如果加法器、乘法器和累加器在单个时钟内就能完成1次功能运算,那么只需1个加法器、1个乘法器和1个累加器采用流水线操作在2个工作时钟内就可以完成2次加法、2次乘法和2次累加运算,就可以完成一次抽取滤波。

4 具体实现

4.1 结构设计

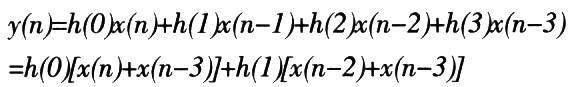

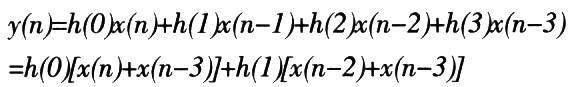

基于上述抽取滤波器的工作原理,笔者用XC2V1000实现了这个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL硬件描述语言共同完成源文件设计。图2是抽取滤波器的顶层原理图。其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。addei18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36-18是数据截位器模块,fir_controller是控制器模块。控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

其中,h(0)=h(3),h(1)=h(2)。其结构如图1所示。由图1可见,具有4个系数的3阶Ⅱ类FIR线性相位滤波器只需2次加法、2次乘法和2次累加就可以完成1次滤波运算。如果IPGA工作时钟为80MHz,输入x(n)的数据率也为80MHz,那么经2倍抽取后输出y(n)为40MHz。也就是说,抽取滤波器每完成1次滤波运算,需要2个工作时钟。如果加法器、乘法器和累加器在单个时钟内就能完成1次功能运算,那么只需1个加法器、1个乘法器和1个累加器采用流水线操作在2个工作时钟内就可以完成2次加法、2次乘法和2次累加运算,就可以完成一次抽取滤波。

4 具体实现

4.1 结构设计

基于上述抽取滤波器的工作原理,笔者用XC2V1000实现了这个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL硬件描述语言共同完成源文件设计。图2是抽取滤波器的顶层原理图。其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。addei18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36-18是数据截位器模块,fir_controller是控制器模块。控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

4.1.1控制器(fir_controller)

控制器是抽取滤波器的核心模块,有2种功能:接收输入数据,向其他模块发送数据和控制信号。它根据加法器、乘法器和累加器的时序特性,规律地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器每个时钟都完成指定的任务,从而实现流水线操作。控制器用YHDL语言描述,用寄存器存放抽头和系数。

4.1.2加法器(adder18)

加法器的输入和输出都是18bits,用VHDL语言描述实现。它有2个工作时钟的延迟,在输入数据准备好的情况下,第一个时钟得出相加结果,第二个时钟把相加结果锁存输出。

4.1.3乘法器(multl8)

乘法器是18bits输入和36bits输出,用库元件MULT18X18S和36bits锁存器实现。MULT18Xl8S是XC2V1000自带的18%26;#215;18bits乘法器,单个时钟就可完成乘法运算;36bits锁存器工作于时钟的上升沿,用VHDL语言描述。乘法器(mult18)也有2个工作时钟的延时,在输入数据准备好的情况下,第一个时钟得出相乘结果,第二个时钟把相乘结果锁存输出。加法器和乘法器采用锁存输出的结构,虽然增加了1个工作时钟的延迟,但有利于抽取滤波器稳定的工作,提高可靠性。

4.1.4累加器(acc36)

36bits累加器用于累加乘法器的输出,得出滤波结果。它有1个控制端口clr,当clr为高电平时,输出前一轮累加结果,并初始化开始新一轮累加;当clr为低电平时.进行累加运算。累加器用VHDL语言描述。

4.1.5数据截位器(signal_36-18)

数据截位器用VHDL语言描述,用于把累加器的36位输出进行取舍处理,一般截掉数据低位部分,保留数据高位。为了对抽取滤波器进行功能仿真,这里截掉数据高18位,保留数据低18位。

4.2 工作过程及功能仿真

加法器、乘法器和累加器在控制器的作用下每个时钟都要完成指定的任务,从而形成流水线操作,实现抽取滤波。

下面以抽取滤波器完成1次抽取滤波的全过程为例,说明抽取滤波器的工作过程。假设时钟1、时钟2、时钟3和时钟4控制器已接收了数据x(n-3)、x(n-2)、x(n-1)和x(n),那么,

时钟5:控制器向加法器发送数据x(n)和x(n-3);

时钟6:加法器进行。x(n)+x(n-3)运算;控制器向加法器发送数据x(n-1)和x(n-2);

时钟7:加法器进行x(n-1)+x(n-2)运算,输出x (n)+x(n-3)运算结果。控制器向乘法器发送系数h(0);

时钟8:加法器输出x(n-1)+x(n-2)运算结果,乘法器进行h(0)[x(n)+x(n-3)]运算,控制器向乘法器发送系数h(1) ;

时钟9:乘法器进行h(1)[x(n-1)+x(n-2)]运算,输出h(0)[x(n)+x(n-3)1运算结果。控制器向累加器发送控制信号(clr为高电平);

时钟10:乘法器输出h(1)[x(n-1)+x(n-2)]运算结果。累加器初始化开始累加操作。控制器向累加器发送控制信号(clr为低电平);

时钟11:累加器进行累加运算h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]。控制器向累加器发送控制信号(clr为高电平),控制器输出滤波数据有效信号(valid为高电平);

时钟12:累加器输出h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]累加结果,并初始化开始新一轮累加操作。控制器输出滤波数据无效信号(valid为低电平);

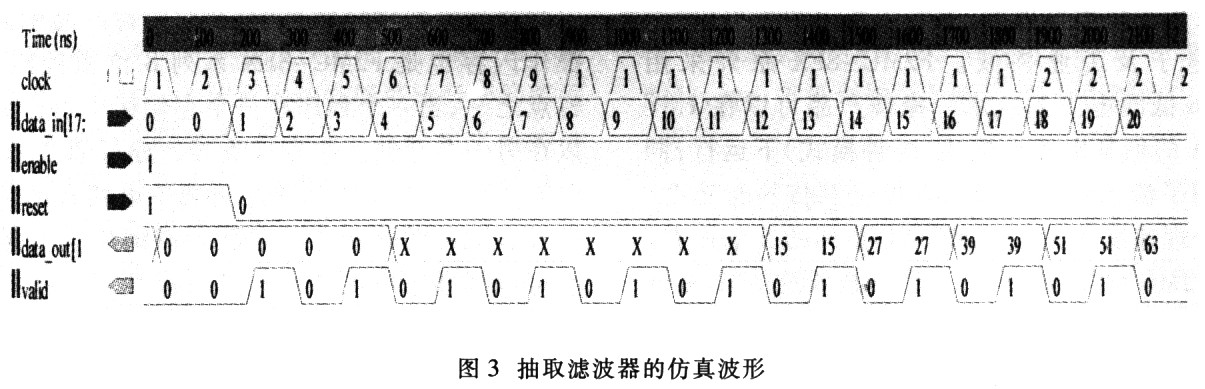

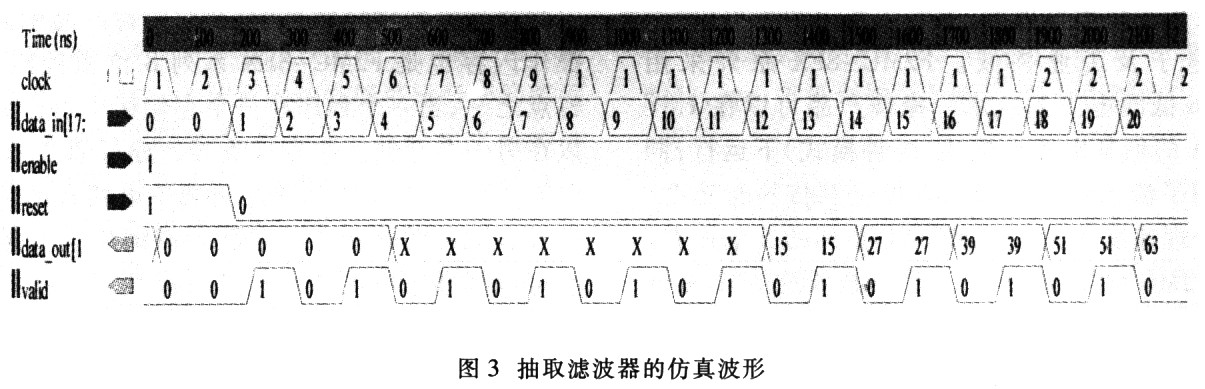

以上就是抽取滤波器完成1次抽取滤波的全过程。可见,从数据x(n)输入到滤波结果y(n)输出需要8个工作时钟。如果控制器不停地向加法器、乘法器和加法器发送抽头、系数和控制信号,就会形成流水线操作,那么每2个时钟,抽取滤波器就会输出1个滤波结果。图3是抽取滤波器的仿真波形图,其中在控制器中设置系数h(0)=1和h(1)=2。

4.1.1控制器(fir_controller)

控制器是抽取滤波器的核心模块,有2种功能:接收输入数据,向其他模块发送数据和控制信号。它根据加法器、乘法器和累加器的时序特性,规律地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器每个时钟都完成指定的任务,从而实现流水线操作。控制器用YHDL语言描述,用寄存器存放抽头和系数。

4.1.2加法器(adder18)

加法器的输入和输出都是18bits,用VHDL语言描述实现。它有2个工作时钟的延迟,在输入数据准备好的情况下,第一个时钟得出相加结果,第二个时钟把相加结果锁存输出。

4.1.3乘法器(multl8)

乘法器是18bits输入和36bits输出,用库元件MULT18X18S和36bits锁存器实现。MULT18Xl8S是XC2V1000自带的18%26;#215;18bits乘法器,单个时钟就可完成乘法运算;36bits锁存器工作于时钟的上升沿,用VHDL语言描述。乘法器(mult18)也有2个工作时钟的延时,在输入数据准备好的情况下,第一个时钟得出相乘结果,第二个时钟把相乘结果锁存输出。加法器和乘法器采用锁存输出的结构,虽然增加了1个工作时钟的延迟,但有利于抽取滤波器稳定的工作,提高可靠性。

4.1.4累加器(acc36)

36bits累加器用于累加乘法器的输出,得出滤波结果。它有1个控制端口clr,当clr为高电平时,输出前一轮累加结果,并初始化开始新一轮累加;当clr为低电平时.进行累加运算。累加器用VHDL语言描述。

4.1.5数据截位器(signal_36-18)

数据截位器用VHDL语言描述,用于把累加器的36位输出进行取舍处理,一般截掉数据低位部分,保留数据高位。为了对抽取滤波器进行功能仿真,这里截掉数据高18位,保留数据低18位。

4.2 工作过程及功能仿真

加法器、乘法器和累加器在控制器的作用下每个时钟都要完成指定的任务,从而形成流水线操作,实现抽取滤波。

下面以抽取滤波器完成1次抽取滤波的全过程为例,说明抽取滤波器的工作过程。假设时钟1、时钟2、时钟3和时钟4控制器已接收了数据x(n-3)、x(n-2)、x(n-1)和x(n),那么,

时钟5:控制器向加法器发送数据x(n)和x(n-3);

时钟6:加法器进行。x(n)+x(n-3)运算;控制器向加法器发送数据x(n-1)和x(n-2);

时钟7:加法器进行x(n-1)+x(n-2)运算,输出x (n)+x(n-3)运算结果。控制器向乘法器发送系数h(0);

时钟8:加法器输出x(n-1)+x(n-2)运算结果,乘法器进行h(0)[x(n)+x(n-3)]运算,控制器向乘法器发送系数h(1) ;

时钟9:乘法器进行h(1)[x(n-1)+x(n-2)]运算,输出h(0)[x(n)+x(n-3)1运算结果。控制器向累加器发送控制信号(clr为高电平);

时钟10:乘法器输出h(1)[x(n-1)+x(n-2)]运算结果。累加器初始化开始累加操作。控制器向累加器发送控制信号(clr为低电平);

时钟11:累加器进行累加运算h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]。控制器向累加器发送控制信号(clr为高电平),控制器输出滤波数据有效信号(valid为高电平);

时钟12:累加器输出h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]累加结果,并初始化开始新一轮累加操作。控制器输出滤波数据无效信号(valid为低电平);

以上就是抽取滤波器完成1次抽取滤波的全过程。可见,从数据x(n)输入到滤波结果y(n)输出需要8个工作时钟。如果控制器不停地向加法器、乘法器和加法器发送抽头、系数和控制信号,就会形成流水线操作,那么每2个时钟,抽取滤波器就会输出1个滤波结果。图3是抽取滤波器的仿真波形图,其中在控制器中设置系数h(0)=1和h(1)=2。

4.3注意事项

2个n位二进制数相加,其和至少需要n+l位二进制数才能正确表示。本设计中的加法器输入输出都是18位,为了防止加法器溢出,应确保18位输入数据x(n)的最高2位相同(都是符号位)。

为了实现抽取滤波器的多级串联结构,应统一输入数据有效信号enable和输出数据有效信号valid的时序要求。本设计规定控制器在累加器输出滤波结果数后下1个时钟送出滤波结果有效信号,时宽为1个工作时钟周期。

5 设计特点

采用此设计结构实现抽取滤波器具有以下3个特点:

(1)节省片内资源和提高资源使用效率

Xilinx公司为了方便用户设计滤波器,在IP核中集成了通用数字滤波器的设计,但利用IP核生成的数字滤波器往往不能针对实际情况合理地利用片内资源,造成资源浪费。本设计中采用了流水线结构,所有功能模块都满负荷工作,没有空闲等待时钟,从而节省了片内资源,提高了资源使用率。

(2)可以实现抽取滤波器多级结构

针对抽取滤波器的输出特性,可以采取相同的设计方法再设计一级抽取滤波器,对前一级输出的数据再次抽取滤波,从而实现多级抽取滤波器结构。

(3)设计灵活且扩展性强

用寄存器存放抽头和系数适用于滤波器阶数较少的情况,如果需要用上百阶的抽取滤波,最好用片内:RAM存放抽头和系数,这时只要稍加改动控制器的逻辑设计既可实现。在此基础上,还可实现可编程抽取滤波器。

6 结束语

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。用该方法设计出的抽取滤波器灵活性强、资源利用率高,能广泛应用于数字接收领域。

4.3注意事项

2个n位二进制数相加,其和至少需要n+l位二进制数才能正确表示。本设计中的加法器输入输出都是18位,为了防止加法器溢出,应确保18位输入数据x(n)的最高2位相同(都是符号位)。

为了实现抽取滤波器的多级串联结构,应统一输入数据有效信号enable和输出数据有效信号valid的时序要求。本设计规定控制器在累加器输出滤波结果数后下1个时钟送出滤波结果有效信号,时宽为1个工作时钟周期。

5 设计特点

采用此设计结构实现抽取滤波器具有以下3个特点:

(1)节省片内资源和提高资源使用效率

Xilinx公司为了方便用户设计滤波器,在IP核中集成了通用数字滤波器的设计,但利用IP核生成的数字滤波器往往不能针对实际情况合理地利用片内资源,造成资源浪费。本设计中采用了流水线结构,所有功能模块都满负荷工作,没有空闲等待时钟,从而节省了片内资源,提高了资源使用率。

(2)可以实现抽取滤波器多级结构

针对抽取滤波器的输出特性,可以采取相同的设计方法再设计一级抽取滤波器,对前一级输出的数据再次抽取滤波,从而实现多级抽取滤波器结构。

(3)设计灵活且扩展性强

用寄存器存放抽头和系数适用于滤波器阶数较少的情况,如果需要用上百阶的抽取滤波,最好用片内:RAM存放抽头和系数,这时只要稍加改动控制器的逻辑设计既可实现。在此基础上,还可实现可编程抽取滤波器。

6 结束语

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。用该方法设计出的抽取滤波器灵活性强、资源利用率高,能广泛应用于数字接收领域。

编辑: 引用地址:基于XC2V1000型FPGA的FIR抽取滤波器的设计

线性相位的FIR滤波器的系数具有某种对称的性质[1],3阶Ⅱ类FIR线性相位滤波器在数学上可以表示为

线性相位的FIR滤波器的系数具有某种对称的性质[1],3阶Ⅱ类FIR线性相位滤波器在数学上可以表示为

其中,h(0)=h(3),h(1)=h(2)。其结构如图1所示。由图1可见,具有4个系数的3阶Ⅱ类FIR线性相位滤波器只需2次加法、2次乘法和2次累加就可以完成1次滤波运算。如果IPGA工作时钟为80MHz,输入x(n)的数据率也为80MHz,那么经2倍抽取后输出y(n)为40MHz。也就是说,抽取滤波器每完成1次滤波运算,需要2个工作时钟。如果加法器、乘法器和累加器在单个时钟内就能完成1次功能运算,那么只需1个加法器、1个乘法器和1个累加器采用流水线操作在2个工作时钟内就可以完成2次加法、2次乘法和2次累加运算,就可以完成一次抽取滤波。

4 具体实现

4.1 结构设计

基于上述抽取滤波器的工作原理,笔者用XC2V1000实现了这个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL硬件描述语言共同完成源文件设计。图2是抽取滤波器的顶层原理图。其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。addei18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36-18是数据截位器模块,fir_controller是控制器模块。控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

其中,h(0)=h(3),h(1)=h(2)。其结构如图1所示。由图1可见,具有4个系数的3阶Ⅱ类FIR线性相位滤波器只需2次加法、2次乘法和2次累加就可以完成1次滤波运算。如果IPGA工作时钟为80MHz,输入x(n)的数据率也为80MHz,那么经2倍抽取后输出y(n)为40MHz。也就是说,抽取滤波器每完成1次滤波运算,需要2个工作时钟。如果加法器、乘法器和累加器在单个时钟内就能完成1次功能运算,那么只需1个加法器、1个乘法器和1个累加器采用流水线操作在2个工作时钟内就可以完成2次加法、2次乘法和2次累加运算,就可以完成一次抽取滤波。

4 具体实现

4.1 结构设计

基于上述抽取滤波器的工作原理,笔者用XC2V1000实现了这个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL硬件描述语言共同完成源文件设计。图2是抽取滤波器的顶层原理图。其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。addei18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36-18是数据截位器模块,fir_controller是控制器模块。控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

4.1.1控制器(fir_controller)

控制器是抽取滤波器的核心模块,有2种功能:接收输入数据,向其他模块发送数据和控制信号。它根据加法器、乘法器和累加器的时序特性,规律地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器每个时钟都完成指定的任务,从而实现流水线操作。控制器用YHDL语言描述,用寄存器存放抽头和系数。

4.1.2加法器(adder18)

加法器的输入和输出都是18bits,用VHDL语言描述实现。它有2个工作时钟的延迟,在输入数据准备好的情况下,第一个时钟得出相加结果,第二个时钟把相加结果锁存输出。

4.1.3乘法器(multl8)

乘法器是18bits输入和36bits输出,用库元件MULT18X18S和36bits锁存器实现。MULT18Xl8S是XC2V1000自带的18%26;#215;18bits乘法器,单个时钟就可完成乘法运算;36bits锁存器工作于时钟的上升沿,用VHDL语言描述。乘法器(mult18)也有2个工作时钟的延时,在输入数据准备好的情况下,第一个时钟得出相乘结果,第二个时钟把相乘结果锁存输出。加法器和乘法器采用锁存输出的结构,虽然增加了1个工作时钟的延迟,但有利于抽取滤波器稳定的工作,提高可靠性。

4.1.4累加器(acc36)

36bits累加器用于累加乘法器的输出,得出滤波结果。它有1个控制端口clr,当clr为高电平时,输出前一轮累加结果,并初始化开始新一轮累加;当clr为低电平时.进行累加运算。累加器用VHDL语言描述。

4.1.5数据截位器(signal_36-18)

数据截位器用VHDL语言描述,用于把累加器的36位输出进行取舍处理,一般截掉数据低位部分,保留数据高位。为了对抽取滤波器进行功能仿真,这里截掉数据高18位,保留数据低18位。

4.2 工作过程及功能仿真

加法器、乘法器和累加器在控制器的作用下每个时钟都要完成指定的任务,从而形成流水线操作,实现抽取滤波。

下面以抽取滤波器完成1次抽取滤波的全过程为例,说明抽取滤波器的工作过程。假设时钟1、时钟2、时钟3和时钟4控制器已接收了数据x(n-3)、x(n-2)、x(n-1)和x(n),那么,

时钟5:控制器向加法器发送数据x(n)和x(n-3);

时钟6:加法器进行。x(n)+x(n-3)运算;控制器向加法器发送数据x(n-1)和x(n-2);

时钟7:加法器进行x(n-1)+x(n-2)运算,输出x (n)+x(n-3)运算结果。控制器向乘法器发送系数h(0);

时钟8:加法器输出x(n-1)+x(n-2)运算结果,乘法器进行h(0)[x(n)+x(n-3)]运算,控制器向乘法器发送系数h(1) ;

时钟9:乘法器进行h(1)[x(n-1)+x(n-2)]运算,输出h(0)[x(n)+x(n-3)1运算结果。控制器向累加器发送控制信号(clr为高电平);

时钟10:乘法器输出h(1)[x(n-1)+x(n-2)]运算结果。累加器初始化开始累加操作。控制器向累加器发送控制信号(clr为低电平);

时钟11:累加器进行累加运算h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]。控制器向累加器发送控制信号(clr为高电平),控制器输出滤波数据有效信号(valid为高电平);

时钟12:累加器输出h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]累加结果,并初始化开始新一轮累加操作。控制器输出滤波数据无效信号(valid为低电平);

以上就是抽取滤波器完成1次抽取滤波的全过程。可见,从数据x(n)输入到滤波结果y(n)输出需要8个工作时钟。如果控制器不停地向加法器、乘法器和加法器发送抽头、系数和控制信号,就会形成流水线操作,那么每2个时钟,抽取滤波器就会输出1个滤波结果。图3是抽取滤波器的仿真波形图,其中在控制器中设置系数h(0)=1和h(1)=2。

4.1.1控制器(fir_controller)

控制器是抽取滤波器的核心模块,有2种功能:接收输入数据,向其他模块发送数据和控制信号。它根据加法器、乘法器和累加器的时序特性,规律地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器每个时钟都完成指定的任务,从而实现流水线操作。控制器用YHDL语言描述,用寄存器存放抽头和系数。

4.1.2加法器(adder18)

加法器的输入和输出都是18bits,用VHDL语言描述实现。它有2个工作时钟的延迟,在输入数据准备好的情况下,第一个时钟得出相加结果,第二个时钟把相加结果锁存输出。

4.1.3乘法器(multl8)

乘法器是18bits输入和36bits输出,用库元件MULT18X18S和36bits锁存器实现。MULT18Xl8S是XC2V1000自带的18%26;#215;18bits乘法器,单个时钟就可完成乘法运算;36bits锁存器工作于时钟的上升沿,用VHDL语言描述。乘法器(mult18)也有2个工作时钟的延时,在输入数据准备好的情况下,第一个时钟得出相乘结果,第二个时钟把相乘结果锁存输出。加法器和乘法器采用锁存输出的结构,虽然增加了1个工作时钟的延迟,但有利于抽取滤波器稳定的工作,提高可靠性。

4.1.4累加器(acc36)

36bits累加器用于累加乘法器的输出,得出滤波结果。它有1个控制端口clr,当clr为高电平时,输出前一轮累加结果,并初始化开始新一轮累加;当clr为低电平时.进行累加运算。累加器用VHDL语言描述。

4.1.5数据截位器(signal_36-18)

数据截位器用VHDL语言描述,用于把累加器的36位输出进行取舍处理,一般截掉数据低位部分,保留数据高位。为了对抽取滤波器进行功能仿真,这里截掉数据高18位,保留数据低18位。

4.2 工作过程及功能仿真

加法器、乘法器和累加器在控制器的作用下每个时钟都要完成指定的任务,从而形成流水线操作,实现抽取滤波。

下面以抽取滤波器完成1次抽取滤波的全过程为例,说明抽取滤波器的工作过程。假设时钟1、时钟2、时钟3和时钟4控制器已接收了数据x(n-3)、x(n-2)、x(n-1)和x(n),那么,

时钟5:控制器向加法器发送数据x(n)和x(n-3);

时钟6:加法器进行。x(n)+x(n-3)运算;控制器向加法器发送数据x(n-1)和x(n-2);

时钟7:加法器进行x(n-1)+x(n-2)运算,输出x (n)+x(n-3)运算结果。控制器向乘法器发送系数h(0);

时钟8:加法器输出x(n-1)+x(n-2)运算结果,乘法器进行h(0)[x(n)+x(n-3)]运算,控制器向乘法器发送系数h(1) ;

时钟9:乘法器进行h(1)[x(n-1)+x(n-2)]运算,输出h(0)[x(n)+x(n-3)1运算结果。控制器向累加器发送控制信号(clr为高电平);

时钟10:乘法器输出h(1)[x(n-1)+x(n-2)]运算结果。累加器初始化开始累加操作。控制器向累加器发送控制信号(clr为低电平);

时钟11:累加器进行累加运算h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]。控制器向累加器发送控制信号(clr为高电平),控制器输出滤波数据有效信号(valid为高电平);

时钟12:累加器输出h(0)[x(n)+x(n-3)]+h(1)[x(n-1)+x(n-2)]累加结果,并初始化开始新一轮累加操作。控制器输出滤波数据无效信号(valid为低电平);

以上就是抽取滤波器完成1次抽取滤波的全过程。可见,从数据x(n)输入到滤波结果y(n)输出需要8个工作时钟。如果控制器不停地向加法器、乘法器和加法器发送抽头、系数和控制信号,就会形成流水线操作,那么每2个时钟,抽取滤波器就会输出1个滤波结果。图3是抽取滤波器的仿真波形图,其中在控制器中设置系数h(0)=1和h(1)=2。

4.3注意事项

2个n位二进制数相加,其和至少需要n+l位二进制数才能正确表示。本设计中的加法器输入输出都是18位,为了防止加法器溢出,应确保18位输入数据x(n)的最高2位相同(都是符号位)。

为了实现抽取滤波器的多级串联结构,应统一输入数据有效信号enable和输出数据有效信号valid的时序要求。本设计规定控制器在累加器输出滤波结果数后下1个时钟送出滤波结果有效信号,时宽为1个工作时钟周期。

5 设计特点

采用此设计结构实现抽取滤波器具有以下3个特点:

(1)节省片内资源和提高资源使用效率

Xilinx公司为了方便用户设计滤波器,在IP核中集成了通用数字滤波器的设计,但利用IP核生成的数字滤波器往往不能针对实际情况合理地利用片内资源,造成资源浪费。本设计中采用了流水线结构,所有功能模块都满负荷工作,没有空闲等待时钟,从而节省了片内资源,提高了资源使用率。

(2)可以实现抽取滤波器多级结构

针对抽取滤波器的输出特性,可以采取相同的设计方法再设计一级抽取滤波器,对前一级输出的数据再次抽取滤波,从而实现多级抽取滤波器结构。

(3)设计灵活且扩展性强

用寄存器存放抽头和系数适用于滤波器阶数较少的情况,如果需要用上百阶的抽取滤波,最好用片内:RAM存放抽头和系数,这时只要稍加改动控制器的逻辑设计既可实现。在此基础上,还可实现可编程抽取滤波器。

6 结束语

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。用该方法设计出的抽取滤波器灵活性强、资源利用率高,能广泛应用于数字接收领域。

4.3注意事项

2个n位二进制数相加,其和至少需要n+l位二进制数才能正确表示。本设计中的加法器输入输出都是18位,为了防止加法器溢出,应确保18位输入数据x(n)的最高2位相同(都是符号位)。

为了实现抽取滤波器的多级串联结构,应统一输入数据有效信号enable和输出数据有效信号valid的时序要求。本设计规定控制器在累加器输出滤波结果数后下1个时钟送出滤波结果有效信号,时宽为1个工作时钟周期。

5 设计特点

采用此设计结构实现抽取滤波器具有以下3个特点:

(1)节省片内资源和提高资源使用效率

Xilinx公司为了方便用户设计滤波器,在IP核中集成了通用数字滤波器的设计,但利用IP核生成的数字滤波器往往不能针对实际情况合理地利用片内资源,造成资源浪费。本设计中采用了流水线结构,所有功能模块都满负荷工作,没有空闲等待时钟,从而节省了片内资源,提高了资源使用率。

(2)可以实现抽取滤波器多级结构

针对抽取滤波器的输出特性,可以采取相同的设计方法再设计一级抽取滤波器,对前一级输出的数据再次抽取滤波,从而实现多级抽取滤波器结构。

(3)设计灵活且扩展性强

用寄存器存放抽头和系数适用于滤波器阶数较少的情况,如果需要用上百阶的抽取滤波,最好用片内:RAM存放抽头和系数,这时只要稍加改动控制器的逻辑设计既可实现。在此基础上,还可实现可编程抽取滤波器。

6 结束语

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。用该方法设计出的抽取滤波器灵活性强、资源利用率高,能广泛应用于数字接收领域。

上一篇:用FPGA实现1553B总线接口中的曼码编解码器

下一篇:基于Verilog HDL的CMOS图像敏感器驱动电路设计

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新半导体设计/制造文章

更多精选电路图

更多热门文章

更多每日新闻

- Power Integrations面向800V汽车应用推出新型宽爬电距离开关IC

- 打破台积电垄断!联电夺下高通先进封装订单

- Ampere 年度展望:2025年重塑IT格局的四大关键趋势

- 存储巨头铠侠正式挂牌上市:首日股价上涨超10%

- Vishay 推出新款精密薄膜MELF电阻,可减少系统元器件数量,节省空间,简化设计并降低成本

- 芯原推出新一代高性能Vitality架构GPU IP系列 支持DirectX 12和先进的计算能力

- NXP 2.5亿美元收购Aviva,但车载SerDes领域依然处于战国时期

- 应对 AI 时代的云工作负载,开发者正加速向 Arm 架构迁移

- 沉浸式体验漫威宇宙,英特尔锐炫显卡为《漫威争锋》提供Day 0支持

- 艾迈斯欧司朗与法雷奥携手革新车辆内饰,打造动态舱内环境

更多往期活动

厂商技术中心

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 OP-47CD/883B

OP-47CD/883B

京公网安备 11010802033920号

京公网安备 11010802033920号