摘要:介绍了未知电路板原理图测绘系统的基本实现原理,并在此原理的基础上,实现了柔性针床网络图测试系统。给出了该系统的设计方案,并详细说明了该系统软、硬件设计方法。实际应用表明,该系统能实现未知电路板原理的测绘工作,具有较好的应用前景。

关键词:电路原理图 测绘 柔性针床 USB CPLD

近年来,我国引进了大量先进的仪器设备,这些设备系统庞大、结构复杂、集成度高。经过多年的使用,这些设备在维护修理、备件保障方面遇到了极大的困难。由于不是技术引进,几乎没有任何关于设备的技术资料,无法获得电子备件的电路原理图,所以对未知(无电路原理图)电路板电路原理图的测绘,对于电子备件尤其是军工产品的反设计具有重要意义。

1 基本原理

要完成对未知电子备件的反设计,必须首先获知该备件的连线表,然后才能依据元器件数据库的相关知识绘制出原电路原理图,进而通过技术分析和设计形成替代方案,实现反设计。对未知电路板的测绘所使用的常用办法主要有如下两种:

(1)用万用表的欧姆档,对印制电路板上的各外露焊点和元器件管脚进行连接测试,即首先测量第一个焊点(或管脚)和第二、第三个焊点(或管脚)之间的电阻,直至测量完所有焊点和管脚,从而得到第一个焊点或管脚在电路板上的连接图。用同样的方法,再测第二个焊点(或管脚)与第三、第四个焊点(或管脚)之间的电阻,直至测量完所有焊点管脚,得到第二个焊点或管脚在电路板上的连接图。依次类推,可以得到电路板上各焊点和元器件管脚的连接关系(即网络图)。这种方法虽然能够得到电路板的网络图,但十分繁琐、效率低、差错率也高,因此应开发自动测绘设备。

(2)采用固定针床的办法进行测绘,对于每种电路板设计专门的测试针床,将专用针床与被测电路板的所有接点可靠接触,在计算机测试软件的控制下,通过专门的通道控制器可在较短时间内完成测试茉莉花和,而且能完成对多层电路板的测绘。但这种方式要求为每种被测对象设计一个专门的针床和测试软件,投放成本高、周期长。

综合以上两种方法的优点,根据常用的通路电阻测试法,设计了“柔性针床网络图测绘系统”,实现了灵活高效的测绘。连线表测试完成后,借助专建立的器件数据库,通过人工干预的方式即可完成电路原理图的绘制工作。

图2

2 系统硬件设计

2.1 系统总体结构

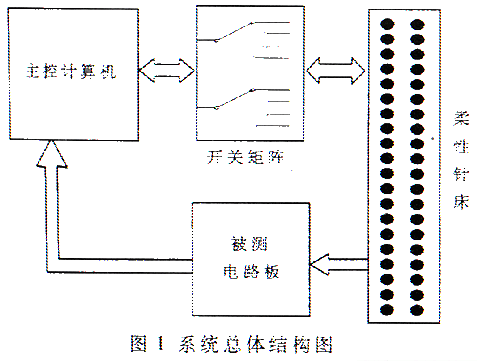

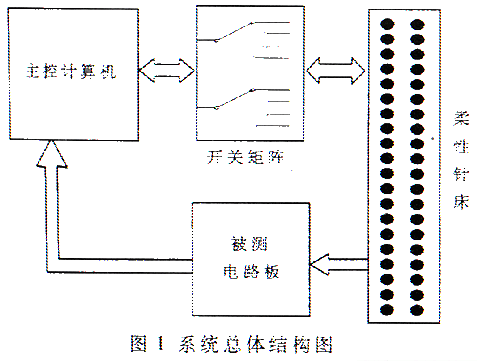

该系统由计算机、开关矩阵、柔性针床阵列和被测备件组成,其结构见图1。其中,柔性针床阵列通过柔性针与电路板上的所有节点可靠连接,开关矩阵实现通道的自动切换或顺序切换,柔性针床宽度仅能够覆盖一个电子芯片,这样通过多个针床,即可覆盖整个待测电路板。

测试时将电路板水平固定,在电路板上方和下方间距为2至3厘米处水平固定柔性针床,柔性针床的一面有密集分布的焊点,这些焊点通过长短可变的弹性探针与被测电路板一面上的外露焊点或元器件管脚相连。柔性针床的另一面由连线将各焊点与开关矩阵相连,电路板的另一面也进行相同的操作,从而将电路板的外露焊点或元器件管脚引到柔性针床上,通过计算机对开关矩阵进行控制,实现柔性针床上各节点之间的连接关系的自动测试。

2.2 测试电路结构组成

本系统采用自定义的总线结构,各柔性针床通过总线进行连接,由控制模块控制相互间的通信。测试电路通过USB总线接口与主机进行连接,如图2所示。

(1)用万用表的欧姆档,对印制电路板上的各外露焊点和元器件管脚进行连接测试,即首先测量第一个焊点(或管脚)和第二、第三个焊点(或管脚)之间的电阻,直至测量完所有焊点和管脚,从而得到第一个焊点或管脚在电路板上的连接图。用同样的方法,再测第二个焊点(或管脚)与第三、第四个焊点(或管脚)之间的电阻,直至测量完所有焊点管脚,得到第二个焊点或管脚在电路板上的连接图。依次类推,可以得到电路板上各焊点和元器件管脚的连接关系(即网络图)。这种方法虽然能够得到电路板的网络图,但十分繁琐、效率低、差错率也高,因此应开发自动测绘设备。

(2)采用固定针床的办法进行测绘,对于每种电路板设计专门的测试针床,将专用针床与被测电路板的所有接点可靠接触,在计算机测试软件的控制下,通过专门的通道控制器可在较短时间内完成测试茉莉花和,而且能完成对多层电路板的测绘。但这种方式要求为每种被测对象设计一个专门的针床和测试软件,投放成本高、周期长。

综合以上两种方法的优点,根据常用的通路电阻测试法,设计了“柔性针床网络图测绘系统”,实现了灵活高效的测绘。连线表测试完成后,借助专建立的器件数据库,通过人工干预的方式即可完成电路原理图的绘制工作。

图2

2 系统硬件设计

2.1 系统总体结构

该系统由计算机、开关矩阵、柔性针床阵列和被测备件组成,其结构见图1。其中,柔性针床阵列通过柔性针与电路板上的所有节点可靠连接,开关矩阵实现通道的自动切换或顺序切换,柔性针床宽度仅能够覆盖一个电子芯片,这样通过多个针床,即可覆盖整个待测电路板。

测试时将电路板水平固定,在电路板上方和下方间距为2至3厘米处水平固定柔性针床,柔性针床的一面有密集分布的焊点,这些焊点通过长短可变的弹性探针与被测电路板一面上的外露焊点或元器件管脚相连。柔性针床的另一面由连线将各焊点与开关矩阵相连,电路板的另一面也进行相同的操作,从而将电路板的外露焊点或元器件管脚引到柔性针床上,通过计算机对开关矩阵进行控制,实现柔性针床上各节点之间的连接关系的自动测试。

2.2 测试电路结构组成

本系统采用自定义的总线结构,各柔性针床通过总线进行连接,由控制模块控制相互间的通信。测试电路通过USB总线接口与主机进行连接,如图2所示。

其中,ADDR1和ADDR2为针床地址总线,控制模块通过发送相应的地址码实现针床的寻址。由于在测试时需要在针床本身和两个针床之间进行测试,只设计一套地址总线不能同时寻址两个针床,故设计了ADDR1和ADDR2两套地址总线,可同时实现对两个测试针床的寻址。

RD、WR为读使能和写使能总线,RD有效时,允许测试针床向控制模块发送数据,WR有效时,允许控制模块发送指令到各个针床,实现控制功能。

AD1、AD2为针床控针地址总线。由于在测试时,各个探针都需要和其它探针进行遍历测试,所以设计两套地址总线用来同时寻址两个不同的探针。AD1所寻址探针信号经数据线D1引出,AD2所寻址探针信号经数据线D2引出,通过测量D1与D2之间的电阻,就可以得到所对应的电路板焊点之间的连接情况。

在本设计中,PC机通过USB接口完成对测试机的控制,而测试数据又通过USB接口送回PC机进行分析,分析结果用于对UUT进行故障诊断。

本系统采用Cypress公司的AN2131QC作为控制器芯片。图3所示为AN2131QC的结构简化框图,USB总线收发器与USB总线引脚D+、D-相连,串行接口引擎用来对串行数据进行解码和译码、错误校验、位填充,并完成其它USB总线所需的信号,最终实现与USB总线接口的数据传输。通用微处理器采用增强型8051,与标准8051相比较,执行速度更快、功能更强大。在内部使用RAM作为程序代码和数据存储器,因此8051序列具有“软”特性,即:用户可以自动装载代码和数据来实现具体功能。

2.2.2 控制模块

控制模块用来完成各个针床的寻址、控制、测试以及数据的发送与接收功能。通过USB接口由主机下达控制命令及接收数据。控制模块结构如图4所示。

其中,ADDR1和ADDR2为针床地址总线,控制模块通过发送相应的地址码实现针床的寻址。由于在测试时需要在针床本身和两个针床之间进行测试,只设计一套地址总线不能同时寻址两个针床,故设计了ADDR1和ADDR2两套地址总线,可同时实现对两个测试针床的寻址。

RD、WR为读使能和写使能总线,RD有效时,允许测试针床向控制模块发送数据,WR有效时,允许控制模块发送指令到各个针床,实现控制功能。

AD1、AD2为针床控针地址总线。由于在测试时,各个探针都需要和其它探针进行遍历测试,所以设计两套地址总线用来同时寻址两个不同的探针。AD1所寻址探针信号经数据线D1引出,AD2所寻址探针信号经数据线D2引出,通过测量D1与D2之间的电阻,就可以得到所对应的电路板焊点之间的连接情况。

在本设计中,PC机通过USB接口完成对测试机的控制,而测试数据又通过USB接口送回PC机进行分析,分析结果用于对UUT进行故障诊断。

本系统采用Cypress公司的AN2131QC作为控制器芯片。图3所示为AN2131QC的结构简化框图,USB总线收发器与USB总线引脚D+、D-相连,串行接口引擎用来对串行数据进行解码和译码、错误校验、位填充,并完成其它USB总线所需的信号,最终实现与USB总线接口的数据传输。通用微处理器采用增强型8051,与标准8051相比较,执行速度更快、功能更强大。在内部使用RAM作为程序代码和数据存储器,因此8051序列具有“软”特性,即:用户可以自动装载代码和数据来实现具体功能。

2.2.2 控制模块

控制模块用来完成各个针床的寻址、控制、测试以及数据的发送与接收功能。通过USB接口由主机下达控制命令及接收数据。控制模块结构如图4所示。

系统控制芯片采用ALTERA公司的MAX7000系列可编程逻辑器件(CPLD),用来接收主机发送的控制信号,对测试电路进行控制;接收测试数据并上传到主机。当WR有效时,接收控制指令;当RD有效时,接收测试数据。在测试电路自定义总线上共有五种测试信号,所以采用三根控制信号线A、B、C,经译码即可输出不同的控制信号。电阻测试电路也位于控制模块中,负责对经D1和D2引出的电路板两个焊点(或管脚)进行测试,测试结果经A/D变换后由CPLD送到主机中。

2.2.3 测试针床

测试针床用来使用探针连接电路板各个焊点或管脚,并使用开关矩阵进行各个探针之间连接的自动顺序切换,从而实现各个焊点之间的互连测试。针床电路如图5所示。

开关矩阵采用MAX7000系列可编程逻辑器件实现,用来连接针床上所有探针,接收控制信号并将所寻址探针信号输出。

3 系统软件设计

系统软件运行于PC机平台上,通过USB总线对测试电路进行控制并接收测试电路测试数据,根据接收到的数据形成所测电路板电路连线表。现主要分析与电路测绘有关的测试电路控制程序:

(1)首先利用ADDR1寻址测试基准针床,每个针床都有特定地址码,如发送ADDR1=00000001,表示选中1号测试针床,以此为基准测试针床来对其它针床进行测试。

(2)号测试针床利用AD1总线对其上所有探针进行寻址,AD1总线寻址该针床的基准测试点,如发送AD1=00000001,表示寻址到1号探针,即1号探针连接D1端。

(3)以ADDR1所寻址针床为基准,利用ADDR2寻址所有针床,所寻址的针床利用AD2总线对其上探针进行寻址。

(4)以AD1总线所寻址探针为基准,对AD2总线所寻址探针进行遍历测试。

程序伪代码如下:

for(ADDR1=1 to 20) //假定共有20个测试针床,选定基准测试针床

{

for(AD1= 1 to 256) //假定每个针床上有256个探针和焊/点相连,选定基准测试焊点

{

系统控制芯片采用ALTERA公司的MAX7000系列可编程逻辑器件(CPLD),用来接收主机发送的控制信号,对测试电路进行控制;接收测试数据并上传到主机。当WR有效时,接收控制指令;当RD有效时,接收测试数据。在测试电路自定义总线上共有五种测试信号,所以采用三根控制信号线A、B、C,经译码即可输出不同的控制信号。电阻测试电路也位于控制模块中,负责对经D1和D2引出的电路板两个焊点(或管脚)进行测试,测试结果经A/D变换后由CPLD送到主机中。

2.2.3 测试针床

测试针床用来使用探针连接电路板各个焊点或管脚,并使用开关矩阵进行各个探针之间连接的自动顺序切换,从而实现各个焊点之间的互连测试。针床电路如图5所示。

开关矩阵采用MAX7000系列可编程逻辑器件实现,用来连接针床上所有探针,接收控制信号并将所寻址探针信号输出。

3 系统软件设计

系统软件运行于PC机平台上,通过USB总线对测试电路进行控制并接收测试电路测试数据,根据接收到的数据形成所测电路板电路连线表。现主要分析与电路测绘有关的测试电路控制程序:

(1)首先利用ADDR1寻址测试基准针床,每个针床都有特定地址码,如发送ADDR1=00000001,表示选中1号测试针床,以此为基准测试针床来对其它针床进行测试。

(2)号测试针床利用AD1总线对其上所有探针进行寻址,AD1总线寻址该针床的基准测试点,如发送AD1=00000001,表示寻址到1号探针,即1号探针连接D1端。

(3)以ADDR1所寻址针床为基准,利用ADDR2寻址所有针床,所寻址的针床利用AD2总线对其上探针进行寻址。

(4)以AD1总线所寻址探针为基准,对AD2总线所寻址探针进行遍历测试。

程序伪代码如下:

for(ADDR1=1 to 20) //假定共有20个测试针床,选定基准测试针床

{

for(AD1= 1 to 256) //假定每个针床上有256个探针和焊/点相连,选定基准测试焊点

{

for(ADDR2=1 to 20) //依次寻址所有针床

{

for(AD2= 1 to 256) //依次寻址测试针床上所有探针(焊点)

{

//测试电路测试函数

…

}

}

}

}

通过以上测试程序,即可实现每个探针(焊点)和其它所有探针(焊点)的遍历测试,从而获取电路板上每个焊点的连接情况。

通过电路板上元器件型号知识,利用此套测绘系统测绘的电路板连线表,结合相应PCB设计软件及人工干预,在某个引进装备上实现了未知电路板的测绘工作,得到了其电路原理图,为下一步的反设计工作奠定了基础。由于涉及知道产权问题,该系统仅应用于特殊领域电子设备。

for(ADDR2=1 to 20) //依次寻址所有针床

{

for(AD2= 1 to 256) //依次寻址测试针床上所有探针(焊点)

{

//测试电路测试函数

…

}

}

}

}

通过以上测试程序,即可实现每个探针(焊点)和其它所有探针(焊点)的遍历测试,从而获取电路板上每个焊点的连接情况。

通过电路板上元器件型号知识,利用此套测绘系统测绘的电路板连线表,结合相应PCB设计软件及人工干预,在某个引进装备上实现了未知电路板的测绘工作,得到了其电路原理图,为下一步的反设计工作奠定了基础。由于涉及知道产权问题,该系统仅应用于特殊领域电子设备。

编辑: 引用地址:未知电路板原理图测绘系统的设计与实现

(1)用万用表的欧姆档,对印制电路板上的各外露焊点和元器件管脚进行连接测试,即首先测量第一个焊点(或管脚)和第二、第三个焊点(或管脚)之间的电阻,直至测量完所有焊点和管脚,从而得到第一个焊点或管脚在电路板上的连接图。用同样的方法,再测第二个焊点(或管脚)与第三、第四个焊点(或管脚)之间的电阻,直至测量完所有焊点管脚,得到第二个焊点或管脚在电路板上的连接图。依次类推,可以得到电路板上各焊点和元器件管脚的连接关系(即网络图)。这种方法虽然能够得到电路板的网络图,但十分繁琐、效率低、差错率也高,因此应开发自动测绘设备。

(2)采用固定针床的办法进行测绘,对于每种电路板设计专门的测试针床,将专用针床与被测电路板的所有接点可靠接触,在计算机测试软件的控制下,通过专门的通道控制器可在较短时间内完成测试茉莉花和,而且能完成对多层电路板的测绘。但这种方式要求为每种被测对象设计一个专门的针床和测试软件,投放成本高、周期长。

综合以上两种方法的优点,根据常用的通路电阻测试法,设计了“柔性针床网络图测绘系统”,实现了灵活高效的测绘。连线表测试完成后,借助专建立的器件数据库,通过人工干预的方式即可完成电路原理图的绘制工作。

图2

2 系统硬件设计

2.1 系统总体结构

该系统由计算机、开关矩阵、柔性针床阵列和被测备件组成,其结构见图1。其中,柔性针床阵列通过柔性针与电路板上的所有节点可靠连接,开关矩阵实现通道的自动切换或顺序切换,柔性针床宽度仅能够覆盖一个电子芯片,这样通过多个针床,即可覆盖整个待测电路板。

测试时将电路板水平固定,在电路板上方和下方间距为2至3厘米处水平固定柔性针床,柔性针床的一面有密集分布的焊点,这些焊点通过长短可变的弹性探针与被测电路板一面上的外露焊点或元器件管脚相连。柔性针床的另一面由连线将各焊点与开关矩阵相连,电路板的另一面也进行相同的操作,从而将电路板的外露焊点或元器件管脚引到柔性针床上,通过计算机对开关矩阵进行控制,实现柔性针床上各节点之间的连接关系的自动测试。

2.2 测试电路结构组成

本系统采用自定义的总线结构,各柔性针床通过总线进行连接,由控制模块控制相互间的通信。测试电路通过USB总线接口与主机进行连接,如图2所示。

(1)用万用表的欧姆档,对印制电路板上的各外露焊点和元器件管脚进行连接测试,即首先测量第一个焊点(或管脚)和第二、第三个焊点(或管脚)之间的电阻,直至测量完所有焊点和管脚,从而得到第一个焊点或管脚在电路板上的连接图。用同样的方法,再测第二个焊点(或管脚)与第三、第四个焊点(或管脚)之间的电阻,直至测量完所有焊点管脚,得到第二个焊点或管脚在电路板上的连接图。依次类推,可以得到电路板上各焊点和元器件管脚的连接关系(即网络图)。这种方法虽然能够得到电路板的网络图,但十分繁琐、效率低、差错率也高,因此应开发自动测绘设备。

(2)采用固定针床的办法进行测绘,对于每种电路板设计专门的测试针床,将专用针床与被测电路板的所有接点可靠接触,在计算机测试软件的控制下,通过专门的通道控制器可在较短时间内完成测试茉莉花和,而且能完成对多层电路板的测绘。但这种方式要求为每种被测对象设计一个专门的针床和测试软件,投放成本高、周期长。

综合以上两种方法的优点,根据常用的通路电阻测试法,设计了“柔性针床网络图测绘系统”,实现了灵活高效的测绘。连线表测试完成后,借助专建立的器件数据库,通过人工干预的方式即可完成电路原理图的绘制工作。

图2

2 系统硬件设计

2.1 系统总体结构

该系统由计算机、开关矩阵、柔性针床阵列和被测备件组成,其结构见图1。其中,柔性针床阵列通过柔性针与电路板上的所有节点可靠连接,开关矩阵实现通道的自动切换或顺序切换,柔性针床宽度仅能够覆盖一个电子芯片,这样通过多个针床,即可覆盖整个待测电路板。

测试时将电路板水平固定,在电路板上方和下方间距为2至3厘米处水平固定柔性针床,柔性针床的一面有密集分布的焊点,这些焊点通过长短可变的弹性探针与被测电路板一面上的外露焊点或元器件管脚相连。柔性针床的另一面由连线将各焊点与开关矩阵相连,电路板的另一面也进行相同的操作,从而将电路板的外露焊点或元器件管脚引到柔性针床上,通过计算机对开关矩阵进行控制,实现柔性针床上各节点之间的连接关系的自动测试。

2.2 测试电路结构组成

本系统采用自定义的总线结构,各柔性针床通过总线进行连接,由控制模块控制相互间的通信。测试电路通过USB总线接口与主机进行连接,如图2所示。

其中,ADDR1和ADDR2为针床地址总线,控制模块通过发送相应的地址码实现针床的寻址。由于在测试时需要在针床本身和两个针床之间进行测试,只设计一套地址总线不能同时寻址两个针床,故设计了ADDR1和ADDR2两套地址总线,可同时实现对两个测试针床的寻址。

RD、WR为读使能和写使能总线,RD有效时,允许测试针床向控制模块发送数据,WR有效时,允许控制模块发送指令到各个针床,实现控制功能。

AD1、AD2为针床控针地址总线。由于在测试时,各个探针都需要和其它探针进行遍历测试,所以设计两套地址总线用来同时寻址两个不同的探针。AD1所寻址探针信号经数据线D1引出,AD2所寻址探针信号经数据线D2引出,通过测量D1与D2之间的电阻,就可以得到所对应的电路板焊点之间的连接情况。

在本设计中,PC机通过USB接口完成对测试机的控制,而测试数据又通过USB接口送回PC机进行分析,分析结果用于对UUT进行故障诊断。

本系统采用Cypress公司的AN2131QC作为控制器芯片。图3所示为AN2131QC的结构简化框图,USB总线收发器与USB总线引脚D+、D-相连,串行接口引擎用来对串行数据进行解码和译码、错误校验、位填充,并完成其它USB总线所需的信号,最终实现与USB总线接口的数据传输。通用微处理器采用增强型8051,与标准8051相比较,执行速度更快、功能更强大。在内部使用RAM作为程序代码和数据存储器,因此8051序列具有“软”特性,即:用户可以自动装载代码和数据来实现具体功能。

2.2.2 控制模块

控制模块用来完成各个针床的寻址、控制、测试以及数据的发送与接收功能。通过USB接口由主机下达控制命令及接收数据。控制模块结构如图4所示。

其中,ADDR1和ADDR2为针床地址总线,控制模块通过发送相应的地址码实现针床的寻址。由于在测试时需要在针床本身和两个针床之间进行测试,只设计一套地址总线不能同时寻址两个针床,故设计了ADDR1和ADDR2两套地址总线,可同时实现对两个测试针床的寻址。

RD、WR为读使能和写使能总线,RD有效时,允许测试针床向控制模块发送数据,WR有效时,允许控制模块发送指令到各个针床,实现控制功能。

AD1、AD2为针床控针地址总线。由于在测试时,各个探针都需要和其它探针进行遍历测试,所以设计两套地址总线用来同时寻址两个不同的探针。AD1所寻址探针信号经数据线D1引出,AD2所寻址探针信号经数据线D2引出,通过测量D1与D2之间的电阻,就可以得到所对应的电路板焊点之间的连接情况。

在本设计中,PC机通过USB接口完成对测试机的控制,而测试数据又通过USB接口送回PC机进行分析,分析结果用于对UUT进行故障诊断。

本系统采用Cypress公司的AN2131QC作为控制器芯片。图3所示为AN2131QC的结构简化框图,USB总线收发器与USB总线引脚D+、D-相连,串行接口引擎用来对串行数据进行解码和译码、错误校验、位填充,并完成其它USB总线所需的信号,最终实现与USB总线接口的数据传输。通用微处理器采用增强型8051,与标准8051相比较,执行速度更快、功能更强大。在内部使用RAM作为程序代码和数据存储器,因此8051序列具有“软”特性,即:用户可以自动装载代码和数据来实现具体功能。

2.2.2 控制模块

控制模块用来完成各个针床的寻址、控制、测试以及数据的发送与接收功能。通过USB接口由主机下达控制命令及接收数据。控制模块结构如图4所示。

系统控制芯片采用ALTERA公司的MAX7000系列可编程逻辑器件(CPLD),用来接收主机发送的控制信号,对测试电路进行控制;接收测试数据并上传到主机。当WR有效时,接收控制指令;当RD有效时,接收测试数据。在测试电路自定义总线上共有五种测试信号,所以采用三根控制信号线A、B、C,经译码即可输出不同的控制信号。电阻测试电路也位于控制模块中,负责对经D1和D2引出的电路板两个焊点(或管脚)进行测试,测试结果经A/D变换后由CPLD送到主机中。

2.2.3 测试针床

测试针床用来使用探针连接电路板各个焊点或管脚,并使用开关矩阵进行各个探针之间连接的自动顺序切换,从而实现各个焊点之间的互连测试。针床电路如图5所示。

开关矩阵采用MAX7000系列可编程逻辑器件实现,用来连接针床上所有探针,接收控制信号并将所寻址探针信号输出。

3 系统软件设计

系统软件运行于PC机平台上,通过USB总线对测试电路进行控制并接收测试电路测试数据,根据接收到的数据形成所测电路板电路连线表。现主要分析与电路测绘有关的测试电路控制程序:

(1)首先利用ADDR1寻址测试基准针床,每个针床都有特定地址码,如发送ADDR1=00000001,表示选中1号测试针床,以此为基准测试针床来对其它针床进行测试。

(2)号测试针床利用AD1总线对其上所有探针进行寻址,AD1总线寻址该针床的基准测试点,如发送AD1=00000001,表示寻址到1号探针,即1号探针连接D1端。

(3)以ADDR1所寻址针床为基准,利用ADDR2寻址所有针床,所寻址的针床利用AD2总线对其上探针进行寻址。

(4)以AD1总线所寻址探针为基准,对AD2总线所寻址探针进行遍历测试。

程序伪代码如下:

for(ADDR1=1 to 20) //假定共有20个测试针床,选定基准测试针床

{

for(AD1= 1 to 256) //假定每个针床上有256个探针和焊/点相连,选定基准测试焊点

{

系统控制芯片采用ALTERA公司的MAX7000系列可编程逻辑器件(CPLD),用来接收主机发送的控制信号,对测试电路进行控制;接收测试数据并上传到主机。当WR有效时,接收控制指令;当RD有效时,接收测试数据。在测试电路自定义总线上共有五种测试信号,所以采用三根控制信号线A、B、C,经译码即可输出不同的控制信号。电阻测试电路也位于控制模块中,负责对经D1和D2引出的电路板两个焊点(或管脚)进行测试,测试结果经A/D变换后由CPLD送到主机中。

2.2.3 测试针床

测试针床用来使用探针连接电路板各个焊点或管脚,并使用开关矩阵进行各个探针之间连接的自动顺序切换,从而实现各个焊点之间的互连测试。针床电路如图5所示。

开关矩阵采用MAX7000系列可编程逻辑器件实现,用来连接针床上所有探针,接收控制信号并将所寻址探针信号输出。

3 系统软件设计

系统软件运行于PC机平台上,通过USB总线对测试电路进行控制并接收测试电路测试数据,根据接收到的数据形成所测电路板电路连线表。现主要分析与电路测绘有关的测试电路控制程序:

(1)首先利用ADDR1寻址测试基准针床,每个针床都有特定地址码,如发送ADDR1=00000001,表示选中1号测试针床,以此为基准测试针床来对其它针床进行测试。

(2)号测试针床利用AD1总线对其上所有探针进行寻址,AD1总线寻址该针床的基准测试点,如发送AD1=00000001,表示寻址到1号探针,即1号探针连接D1端。

(3)以ADDR1所寻址针床为基准,利用ADDR2寻址所有针床,所寻址的针床利用AD2总线对其上探针进行寻址。

(4)以AD1总线所寻址探针为基准,对AD2总线所寻址探针进行遍历测试。

程序伪代码如下:

for(ADDR1=1 to 20) //假定共有20个测试针床,选定基准测试针床

{

for(AD1= 1 to 256) //假定每个针床上有256个探针和焊/点相连,选定基准测试焊点

{

for(ADDR2=1 to 20) //依次寻址所有针床

{

for(AD2= 1 to 256) //依次寻址测试针床上所有探针(焊点)

{

//测试电路测试函数

…

}

}

}

}

通过以上测试程序,即可实现每个探针(焊点)和其它所有探针(焊点)的遍历测试,从而获取电路板上每个焊点的连接情况。

通过电路板上元器件型号知识,利用此套测绘系统测绘的电路板连线表,结合相应PCB设计软件及人工干预,在某个引进装备上实现了未知电路板的测绘工作,得到了其电路原理图,为下一步的反设计工作奠定了基础。由于涉及知道产权问题,该系统仅应用于特殊领域电子设备。

for(ADDR2=1 to 20) //依次寻址所有针床

{

for(AD2= 1 to 256) //依次寻址测试针床上所有探针(焊点)

{

//测试电路测试函数

…

}

}

}

}

通过以上测试程序,即可实现每个探针(焊点)和其它所有探针(焊点)的遍历测试,从而获取电路板上每个焊点的连接情况。

通过电路板上元器件型号知识,利用此套测绘系统测绘的电路板连线表,结合相应PCB设计软件及人工干预,在某个引进装备上实现了未知电路板的测绘工作,得到了其电路原理图,为下一步的反设计工作奠定了基础。由于涉及知道产权问题,该系统仅应用于特殊领域电子设备。

上一篇:用STATECAD快速设计有限状态机

下一篇:基于FPGA的高级数据加密AES中的字节替换设计

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 MC1458CD

MC1458CD

京公网安备 11010802033920号

京公网安备 11010802033920号