摘要:介绍了应用FPGA技术进行帧同步器设计的实现原理、系统框图及设计中需要注意的问题,给出了用VHDL描述的几个模块的源代码。

关键词:数字复接;帧同步器;FPGA

在数字通信网中,为了提高传输效率,常常需要将若干路低速数字信号合并成一路高速数字信号,以便通过高速信道进行传输。实现此功能的设备称为数字复接系统。

数字复接系统包括发送端和接收端两部分,通常称为复接器和分接器。为了使分接器的帧状态相对于复接器的帧状态获得并保持相位关系,以便正确地实施分接,数字复接系统在发送端把低速数字信号合并为高速信号的同时,往往还要插入用于同步的帧同步码;而在接收端,分接器要把发送端数字信号中的帧同步码检测出来并去除,然后才能分解为原来的支路数字信号,其中完成帧同步码检出这一功能的单元称为数字复接系统的帧同步器。在合路数字信号中,帧同步码能否被准确识别直接决定了能否正确的分接出各个支路信号。

目前,FPGA已在通信领域得到了广泛应用,这也为数字复接技术提供了灵活且可移植的设计方法。本文将介绍数字复接系统中帧同步器的工作原理和FPGA的设计流程,同时将给出具体实现方法以及设计中需要注意的问题。

1 帧同步器原理

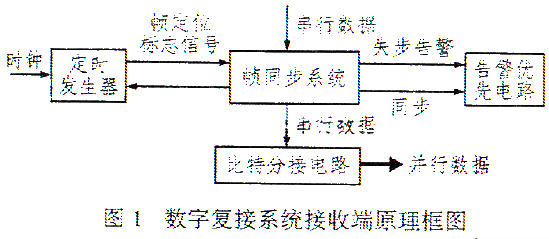

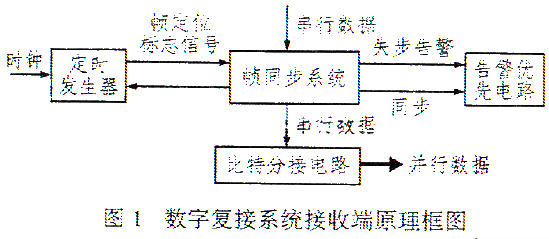

图1是笔者设计的一种数字复接系统接收端的原理框图。其中,定时发生器为帧同步系统提供帧定位标志信号;帧同步系统用来检测所传输数据码流中的帧同步码;比特分接电路用于把串行数据转换成并行数据;告警优先电路用来指示当前系统处于同步状态还是失步状态。

在复接系统的发送端,可以将帧同步码集中插在每帧的开头位置;也可以将其分散插在各个支路的前面。前者称为帧同步码集中插入法,后者称为分散插入法。图2所示是使用集中插入法时,接收端帧同步器的原理框图。

通常帧同步电路有两种状态,同步未建立时系统处于搜捕态,建立后则处于保持态;保持态下的同步保护措施称为前方保护,搜捕态下的同步保护措施称为后方保护。帧同步系统电路设计的原则是:同步建立时,假同步概率要小;同步建立后,漏同步概率要小。

图2中的帧同步器前端是由8位移位寄存器组成的帧同步码检测电路,当输入码流中无同步码组时,检测电路输出始终为1,这时定时发生器关闭,比较/计数电路(由a、b、c、d四个D触发器组成)不工作,系统处于搜捕态;一旦在输入码流中检测到同步码组,检测电路输出就为0,定时发生器开始产生比较/计数电路的计数时钟,计数器开始后方保护计数;如果随后在规定时刻上又连续α-1次(图中α=3)检测到帧同步码组,则系统同步,帧同步器进入保持态。在同步保持状态下,一旦帧同步码检测电路在规定时刻有一次未发现帧同步码,比较/计数电路便开始前方保护计数,如果随后在规定时刻上又连续β-1次(图中β=4)检测不到帧同步码,则定时发生器关闭,帧同步器由保持态进入搜捕态,重新捕捉帧同步码。

值得注意的是,如果搜捕中第一次检测到的是假的同步码组(即在传送的码元中有一段数据与帧同步码相同,但其出现的位置不是在规定的同步码位置上),定时发生器仍不工作,此时帧同步码检测电路将继续搜捕,直至检测到真正的帧同步码为止。

在复接系统的发送端,可以将帧同步码集中插在每帧的开头位置;也可以将其分散插在各个支路的前面。前者称为帧同步码集中插入法,后者称为分散插入法。图2所示是使用集中插入法时,接收端帧同步器的原理框图。

通常帧同步电路有两种状态,同步未建立时系统处于搜捕态,建立后则处于保持态;保持态下的同步保护措施称为前方保护,搜捕态下的同步保护措施称为后方保护。帧同步系统电路设计的原则是:同步建立时,假同步概率要小;同步建立后,漏同步概率要小。

图2中的帧同步器前端是由8位移位寄存器组成的帧同步码检测电路,当输入码流中无同步码组时,检测电路输出始终为1,这时定时发生器关闭,比较/计数电路(由a、b、c、d四个D触发器组成)不工作,系统处于搜捕态;一旦在输入码流中检测到同步码组,检测电路输出就为0,定时发生器开始产生比较/计数电路的计数时钟,计数器开始后方保护计数;如果随后在规定时刻上又连续α-1次(图中α=3)检测到帧同步码组,则系统同步,帧同步器进入保持态。在同步保持状态下,一旦帧同步码检测电路在规定时刻有一次未发现帧同步码,比较/计数电路便开始前方保护计数,如果随后在规定时刻上又连续β-1次(图中β=4)检测不到帧同步码,则定时发生器关闭,帧同步器由保持态进入搜捕态,重新捕捉帧同步码。

值得注意的是,如果搜捕中第一次检测到的是假的同步码组(即在传送的码元中有一段数据与帧同步码相同,但其出现的位置不是在规定的同步码位置上),定时发生器仍不工作,此时帧同步码检测电路将继续搜捕,直至检测到真正的帧同步码为止。

2 FPGA设计与实现

在FPGA设计中,帧同步器主要由帧同步码检出、保护和校核计数、帧失步调整控制门三部分组成。图3中的虚线框部分就是帧同步器。下面给出用VHDL语言设计帧同步器的几个进程模块。

2.1 同步码检测电路

帧同步码检测电路由8位移位寄存器组成,这里把帧同步码设定为8位最佳码“10111000”,当电路检测到输入码流中有帧同步码组时,检测电路将输出“0”;否则将输出“1”。输出结果将作为定时发生器的控制信号之一。具体程序如下(其中d in为串行输入码流,yf1是检测电路输出的结果):

process(clk)

begin

if ( clk'event and clk=′1′) then

output<=d_in&output(7 down to 1);

end if;

end process p2;

yfl<= not((not output(7))and (not output(6)) and ( not output(5)) and output(4) and output(3) and output(2) and (not output(1))and output(0));

--″10111000″

2.2 定时发生器

定时发生器可对时钟clk进行n分频,分频后的周期等于帧周期(一帧有n个码元,这里n=88)。 定时发生器主要用来产生帧定位标志信号,该信号是产生比较/计数电路计数时钟clk yf5的信号之一。在下面的程序中,clk为时钟,yf4为控制门输出信号,用于控制定时发生器的打开和关闭,f8为帧定位标志信号。具体程序如下:

process(reset,clk,yf4)

begin

if reset=′1′ then

f8<=′1′;

elsif clk'event and clk=′0′ then

if yf4=′0′then

countf<=″0000000″

f8<=′1′;

elsif countf=″1010111″ then

countf<=″0000000″;

f8<=′1′;

else

countf<=countf+1;

f8<=′0′;

end if;

end if;

end process

2.3 控制门

控制门主要由RS触发器构成,用来判断系统是同步还是失步。同步时,RS触发器的Q端输出1,Q 端输出0;失步时,Q端输出0,Q 端输出1。Q端可作为进一步分接数据的控制信号, Q 端输出结果可打开或关闭控制门yf4。具体程序如下:

process(clk)

begin

if clk'event and clk=′1′ then

rs<=(R&S);

case rs is

when″01″=> Q1<= ′1′;

Q<=′0′;

when ″10″=> Q1<= ′0′;

Q<=′1′;

when ″11″=> Q<=RSq;

Q1<= RSq1;

when others => null;

end case;

end if;

end process

2 FPGA设计与实现

在FPGA设计中,帧同步器主要由帧同步码检出、保护和校核计数、帧失步调整控制门三部分组成。图3中的虚线框部分就是帧同步器。下面给出用VHDL语言设计帧同步器的几个进程模块。

2.1 同步码检测电路

帧同步码检测电路由8位移位寄存器组成,这里把帧同步码设定为8位最佳码“10111000”,当电路检测到输入码流中有帧同步码组时,检测电路将输出“0”;否则将输出“1”。输出结果将作为定时发生器的控制信号之一。具体程序如下(其中d in为串行输入码流,yf1是检测电路输出的结果):

process(clk)

begin

if ( clk'event and clk=′1′) then

output<=d_in&output(7 down to 1);

end if;

end process p2;

yfl<= not((not output(7))and (not output(6)) and ( not output(5)) and output(4) and output(3) and output(2) and (not output(1))and output(0));

--″10111000″

2.2 定时发生器

定时发生器可对时钟clk进行n分频,分频后的周期等于帧周期(一帧有n个码元,这里n=88)。 定时发生器主要用来产生帧定位标志信号,该信号是产生比较/计数电路计数时钟clk yf5的信号之一。在下面的程序中,clk为时钟,yf4为控制门输出信号,用于控制定时发生器的打开和关闭,f8为帧定位标志信号。具体程序如下:

process(reset,clk,yf4)

begin

if reset=′1′ then

f8<=′1′;

elsif clk'event and clk=′0′ then

if yf4=′0′then

countf<=″0000000″

f8<=′1′;

elsif countf=″1010111″ then

countf<=″0000000″;

f8<=′1′;

else

countf<=countf+1;

f8<=′0′;

end if;

end if;

end process

2.3 控制门

控制门主要由RS触发器构成,用来判断系统是同步还是失步。同步时,RS触发器的Q端输出1,Q 端输出0;失步时,Q端输出0,Q 端输出1。Q端可作为进一步分接数据的控制信号, Q 端输出结果可打开或关闭控制门yf4。具体程序如下:

process(clk)

begin

if clk'event and clk=′1′ then

rs<=(R&S);

case rs is

when″01″=> Q1<= ′1′;

Q<=′0′;

when ″10″=> Q1<= ′0′;

Q<=′1′;

when ″11″=> Q<=RSq;

Q1<= RSq1;

when others => null;

end case;

end if;

end process

2.4 比较/计数电路

比较/计数电路用于完成搜捕态与保持态下的计数。搜捕态下,当帧同步码检测电路连续3α=3次捕获到同相位的正确帧同步码时,帧同步器将进入保持态;而在保持态下,如果帧同步码检测电路连续4(β=4)次未检测到帧同步码,帧同步器将进入搜捕态。程序如下(其中,比较/计数电路计数时钟clk_yf5由帧定位标志信号f8和时钟clk产生,yf2为输出保持结果,yf3为输出搜捕结果):

clk_yf5<=not (f8 and clk) ;产生比较/计数电路所需时钟

process(reset,clk_yf5) ;比较/计数电路

begin

if reset=′1′ then

qa<=′0′;qb<=′0′;qc<=′0′;

qa1<=′1′;qb1<=′1′;qc1<=′1′;qd1<=′1′;

--protel<=″0000″;

elsif clk_yf5'event and clk_yf5=′1′ then

qa<=qe1;

qa1<=qe;

qb<=qa;

qb1<=qa1;

qc<=qb;

qc1<= qb1;

qd1<=qc1;

end if;

end process;

yf2<=not(qa1 and qb1 and qc1 and qd1);

yf3<=not(qa and qb and qc);

3 设计中需要注意的问题

设计中要严格控制定时发生器产生时钟clk_yf5的宽度,以避免出现不定状态。如果帧定位标志信号f8与帧同步检出电路都是由时钟clk的上升沿或下降沿产生的,那么clk_yf5脉冲中就会出现一小段不定状态,而在这段时间里帧同步系统是不能正常工作的。所以,帧定位标志信号f8由时钟clk的下降沿触发产生,帧同步检出电路则由时钟clk的上升沿触发,这样便可以得到一半码元宽度的时钟clk_yf5脉冲,且脉冲中不存在不定状态。

设计中应多采用同步时序电路来实现各个进程模块的功能,以免电路中产生毛刺。

4 结束语

本设计选用Xilinx公司的ISE5.2作为硬件开发平台,并采用VHDL编程语言。文中程序已通过了综合实验,并进行了功能仿真和时序仿真,仿真结果正确。在硬件实现与调试过程中,将程序下载到Xilinx公司的VIRTEX芯片,然后经过整体调试,最终实现了数字复接系统中帧同步器的设计。

2.4 比较/计数电路

比较/计数电路用于完成搜捕态与保持态下的计数。搜捕态下,当帧同步码检测电路连续3α=3次捕获到同相位的正确帧同步码时,帧同步器将进入保持态;而在保持态下,如果帧同步码检测电路连续4(β=4)次未检测到帧同步码,帧同步器将进入搜捕态。程序如下(其中,比较/计数电路计数时钟clk_yf5由帧定位标志信号f8和时钟clk产生,yf2为输出保持结果,yf3为输出搜捕结果):

clk_yf5<=not (f8 and clk) ;产生比较/计数电路所需时钟

process(reset,clk_yf5) ;比较/计数电路

begin

if reset=′1′ then

qa<=′0′;qb<=′0′;qc<=′0′;

qa1<=′1′;qb1<=′1′;qc1<=′1′;qd1<=′1′;

--protel<=″0000″;

elsif clk_yf5'event and clk_yf5=′1′ then

qa<=qe1;

qa1<=qe;

qb<=qa;

qb1<=qa1;

qc<=qb;

qc1<= qb1;

qd1<=qc1;

end if;

end process;

yf2<=not(qa1 and qb1 and qc1 and qd1);

yf3<=not(qa and qb and qc);

3 设计中需要注意的问题

设计中要严格控制定时发生器产生时钟clk_yf5的宽度,以避免出现不定状态。如果帧定位标志信号f8与帧同步检出电路都是由时钟clk的上升沿或下降沿产生的,那么clk_yf5脉冲中就会出现一小段不定状态,而在这段时间里帧同步系统是不能正常工作的。所以,帧定位标志信号f8由时钟clk的下降沿触发产生,帧同步检出电路则由时钟clk的上升沿触发,这样便可以得到一半码元宽度的时钟clk_yf5脉冲,且脉冲中不存在不定状态。

设计中应多采用同步时序电路来实现各个进程模块的功能,以免电路中产生毛刺。

4 结束语

本设计选用Xilinx公司的ISE5.2作为硬件开发平台,并采用VHDL编程语言。文中程序已通过了综合实验,并进行了功能仿真和时序仿真,仿真结果正确。在硬件实现与调试过程中,将程序下载到Xilinx公司的VIRTEX芯片,然后经过整体调试,最终实现了数字复接系统中帧同步器的设计。

编辑: 引用地址:基于FPGA的数字复接系统帧同步器设计与实现

在复接系统的发送端,可以将帧同步码集中插在每帧的开头位置;也可以将其分散插在各个支路的前面。前者称为帧同步码集中插入法,后者称为分散插入法。图2所示是使用集中插入法时,接收端帧同步器的原理框图。

通常帧同步电路有两种状态,同步未建立时系统处于搜捕态,建立后则处于保持态;保持态下的同步保护措施称为前方保护,搜捕态下的同步保护措施称为后方保护。帧同步系统电路设计的原则是:同步建立时,假同步概率要小;同步建立后,漏同步概率要小。

图2中的帧同步器前端是由8位移位寄存器组成的帧同步码检测电路,当输入码流中无同步码组时,检测电路输出始终为1,这时定时发生器关闭,比较/计数电路(由a、b、c、d四个D触发器组成)不工作,系统处于搜捕态;一旦在输入码流中检测到同步码组,检测电路输出就为0,定时发生器开始产生比较/计数电路的计数时钟,计数器开始后方保护计数;如果随后在规定时刻上又连续α-1次(图中α=3)检测到帧同步码组,则系统同步,帧同步器进入保持态。在同步保持状态下,一旦帧同步码检测电路在规定时刻有一次未发现帧同步码,比较/计数电路便开始前方保护计数,如果随后在规定时刻上又连续β-1次(图中β=4)检测不到帧同步码,则定时发生器关闭,帧同步器由保持态进入搜捕态,重新捕捉帧同步码。

值得注意的是,如果搜捕中第一次检测到的是假的同步码组(即在传送的码元中有一段数据与帧同步码相同,但其出现的位置不是在规定的同步码位置上),定时发生器仍不工作,此时帧同步码检测电路将继续搜捕,直至检测到真正的帧同步码为止。

在复接系统的发送端,可以将帧同步码集中插在每帧的开头位置;也可以将其分散插在各个支路的前面。前者称为帧同步码集中插入法,后者称为分散插入法。图2所示是使用集中插入法时,接收端帧同步器的原理框图。

通常帧同步电路有两种状态,同步未建立时系统处于搜捕态,建立后则处于保持态;保持态下的同步保护措施称为前方保护,搜捕态下的同步保护措施称为后方保护。帧同步系统电路设计的原则是:同步建立时,假同步概率要小;同步建立后,漏同步概率要小。

图2中的帧同步器前端是由8位移位寄存器组成的帧同步码检测电路,当输入码流中无同步码组时,检测电路输出始终为1,这时定时发生器关闭,比较/计数电路(由a、b、c、d四个D触发器组成)不工作,系统处于搜捕态;一旦在输入码流中检测到同步码组,检测电路输出就为0,定时发生器开始产生比较/计数电路的计数时钟,计数器开始后方保护计数;如果随后在规定时刻上又连续α-1次(图中α=3)检测到帧同步码组,则系统同步,帧同步器进入保持态。在同步保持状态下,一旦帧同步码检测电路在规定时刻有一次未发现帧同步码,比较/计数电路便开始前方保护计数,如果随后在规定时刻上又连续β-1次(图中β=4)检测不到帧同步码,则定时发生器关闭,帧同步器由保持态进入搜捕态,重新捕捉帧同步码。

值得注意的是,如果搜捕中第一次检测到的是假的同步码组(即在传送的码元中有一段数据与帧同步码相同,但其出现的位置不是在规定的同步码位置上),定时发生器仍不工作,此时帧同步码检测电路将继续搜捕,直至检测到真正的帧同步码为止。

2 FPGA设计与实现

在FPGA设计中,帧同步器主要由帧同步码检出、保护和校核计数、帧失步调整控制门三部分组成。图3中的虚线框部分就是帧同步器。下面给出用VHDL语言设计帧同步器的几个进程模块。

2.1 同步码检测电路

帧同步码检测电路由8位移位寄存器组成,这里把帧同步码设定为8位最佳码“10111000”,当电路检测到输入码流中有帧同步码组时,检测电路将输出“0”;否则将输出“1”。输出结果将作为定时发生器的控制信号之一。具体程序如下(其中d in为串行输入码流,yf1是检测电路输出的结果):

process(clk)

begin

if ( clk'event and clk=′1′) then

output<=d_in&output(7 down to 1);

end if;

end process p2;

yfl<= not((not output(7))and (not output(6)) and ( not output(5)) and output(4) and output(3) and output(2) and (not output(1))and output(0));

--″10111000″

2.2 定时发生器

定时发生器可对时钟clk进行n分频,分频后的周期等于帧周期(一帧有n个码元,这里n=88)。 定时发生器主要用来产生帧定位标志信号,该信号是产生比较/计数电路计数时钟clk yf5的信号之一。在下面的程序中,clk为时钟,yf4为控制门输出信号,用于控制定时发生器的打开和关闭,f8为帧定位标志信号。具体程序如下:

process(reset,clk,yf4)

begin

if reset=′1′ then

f8<=′1′;

elsif clk'event and clk=′0′ then

if yf4=′0′then

countf<=″0000000″

f8<=′1′;

elsif countf=″1010111″ then

countf<=″0000000″;

f8<=′1′;

else

countf<=countf+1;

f8<=′0′;

end if;

end if;

end process

2.3 控制门

控制门主要由RS触发器构成,用来判断系统是同步还是失步。同步时,RS触发器的Q端输出1,Q 端输出0;失步时,Q端输出0,Q 端输出1。Q端可作为进一步分接数据的控制信号, Q 端输出结果可打开或关闭控制门yf4。具体程序如下:

process(clk)

begin

if clk'event and clk=′1′ then

rs<=(R&S);

case rs is

when″01″=> Q1<= ′1′;

Q<=′0′;

when ″10″=> Q1<= ′0′;

Q<=′1′;

when ″11″=> Q<=RSq;

Q1<= RSq1;

when others => null;

end case;

end if;

end process

2 FPGA设计与实现

在FPGA设计中,帧同步器主要由帧同步码检出、保护和校核计数、帧失步调整控制门三部分组成。图3中的虚线框部分就是帧同步器。下面给出用VHDL语言设计帧同步器的几个进程模块。

2.1 同步码检测电路

帧同步码检测电路由8位移位寄存器组成,这里把帧同步码设定为8位最佳码“10111000”,当电路检测到输入码流中有帧同步码组时,检测电路将输出“0”;否则将输出“1”。输出结果将作为定时发生器的控制信号之一。具体程序如下(其中d in为串行输入码流,yf1是检测电路输出的结果):

process(clk)

begin

if ( clk'event and clk=′1′) then

output<=d_in&output(7 down to 1);

end if;

end process p2;

yfl<= not((not output(7))and (not output(6)) and ( not output(5)) and output(4) and output(3) and output(2) and (not output(1))and output(0));

--″10111000″

2.2 定时发生器

定时发生器可对时钟clk进行n分频,分频后的周期等于帧周期(一帧有n个码元,这里n=88)。 定时发生器主要用来产生帧定位标志信号,该信号是产生比较/计数电路计数时钟clk yf5的信号之一。在下面的程序中,clk为时钟,yf4为控制门输出信号,用于控制定时发生器的打开和关闭,f8为帧定位标志信号。具体程序如下:

process(reset,clk,yf4)

begin

if reset=′1′ then

f8<=′1′;

elsif clk'event and clk=′0′ then

if yf4=′0′then

countf<=″0000000″

f8<=′1′;

elsif countf=″1010111″ then

countf<=″0000000″;

f8<=′1′;

else

countf<=countf+1;

f8<=′0′;

end if;

end if;

end process

2.3 控制门

控制门主要由RS触发器构成,用来判断系统是同步还是失步。同步时,RS触发器的Q端输出1,Q 端输出0;失步时,Q端输出0,Q 端输出1。Q端可作为进一步分接数据的控制信号, Q 端输出结果可打开或关闭控制门yf4。具体程序如下:

process(clk)

begin

if clk'event and clk=′1′ then

rs<=(R&S);

case rs is

when″01″=> Q1<= ′1′;

Q<=′0′;

when ″10″=> Q1<= ′0′;

Q<=′1′;

when ″11″=> Q<=RSq;

Q1<= RSq1;

when others => null;

end case;

end if;

end process

2.4 比较/计数电路

比较/计数电路用于完成搜捕态与保持态下的计数。搜捕态下,当帧同步码检测电路连续3α=3次捕获到同相位的正确帧同步码时,帧同步器将进入保持态;而在保持态下,如果帧同步码检测电路连续4(β=4)次未检测到帧同步码,帧同步器将进入搜捕态。程序如下(其中,比较/计数电路计数时钟clk_yf5由帧定位标志信号f8和时钟clk产生,yf2为输出保持结果,yf3为输出搜捕结果):

clk_yf5<=not (f8 and clk) ;产生比较/计数电路所需时钟

process(reset,clk_yf5) ;比较/计数电路

begin

if reset=′1′ then

qa<=′0′;qb<=′0′;qc<=′0′;

qa1<=′1′;qb1<=′1′;qc1<=′1′;qd1<=′1′;

--protel<=″0000″;

elsif clk_yf5'event and clk_yf5=′1′ then

qa<=qe1;

qa1<=qe;

qb<=qa;

qb1<=qa1;

qc<=qb;

qc1<= qb1;

qd1<=qc1;

end if;

end process;

yf2<=not(qa1 and qb1 and qc1 and qd1);

yf3<=not(qa and qb and qc);

3 设计中需要注意的问题

设计中要严格控制定时发生器产生时钟clk_yf5的宽度,以避免出现不定状态。如果帧定位标志信号f8与帧同步检出电路都是由时钟clk的上升沿或下降沿产生的,那么clk_yf5脉冲中就会出现一小段不定状态,而在这段时间里帧同步系统是不能正常工作的。所以,帧定位标志信号f8由时钟clk的下降沿触发产生,帧同步检出电路则由时钟clk的上升沿触发,这样便可以得到一半码元宽度的时钟clk_yf5脉冲,且脉冲中不存在不定状态。

设计中应多采用同步时序电路来实现各个进程模块的功能,以免电路中产生毛刺。

4 结束语

本设计选用Xilinx公司的ISE5.2作为硬件开发平台,并采用VHDL编程语言。文中程序已通过了综合实验,并进行了功能仿真和时序仿真,仿真结果正确。在硬件实现与调试过程中,将程序下载到Xilinx公司的VIRTEX芯片,然后经过整体调试,最终实现了数字复接系统中帧同步器的设计。

2.4 比较/计数电路

比较/计数电路用于完成搜捕态与保持态下的计数。搜捕态下,当帧同步码检测电路连续3α=3次捕获到同相位的正确帧同步码时,帧同步器将进入保持态;而在保持态下,如果帧同步码检测电路连续4(β=4)次未检测到帧同步码,帧同步器将进入搜捕态。程序如下(其中,比较/计数电路计数时钟clk_yf5由帧定位标志信号f8和时钟clk产生,yf2为输出保持结果,yf3为输出搜捕结果):

clk_yf5<=not (f8 and clk) ;产生比较/计数电路所需时钟

process(reset,clk_yf5) ;比较/计数电路

begin

if reset=′1′ then

qa<=′0′;qb<=′0′;qc<=′0′;

qa1<=′1′;qb1<=′1′;qc1<=′1′;qd1<=′1′;

--protel<=″0000″;

elsif clk_yf5'event and clk_yf5=′1′ then

qa<=qe1;

qa1<=qe;

qb<=qa;

qb1<=qa1;

qc<=qb;

qc1<= qb1;

qd1<=qc1;

end if;

end process;

yf2<=not(qa1 and qb1 and qc1 and qd1);

yf3<=not(qa and qb and qc);

3 设计中需要注意的问题

设计中要严格控制定时发生器产生时钟clk_yf5的宽度,以避免出现不定状态。如果帧定位标志信号f8与帧同步检出电路都是由时钟clk的上升沿或下降沿产生的,那么clk_yf5脉冲中就会出现一小段不定状态,而在这段时间里帧同步系统是不能正常工作的。所以,帧定位标志信号f8由时钟clk的下降沿触发产生,帧同步检出电路则由时钟clk的上升沿触发,这样便可以得到一半码元宽度的时钟clk_yf5脉冲,且脉冲中不存在不定状态。

设计中应多采用同步时序电路来实现各个进程模块的功能,以免电路中产生毛刺。

4 结束语

本设计选用Xilinx公司的ISE5.2作为硬件开发平台,并采用VHDL编程语言。文中程序已通过了综合实验,并进行了功能仿真和时序仿真,仿真结果正确。在硬件实现与调试过程中,将程序下载到Xilinx公司的VIRTEX芯片,然后经过整体调试,最终实现了数字复接系统中帧同步器的设计。

上一篇:PicoBlaze处理器IP Core的原理与应用

下一篇:基于FPGA的直接数字频率合成技术设计

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TS472IQT

TS472IQT

京公网安备 11010802033920号

京公网安备 11010802033920号