1.中断的基本概念

当单片机正在执行程序时,出现了某些特殊状况,例如定时时间到、有键盘信号输入等,此时CPU须要暂时停止当前的程序,而转去执行处理这些事件的程序,待执行完这些特定的程序之后,再返回到原先的程序去执行,这就形成了一次“中断”。“中断”加强了单片机处理突发事件的能力,如果没有中断功能,对可能发生的特殊状况的处理就必须采用定时查询,这样就会浪费大量的CPU时间。

因此,中断是单片机中很重要的一个概念,是提高工作效率的重要功能,中断系统功能的好坏是衡量单片机功能的重要指标。单片机的“中断源”与单片机包含的外围设备有很大的关系,所谓“中断源”就是引起中断的原因或根源,就是中断请求的来源。16F873/876内部集成了12个外围设备。

外围设备在工作过程中,都需要CPU参与控制、协调或交换数据等服务,而CPU正是通过中断技术使得这些外围设备协调工作的。PIC单片机作一次中断处理的过程如下,当某一中断源发出中断请求时:

①假如CPU正在执行更重要的任务,则可采用屏蔽的方法暂时不响应该中断请求;

②如果可以响应该中断请求,则CPU执行完当前指令后,必须把断点处的程序计数器PC的值(即下一条指令的地址)压入堆栈保存起来(断点保护),也可以把一些的重要寄存器内容也保护起来(现场保护)。然后再转移到相应的中断服务子程序中执行。

③在中断服务子程序中,首先必须确定发出中断请求的中断源,然后再跳转到与该中断源相对应的程序分支中去执行中断服务程序。

④当中断服务程序执行毕后,必须先恢复被保护的寄存器的值(现场恢复),再将程序计数器PC的值从堆栈中恢复(断点恢复) ,使CPU返回断点处继续执行被中断的程序。

2.PIC16F876的中断源

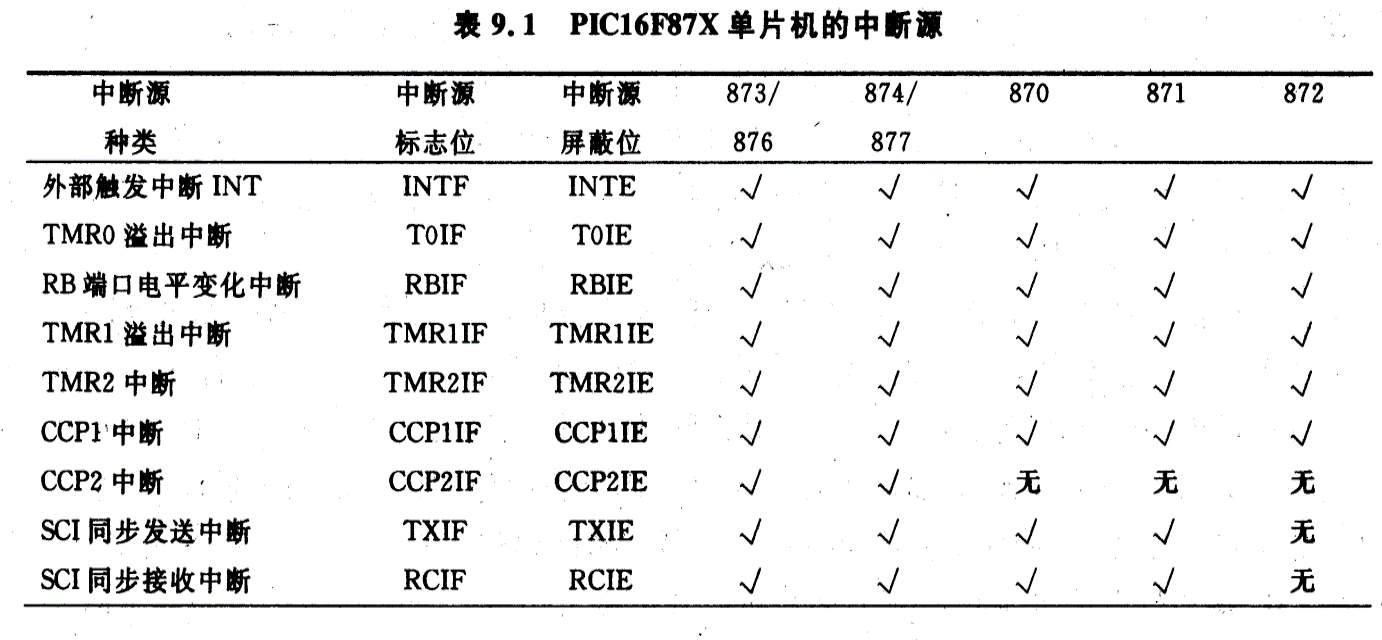

PIC16F876单片机具备的中断源如下表所示:

从上表可看出,各中断源基本上都与各个外围设备模块相对应的:多数的外围设备对应着一个中断源(如定时/计数器TMR0),也有的外围设备对应二个中断源(如SCI同步/异步接收/发送器USART);有的外围设备没有中断源与之对应(如输入/输出端口 RA和RC);也有的中断源没有外围设备与之对应(例如外部中断源INT)。

每一种中断源对应了一个中断标志位,记为XXXF,以及一个中断屏蔽位或叫中断使能位,记为XXXE。中断源产生的中断信号能否到达CPU,都受控于相应的中断屏蔽位。 每个中断源申请中断时,其中断标志位会自动置位,中断标志位的清0是由用户程序完成的;而每个中断屏蔽位的置位和清位均由用户程序完成。

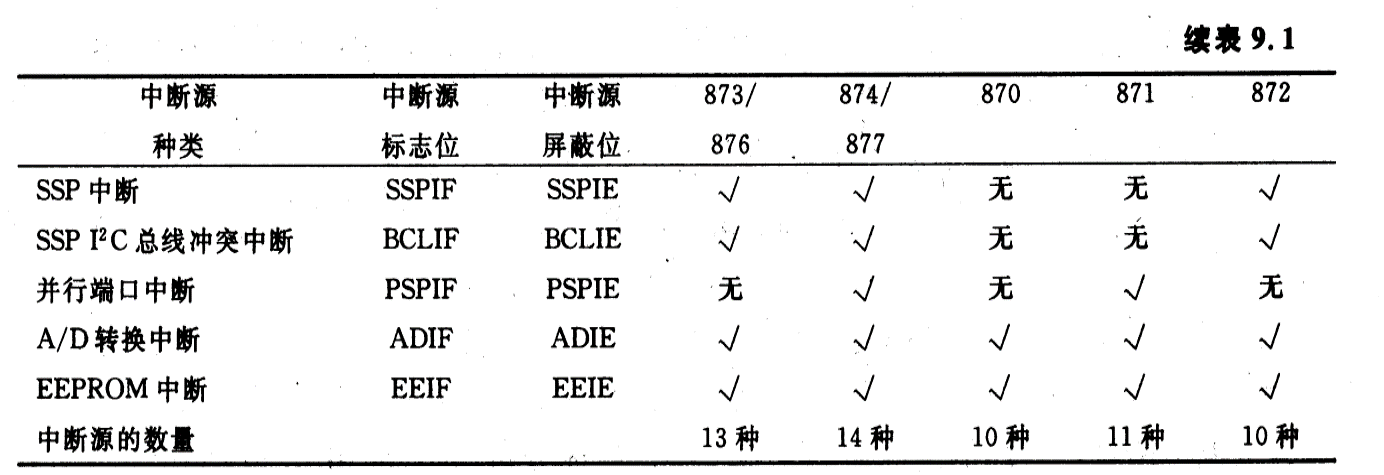

PIC16F876单片机的中断系统的逻辑电路如图:

图中全部的的14个中断源按两个梯队并列排开,第一梯队中只安排了3个中断源,其余的中断源全部安排到第二梯队中。所有的中断源都受“全局中断屏蔽位”(也称总屏蔽位)GIE的控制;第一梯队的中断源不仅受GIE的控制,还要受各自中断屏蔽位的控制;第二梯队的中断源不仅受到GIE和各自中断屏蔽位的控制,还要受到一个外设中断屏蔽位PEIE的控制。

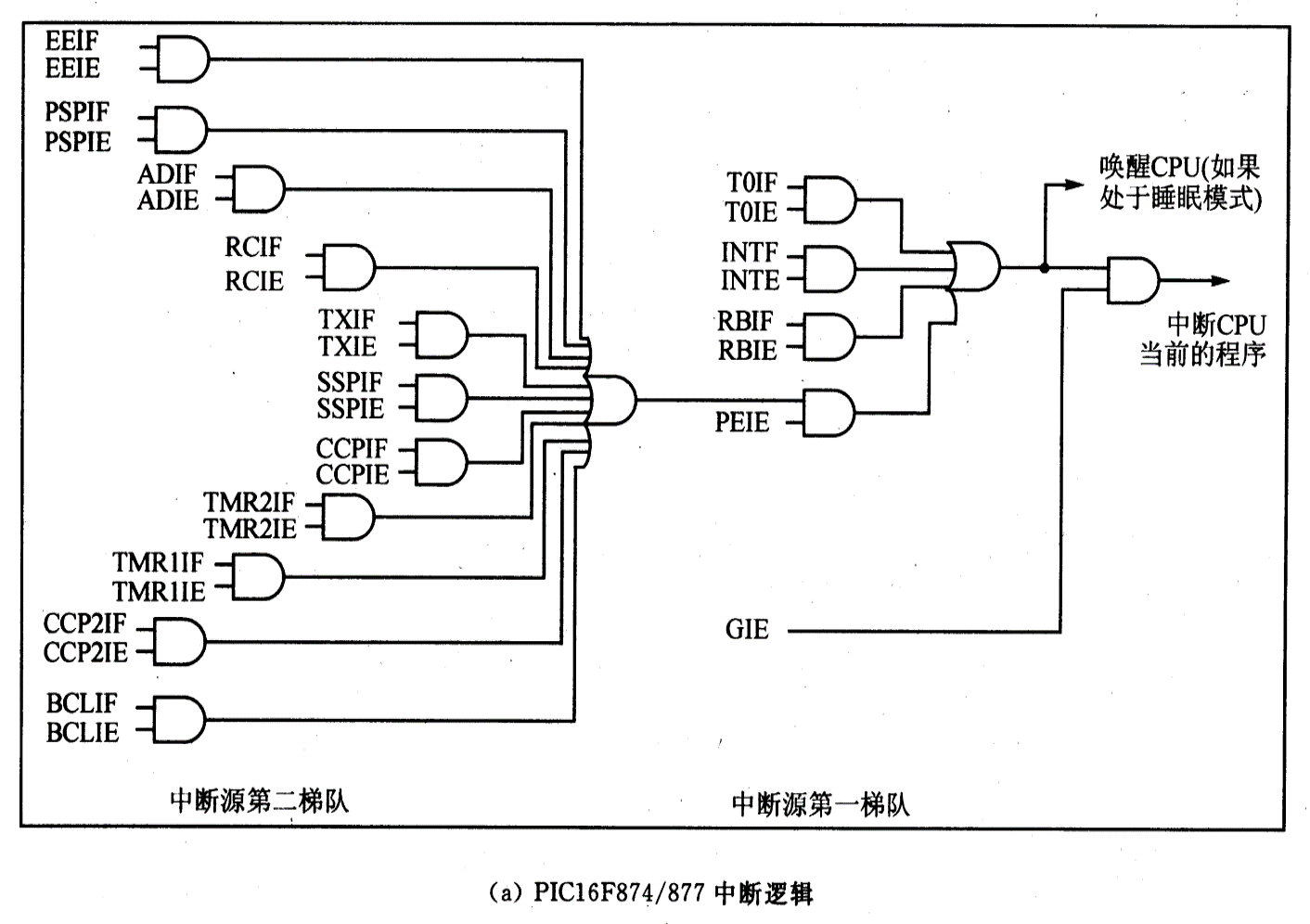

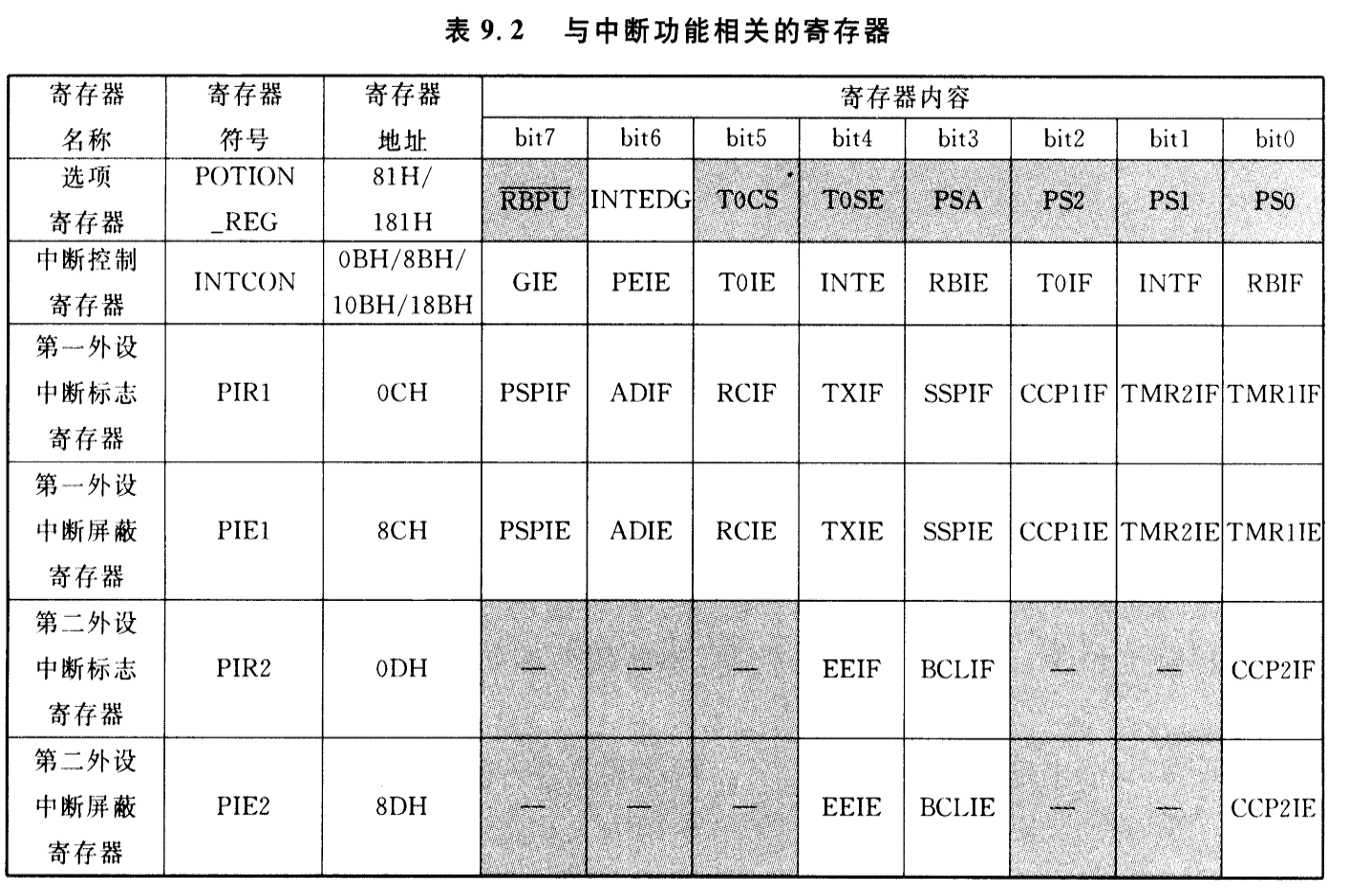

3.与中断相关的寄存器

与中断有关的特殊功能寄存器SFR共有6个,分别是:

选项寄存器OPTION_REG、中断控制寄存器INTCON、第一外围设备中断标志寄存器PIR1、第一外围设备中断屏蔽寄存器PIE1(也称中断使能寄存器)、第二外围设备中断标志寄存器PIR2和第二外围设备中断屏蔽寄存器PIE2。

后5个SFR,共有40位,但仅使用了30位来控制中断,分别与图中的中断逻辑电路输入信号成严格的对应关系。

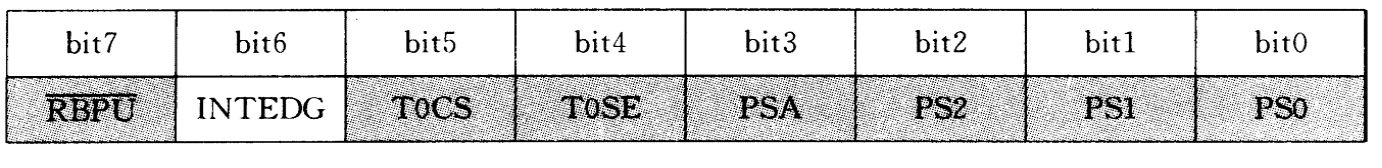

3.1 选项寄存器OPTION _REG

该寄存器包含了与定时/计数器TMR0、分频器和端口RB有关的控制位。RB端口引脚RB0和外部中断INT复用一脚,与该脚有关的一个控制位含义如下:

INTEDG:外部中断INT触发信号边沿选择位:1=选择RB0/INT上升沿触发;0=选择RB0/INT下降沿触发。

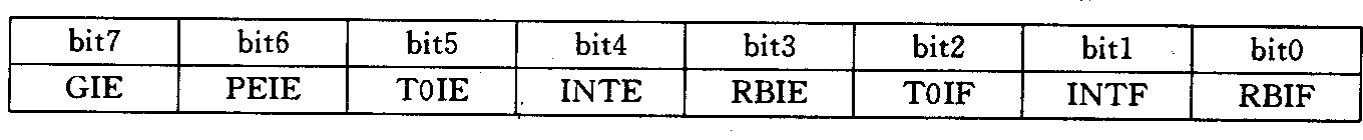

3.2 中断控制寄存器INTCON

它将第一梯队中的3个中断源的标志位和屏蔽位,以及PEIE和GIE包含在其中:

RBIF:端口RB的引脚RB4~RB7电平变化中断标志位。1=RB4~RB7已经发生了电平变化;0=RB4~RB7尚未发生电平变化。

RBIE:端口RB的引脚RB4~RB7电平变化中断屏蔽位。1=允许RB产生的中断;0=屏蔽端口RB产生的中断。

INTF:外部INT引脚中断标志位。1=外部INT引脚有中断触发信号; 0=外部INT引脚无中断触发信号。

INTE:外部INT引脚中断屏蔽位。 l=允许外部INT引脚产生的中断;0=屏蔽外部INT引脚产生的中断。T0IF:TMR0溢出中断标志位。1=TMR0已经发生了溢出;0=TMR0尚未发生溢出。

T0IE:TMR0溢出中断屏蔽位。1=允许TMR0溢出后产生的中断; 0=屏蔽TMR0溢出后产生的中断。

PEIE:外设中断屏蔽位。1=允许CPU响应来自第二梯队中断请求0=禁止CPU响应来自第二梯队中断请求。GIE:全局中断屏蔽位(总屏蔽位)。1=允许CPU响应所有中断源产生的中断请求;0=禁止CPU响应所有中断源产生的中断请求。

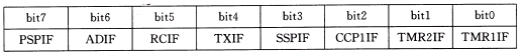

3.3 第一外围设备中断标志寄存器PIR1

该寄存器中各中断标志位的含义如下:

TMR1IF:定时/计数器TMR1模块溢出中断标志位。1=发生了TMR1溢出; 0=未发生TMR1溢出。

TMR2IF:定时/计数器TMR2模块溢出中断标志位。1=发生了TMR2溢出; 0=未发生TMR2溢出。

CCP1IF:输入捕捉/输出比较/脉宽调制CCP1模块中断标志位。 输入捕捉模式下:1=发生了捕捉中断请求;0=未发生捕捉中断请求。输出比较模式下:1=发生了比较输出中断请求;0=未发生比较输出中断请求。脉宽调制模式下: 无用。SSPIF:同步串行端口(SSP)中断标志位。1=发送/接收完毕产生的中断请求;0=等待发送/接收。

TXIF:串行通信接口(SCI)发送中断标志位。1=发送完成,即发送缓冲区空 0=正在发送,即发送缓冲区未空。RCIF:串行通信接口(SCI)接收中断标志位。1=接收完成,即接收缓冲区满0=正在接收,即接收缓冲区空。

ADIF:模拟/数字(A/D)转换中断标志位。1=发生了A/D转换中断;0=未发生A/D转换中断。

PSPIF:并行端口中断标志位,只有40脚封装型号具备,对于28脚封装型号总保持0。1=并行端口发生了读/写中断请求;0=并行端口未发生读/写中断请求。3.4 第一外围设备中断屏蔽寄存器PIE1

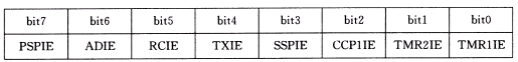

该寄存器中包含的中断屏蔽位(使能位)的含义如下:

TMR1IE:定时器/计数器TMRl模块溢出中断屏蔽位。l=开放TMRl溢出发生中断;0=屏蔽TMRl溢出发生中断。

TMR2IE:定时/计数器TMR2溢出中断屏蔽位。1=开放TMR2溢出发生的中断;0=屏蔽TMR2溢出发生的中断。

CCP1IE:输入捕捉/输出比较/脉宽调制CCP1模块中断屏蔽位。1=开放CCP1模块产生的中断请求;0=屏蔽CCP1模块产生的中断请求。

SSPIE:同步串行端口(SSP)中断屏蔽位。1=开放SSP模块产生的中断请求0=屏蔽SSP模块产生的中断请求。TXIE:串行通信接口(SCI)发送中断屏蔽位。1=开放SCI发送中断请求;0=屏蔽SCI发送中断请求。

RCIE:串行通信接口(SCI)接收中断屏蔽位。1=开放SCI接收中断请求;0=屏蔽SCI接收中断请求。

ADIE:模拟/数字(A/D)转换中断屏蔽位。1=开放A/D转换器的中断请求;0=屏蔽A/D转换器的中断请求。

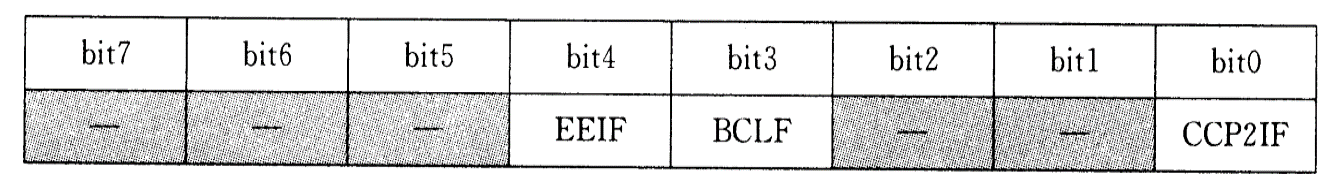

PSPIE:并行端口中断屏蔽位,只有40脚封装型号具备,对于28脚封装型号总保持0。1=开放并行端口读/写发生的中断请求;0=屏蔽并行端口读/写发生的中断请求。3.5 第二外围设备中断标志寄存器PIR2

CCP2IF:输入捕捉/输出比较/脉宽调制CCP2模块中断标志位。输入捕捉模式下:1=发生了捕捉中断请求(必须用软件清0);0=未发生捕捉中断请求。输出比较模式下:1=发生了比较输出中断请求(必须用软件清0);0=未发生比较输出中断请求。脉宽调制模式下:无用

BCLIF:I2C总线冲突中断标志。当同步串行端口MSSP被配置成I2C总线的主控器模式时:1=发生了总线冲突;0=未发生总线冲突。

EEIF:EEPROM写操作中断标志位。1=写操作已经完成(必须用软件清0);0=写操作未完成或尚未开始进行。

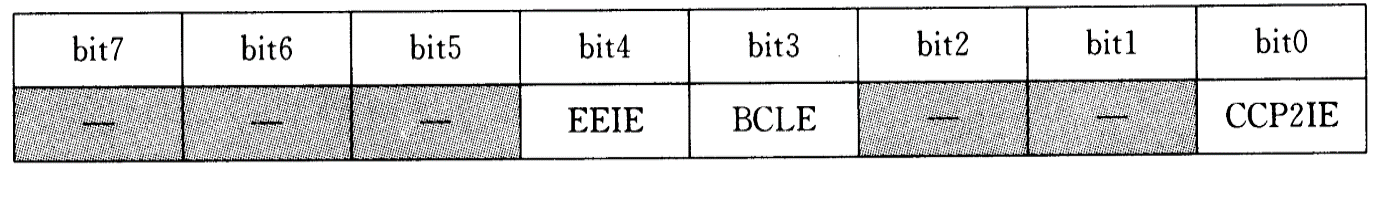

3.6 第二外围设备中断屏蔽寄存器PIE2

CCP2IE:输入捕捉/输出比较/脉宽调制CCP2模块中断屏蔽位。1=开放CCP2模块产生的中断请求;

0=屏蔽CCP2模块产生的中断请求。EEIE:EEPROM写操作中断屏蔽位。1=开放EEPROM写操作产生的中断请求;0=屏蔽EEPROM写操作产生的中断请求。

4.中断的处理

单片机复位后,硬件会自动设置GIE=0,屏蔽所有的中断源,假如要求单片机能响应所有中断,必须设置GIE=1。其实无论GIE或着其他中断屏蔽位是否为1,当某中断源的中断条件满足时,都会发出中断请求,即相应的中断标志位都会置1。但是否能够得到CPU的响应,则由该中断源的中断屏蔽位决定。

CPU响应中断后,自动设置GIE=0,屏蔽所有中断,以免发生重复中断响应,然后自动把PC寄存器当前值压入堆栈,并把PC值赋予地址0004H,从而转向执行中断服务子程序。

进入中断服务程序后,程序必须要确定发出请求的中断源,这可以通过检查各中断源的标志位来实现。确定了中断源后,就用软件把该中断源的标志位清0,否则,执行中断返回指令重开中断后,假如中断标志位仍然为1,则会引起CPU重复响应同一个中断请求。执行中断返回指令RETFIE后,不仅会将保留在堆栈中的断点地址弹回到PC寄存器中,使程序能返回到被中断的程序处;而且还会自动设置GIE=1,重新开放所有的中断源。

5.关于中断部分的总结

⑴单片机在任何情况下的复位,均会导致总屏蔽位和其他的中断屏蔽位清0,即在默认状态下,禁止CPU响应所有中断。

⑵中断标志位的状态与该所有的中断屏蔽位无关,即不管是否允许CPU响应中断源的中断请求,只要满足了中断的条件,中断标志位就会被置成1。⑶当系统开放某一中断源时,中断源就通过中断标志位向CPU申请中断,只要将中断标志位置1,就会产生中断响应。

⑷当CPU响应任一个中断后,全局中断屏蔽位GIE将会自动清0;当中断返回时它又会自动恢复为1。(5)如果在中断服务期间若用软件将自动清0的GIE重新置1,这时若再出现中断请求,就会形成中断的嵌套:即在响应某一中断期间又响应了其他中断。不过嵌套的级数不能超过堆栈的深度(8级),以免造成堆栈溢出。

⑹如果同时发生多个中断请求,到底哪个中断会优先得到处理,完全取决于在中断服务子程序中检查中断源的顺序,原因是各个中断源之间不存在优先级别之分。

⑺每一种中断源受屏蔽的次数不完全相同,第一梯队的中断源受到二次屏蔽,而第二梯队的中断源受到三次屏蔽。

⑻ PIC系列单片机的型号不同,数据存储器RAM的布局不完全相同,为工作寄存器W安排备份寄存器W_TEMP的方法也就不完全相同。

上一篇:PIC单片机-利用Timer2定时器的溢出中断实现动态扫描数码管

下一篇:PIC单片机入门_指令系统

推荐阅读最新更新时间:2024-03-16 16:10

设计资源 培训 开发板 精华推荐

- 消息称 AMD 将入局手机芯片领域,采用台积电 3nm 工艺

- 英飞凌推出OptiMOS™ Linear FET 2 MOSFET, 赋能先进的热插拔技术和电池保护功能

- SGMII及其应用

- 贸泽开售用于机器人和机器视觉的 STMicroelectronics B-CAMS-IMX模块

- 三星 Exynos 2600 芯片前景堪忧:良率挑战严峻,有被取消量产风险

- 苹果搁置反垄断报告的请求遭印度监管机构拒绝,案件将继续推进

- 2024年Automechanika Shanghai海量同期活动刷新历届记录,汇聚行业智慧,共谋未来发展

- 企业文化分享 如何培养稀缺的硅IP专业人员?SmartDV开启的个人成长与团队协作之旅

- 恩智浦发布首个超宽带无线电池管理系统解决方案

- 北交大本科生探秘泰克先进半导体开放实验室,亲历前沿高科技魅力

手把手教你学DSP基于TMS320F28335 第2版 (涨卿杰)

手把手教你学DSP基于TMS320F28335 第2版 (涨卿杰) 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号