一、存储器格式(字对齐):

Arm体系结构将存储器看做是从零地址开始的字节的线性组合。从零字节到三字节放置第一个存储的字(32位)数据,从第四个字节到第七个字节放置第二个存储的字数据,一次排列。作为32位的微处理器,arm体系结构所支持的最大寻址空间为4GB。

存储器格式

1、大端格式:高字节在低地址,低字节在高地址;

2、小端格式:高字节在高地址,低字节在低地址;

指令长度:

Arm微处理器的指令长度是32位的,也可以为16位(thumb状态下)。Arm微处理器中支持字节(8位),半字(16位),字(32位)三种数据类型,其中,字需要4字节对齐,半字需要2字节对齐。

注:所谓的指令长度是一条完整的指令的长度,而不是单纯的mov这3个字母长度

二、ARM体系的CPU有两种工作状态

1、ARM状态:处理器执行32位的字对齐的ARM指令;

2、Thumb状态:处理器执行16位的、半字对齐的Thumb指令;

在程序运行的过程中,可以在两种状态之间进行相应的转换。处理器工作状态的转变并不影响处理器的工作模式和相应寄存器中的内容。

CPU上电处于ARM状态

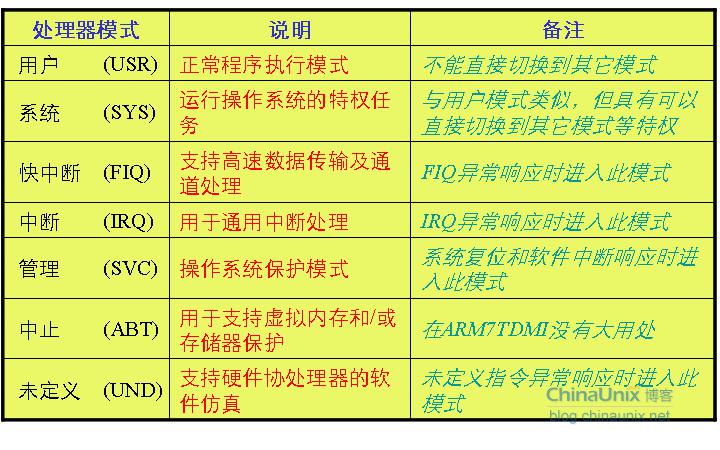

三、ARM体系的CPU有以下7种工作模式:

1、用户模式(Usr):用于正常执行程序;

2、快速中断模式(FIQ):用于高速数据传输;

3、外部中断模式(IRQ):用于通常的中断处理;

4、管理模式(svc):操作系统使用的保护模式;

5、数据访问终止模式(abt):当数据或指令预取终止时进入该模式,可用于虚拟存储以及存储保护;

6、系统模式(sys):运行具有特权的操作系统任务;

7、未定义指令中止模式(und):当未定义的指令执行时进入该模式,可用于支持硬件;

Arm的工作模式切换有两种方法:

被动切换:在arm运行的时候产生一些异常或者中断来自动进行模式切换

主动切换:通过软件改变,即软件设置寄存器来经行arm的模式切换,应为arm的工作模式都是可以通过相应寄存器的赋值来切换的。

Tips:当处理器运行在用户模式下,某些被保护的系统资源是不能被访问的。

除用户模式外,其余6种工作模式都属于特权模式;

特权模式中除了系统模式以外的其余5种模式称为异常模式;

大多数程序运行于用户模式;

进入特权模式是为了处理中断、异常、或者访问被保护的系统资源;

四、寄存器

ARM有31个通用的32位寄存器,6个程序状态寄存器,共分为7组,有些寄存器是所有工作模式共用的,还有一些寄存器专属于每一种工作模式;

R13——栈指针寄存器,用于保存堆栈指针;

R14——程序连接寄存器,当执行BL子程序调用指令时,R14中得到R15的备份,而当发生中断或异常时,R14保存R15的返回值;

R15——程序计数器;

快速中断模式有7个备份寄存器R8—R14,这使得进入快速中断模式执行很大部分程序时,甚至不需要保存任何寄存器;

其它特权模式都含有两个独立的寄存器副本R13、R14,这样可以令每个模式都拥有自己的堆栈指针和连接寄存器;

五、当前程序状态寄存器(CPSR)

CPSR中各位意义如下:

T位:1——CPU处于Thumb状态, 0——CPU处于ARM状态;

I、F(中断禁止位): 1——禁止中断, 0——中断使能;

工作模式位:可以改变这些位,进行模式切换;

六、程序状态保存寄存器(SPSR)

当切换进入某一个特权模式时,SPSR保存前一个工作模式的CPSR值,这样,当返回前一个工作模式时,可以将SPSR的值恢复到CPSR中;

七、模式切换

当异常发生,CPU进入相应的异常模式时,以下工作是由CPU自动完成的:

1、在异常模式的R14中保存前一工作模式的下一条即将执行的指令地址;

2、将CPSR的值复制到异常模式的SPSR中;

3、将CPSR的工作模式设为该异常模式对应的工作模式;

4、令PC值等于这个异常模式在异常向量表中的地址,即跳转去执行异常向量表中的相应指令;

从异常工作模式退回到之前的工作模式时,需要由软件来完成以下工作:

1、将异常模式的R14减去一个适当的值(4或8)后赋给PC寄存器;

2、将异常模式SPSR的值赋给CPSR;

====================================================================================

转载:大端与小端存储模式的详解

存储模式:

小端:较高的有效字节存储在较高的存储器地址,较低的有效字节存储在较低的存储器地址。

大端:较高的有效字节存储在较低的存储器地址,较低的有效字节存储在较高的存储器地址。

STM32 属于小端模式,简单地说:比如:temp=0X12345678;假设temp的地址为:0X4000 0000

那么,在内存里面,其存储就变成了:

| 地址 | HEX |

|0X4000 0000 |78 56 43 12|

更为简单一点:

低地址---------->高地址【大端模式】:

0X12|0X34|0X56|0X78|

低地址---------->高地址【小端模式】:

0X78|0X56|0X34|0X12|

大端与小端的优势

二者无所谓优势,无所谓劣势,各自优势便是对方劣势

大端模式:符号位的判定固定为第一个字节,容易判断正负。

小端模式:强制转换数据不需要调整字节内容,1、2、4字节的存储方式一样

数组在大端小端情况下的存储:

以unsigned int value = 0x12345678为例,

分别看看在两种字节序下其存储情况,

我们可以用unsigned char buf[4]来表示value:

Big-Endian: 低地址存放高位,如下:

高地址

---------------

buf[3] (0x78) -- 低位

buf[2] (0x56)

buf[1] (0x34)

buf[0] (0x12) -- 高位

---------------

低地址

Little-Endian: 低地址存放低位,如下:

高地址

---------------

buf[3] (0x12) -- 高位

buf[2] (0x34)

buf[1] (0x56)

buf[0] (0x78) -- 低位

--------------

低地址

为何会出现大小端之分:

这是因为在计算机系统中,我们是以字节为单位的,

每个地址单元都对应着一个字节,一个字节为8bit。

但是在C语言中除了8bit的char之外,还有16bit的short型,32bit的long型(要看具体的编译器),

另外,对于位数大于8位的处理器,例如16位或者32位的处理器,

由于寄存器宽度大于一个字节,那么必然存在着一个如果将多个字节安排的问题。

因此就导致了大端存储模式和小端存储模式。

例如一个16bit的short型x,在内存中的地址为0x0010,x的值为0x1122,

那么0x11为高字节,0x22为低字节。对于大端模式,就将0x11放在低地址中,即0x0010中,

0x22放在高地址中,即0x0011中。小端模式,刚好相反。

我们常用的X86结构是小端模式,而KEIL C51则为大端模式。

很多的ARM,DSP都为小端模式。有些ARM处理器还可以由硬件来选择是大端模式还是小端模式。

字节序:【一般操作系统都是小端,而通讯协议是大端的】

常见CPU字节序:

Big Endian : PowerPC、IBM、Sun

Little Endian : x86、DEC

ARM既可以工作在大端模式,也可以工作在小端模式

常见文件的字节序

Adobe PS – Big Endian

BMP – Little Endian

DXF(AutoCAD) – Variable

GIF – Little Endian

JPEG – Big Endian

MacPaint – Big Endian

RTF – Little Endian

另外,Java和所有的网络通讯协议都是使用Big-Endian的编码

对于CPU是大端还是小段,可使用代码来进行测试:

//CPU大小端

//0,小端模式;1,大端模式.

static u8 cpu_endian;

//获取CPU大小端模式,结果保存在cpu_endian里面

void find_cpu_endian(void)

{

int x=1;

if(*(char*)&x==1)cpu_endian=0; //小端模式

elsecpu_endian=1; //大端模式

}

以上测试,在STM32上,你会得到cpu_endian=0,也就是小端模式.

上一篇:OK6410裸机之中断处理过程

下一篇:OK6410裸机之异常处理

推荐阅读最新更新时间:2024-03-16 16:15

ARM Cortex-M0权威指南(中文)

ARM Cortex-M0权威指南(中文) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号