1 异常与中断(Cortex-M3)

1.1 异常与中断

原话:

Cortex‐M3 在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。

其中,编号为 1-15 的对应系统异常,大于等于 16 的则全是外部中断。

除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。

所有能打断正常执行流的事件都称为异常。

异常的概念包含中断的概念,即中断是异常的子集。

异常与中断都是硬件支持的。

异常表:

外部中断表:

这里的“外部中断”不是指STM32中的EXTI中断,而是所有中断。

1.2 优先级

原则上,CM3 支持 3 个固定的高优先级和多达 256 级的可编程优先级,并且支持128级抢占(preempt)优先级和128 级亚优先级。但各厂商会做裁剪。

抢占优先级即高抢占优先级任务可以打断正在执行的低抢占优先级任务,而让CPU转而执行高抢占优先级任务。

亚优先级则为多个相同抢占优先级、不同亚优先级的任务同时请求异常时,CPU会先执行高亚优先级的任务。

抢占优先级也有称为“先占优先级”。

“亚优先级”也有会被称为“响应优先级”或“子优先级”。

NVIC 中有一个寄存器是“应用程序中断及复位控制寄存器”,它里面有一个位段名为“优先级组”。

优先级组分配:(默认为7位抢占)

中断优先级组的配置一般在程序最初设置一次。(中途改变中断优先级组本人没有试过)

1.3 中断与悬起(挂起)

当中断输入脚被assert(确认有效?)后,该中断就被悬起。即使后来中断源取消了中断请求,已经被标记成悬起的中断也被记录下来。到了系统中它的优先级最高的时候,就会得到响应。

但是,如果在某个中断得到响应之前,其悬起状态被清除了(例如,在 PRIMASK 或FAULTMASK 置位的时候软件清除了悬起状态标志),则中断被取消。

当某中断的服务例程开始执行时,就称此中断进入了“活跃”状态,并且其悬起位会被硬件自动清除。

中断输入引脚有效后,中断就被悬起,即使取消请求,也会执行。

中断是否处于悬起状态,中断请求被响应的关键。

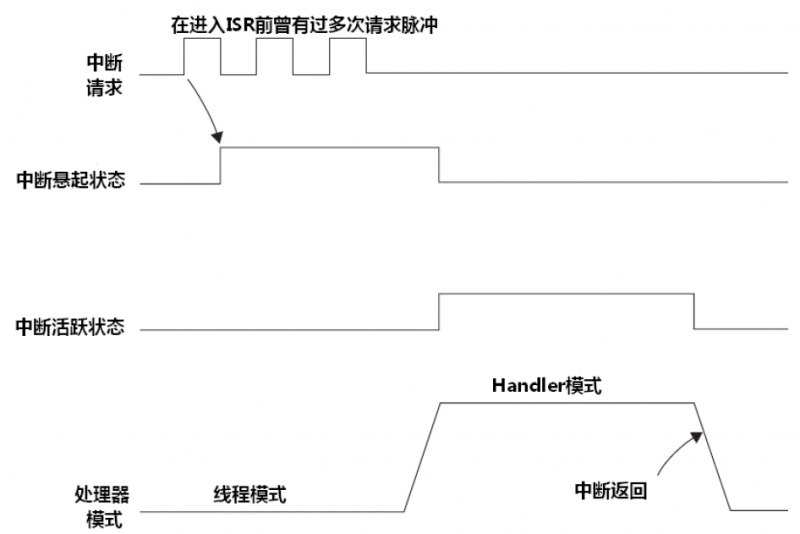

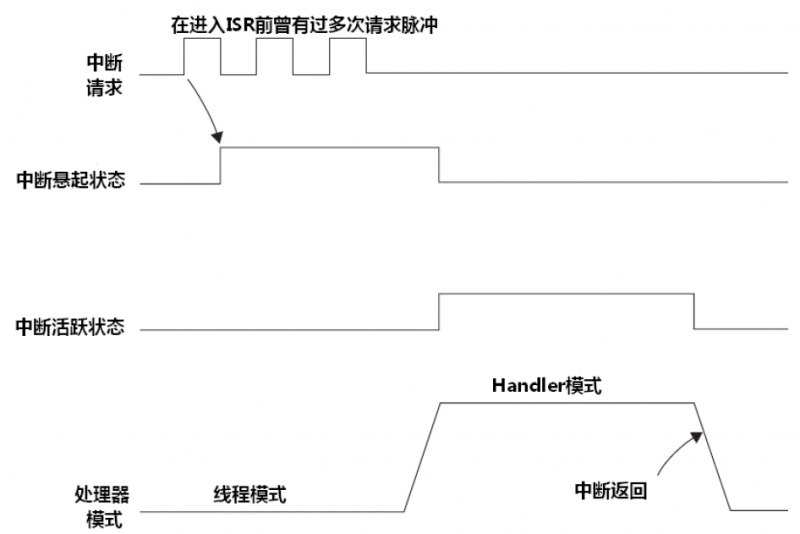

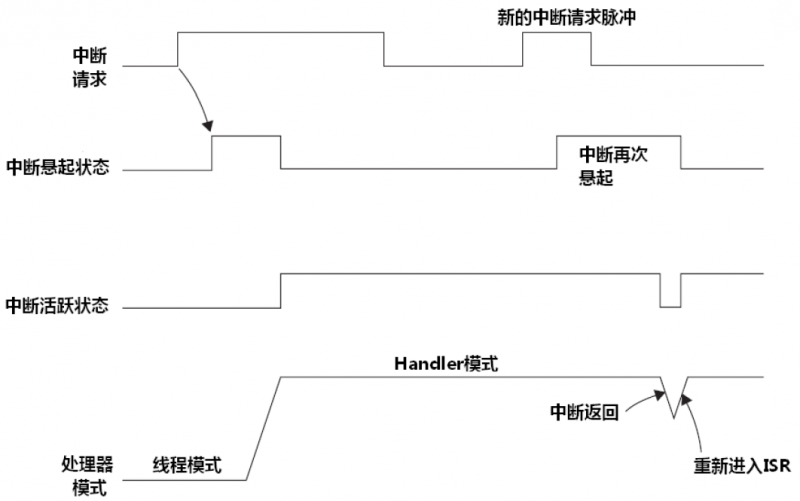

中断响应之前,请求以脉冲方式呈现的话,仅看做一次请求(悬起不被软件清除的前提下)。

中断被响应时,硬件清除悬起状态。

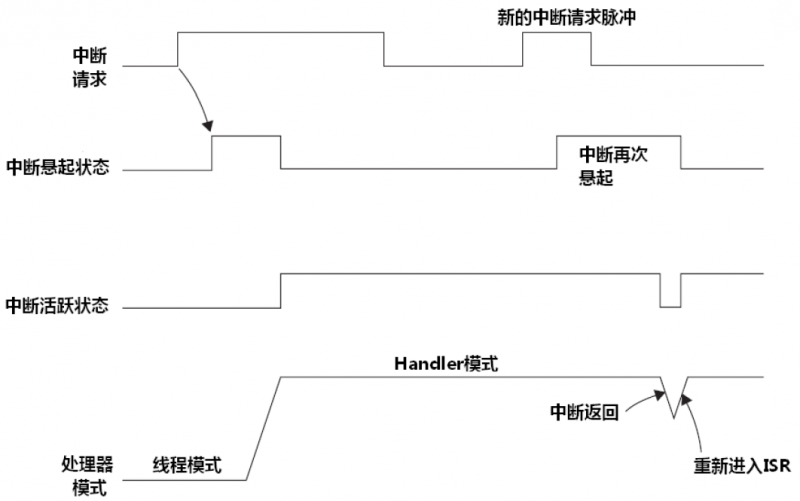

中断响应中,请求被释放,但又变为有效时,会再次悬起。

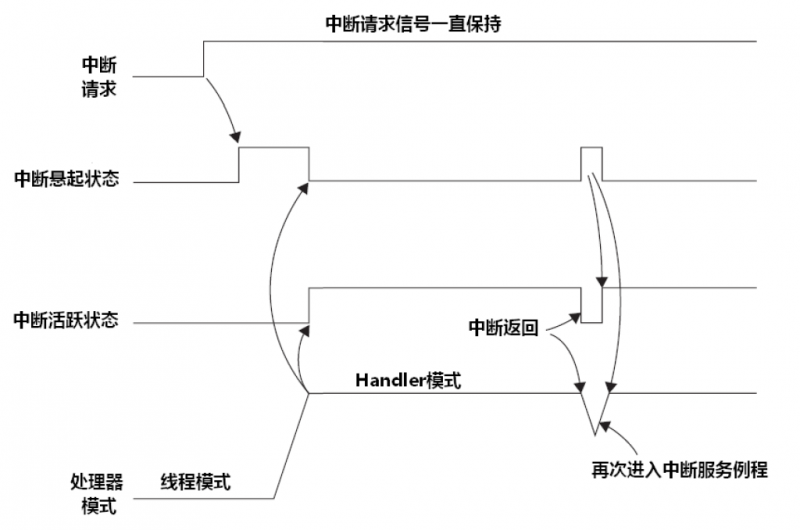

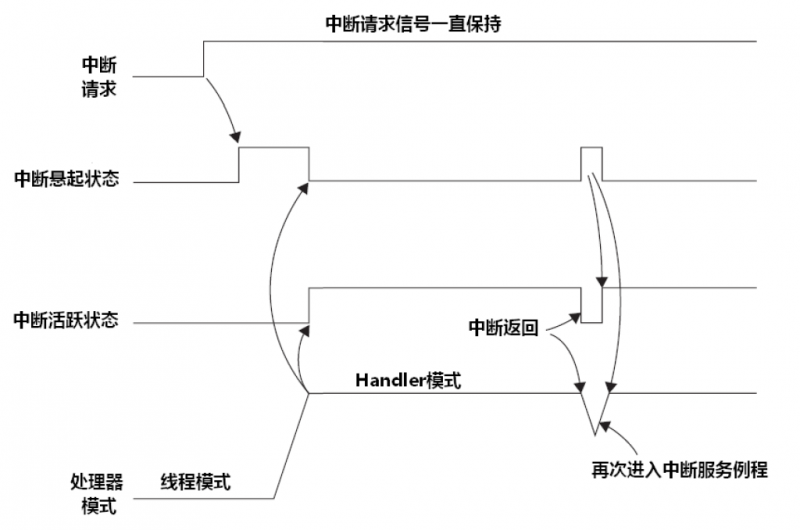

中断响应完成之后,中断请求仍然存在,则再次悬起,等待响应。

1.4 SVC和PendSV

SVC(System serVice Call):系统(服务)调用;

SVC异常是必须立即得到响应的,若因优先级不比当前正处理的高,或是其它原因使之无法立即响应,将上访成硬 fault。

PendSV(Pend System serVice):可悬起系统调用。

PendSV 则不同,它是可以像普通的中断一样被悬起的。

PendSV 的典型使用场合是在上下文切换时(在不同任务之间切换)。

多用于操作系统软件开发中。(uC/OS-II中就用PendSV来实现任务调度)

简单的调度方式:

1.时间轮转(SysTick)

2. 产生一个系统调用(PendSV设置为最低优先级)

任务 A 呼叫 SVC 来请求任务切换(例如,等待某些工作完成)

OS 接收到请求,做好上下文切换的准备,并且 pend 一个 PendSV 异常。

当 CPU 退出 SVC 后,它立即进入 PendSV,从而执行上下文切换。

当 PendSV 执行完毕后,将返回到任务 B,同时进入线程模式。

发生了一个中断,并且中断服务程序开始执行

在 ISR 执行过程中,发生 SysTick 异常,并且抢占了该 ISR。

OS 执行必要的操作,然后 pend 起 PendSV 异常以作好上下文切换的准备。

当 SysTick 退出后,回到先前被抢占的 ISR 中,ISR 继续执行ISR 执行完毕并退出后,PendSV 服务例程开始执行,并且在里面执行上下文切换

当 PendSV 执行完毕后,回到任务 A,同时系统再次进入线程模式。

1.5 CM3中断处理特色——Tail-Chainign

两个同优先级中断交接时,不执行断点恢复和断点数据恢复,直接转到下一个中断执行。

2 中断与事件

2.1 事件、中断事件 中断

凡从事过ST MCU应用开发的人往往会遇到事件、中断事件 中断三个概念或术语。这三个概念彼此关联,有时会让人有点混淆或犯迷糊。

先拿一件生活中的事情打比方对上述三个概念做个基本的粗略理解,之后再分享一个STM32 GPIO外部中断配置案例。

比如一老师在教室里给学生们上课。课堂上的学生可能做出各种行为动作,比方做笔记、打哈气、翻书包、讲小话等,我们把这些行为统称为事件,其中有些行为老师往往只是视而不见,继续他的上课;而有些行为可能导致老师的上课中止,比方讲小话,并对学生的相关行为予以警告、批评或纠正等,然后继续上课。我们把老师因为学生的某些行为而中止授课,并产生后续动作,之后接着上课的这个过程理解为中断或中断响应。我们把可能导致老师上课中断的学生行为理解为中断事件。

结合上面的比方,不难理解中断事件是一种可以导致中断发生的事件,中断则是因为中断事件的发生而导致的后续行为过程。事件与中断事件是包含关系,即事件可分为中断事件或非中断事件。而中断事件与中断之间属于前后关联的因果关系,虽有关联,但二者在时序上、行为上并不一样。

结合具体的ST MCU运行过程,其中会有许多各种各样的事件,比方管脚电平变化、计数器溢出、DMA空、FIFO非空、AD转换结束、超时、外设使能、初始化等等,其中有些事件是不会导致中断产生的,比方外设使能或部分初始化动作是不会导致中断发生的,有些事件就可能导致中断发生,比方计数器溢出,AD转换结束等,这些就是中断事件。当然这些中断事件最终能否触发后续中断,得看是否开启了该中断事件的中断使能,相关中断矢量控制器【NVIC】是否配置,最终让CPU内核参与进来,并完成后续的中断服务动作。

不妨借助STM32 MCU的GPIO的外部事件与中断控制器的框图来理解上述概念。

从上图可以看出,不论外部电平变化成为中断事件还是非中断事件,绿色方框部分都是一样的,即具有相同的触发源。差别就在后面。一般性事件要变为中断事件,得有相关中断使能位的允许。中断事件再向CPU激活相关中断请求,在NVIC配置相应中断矢量后,CPU便参与进行后续的中断响应服务【如保存现场、执行中断服务程序、恢复现场并返回】,而非中断事件就没有中断事件后续的流程,只是有些硬件触发信号或标志的产生。当然非中断事件的形成也是可控的。

既然一个可以触发中断的事件可能被配置中断事件或非中断事件,那么在相关事件的触发配置时就出现两种可能,即允许产生中断或禁止产生中断。于是乎,ST MCU参考手册里在谈到事件的触发方式时就引出了事件模式和中断模式两个概念。

比方STM32的GPIO口的电平跳变基本都是可以触发外部中断的。但在具体配置时,可以根据需要来决定启用还是禁用相关脚的中断功能,从而选择不同的事件触发方式,即事件模式和中断模式。如果不希望电平跳变事件触发中断,就配置为事件模式,反之,配置为中断模式。

在STM32相关参考手册里,涉及中断【INTERRUPT】和事件【EVENT】二词表述的地方比较多,加上这两个词的含义比较宽泛。手册里可能会用interrupt或interrupt event表述同一东西,或者说interrup泛指中断事件及后续中断响应全过程。比方类似下面语句的地方:

有时用Interrupt event明确出来。比方下面表格中提到interrupt event.

总之,不管手册上怎么写,不必拘泥于字词符号,结合上下文弄清怎么回事就好。

2.2 外部中断线或外部事件线示例分析

这张图是一条外部中断线或外部事件线的示意图,图中信号线上划有一条斜线,旁边标志19字样的注释,表示这样的线路共有19套.图中的蓝色虚线箭头,标出了外部中断信号的传输路径,首先外部信号从编号1的芯片管脚进入,经过编号2的边沿检测电路,通过编号3的或门进入中断挂起请求寄存器,最后经过编号4的与门输出到NVIC中断检测电路,这个边沿检测电路受上升沿或下降沿选择寄存器控制,用户可以使用这两个寄存器控制需要哪一个边沿产生中断,因为选择上升沿或下降沿是分别受2个平行的寄存器控制,所以用户可以同时选择上升沿或下降沿,而如果只有一个寄存器控制,那么只能选择一个边沿了.

按下来是编号3的或门,这个或门的另一个输入是软件中断/事件寄存器,从这里可以看出,软件可以优先于外部信号请求一个中断或事件,即当软件中断/事件寄存器的对应位为”1”时,不管外部信号如何,编号3的或门都会输出有效信号.

一个中断或事件请求信号经过编号3的或门后,进入挂起请求寄存器,到此之前,中断和事件的信号传输通路都是一致的,也就是说,挂起请求寄存器中记录了外部信号的电平变化.

外部请求信号最后经过编号4的与门,向NVIC中断控制器发出一个中断请求,如果中断屏蔽寄存器的对应位为”0”,则该请求信号不能传输到与门的另一端,实现了中断的屏蔽.

明白了外部中断的请求机制,就很容易理解事件的请求机制了.图中红色虚线箭头,标出了外部事件信号的传输路径,外部请求信号经过编号3的或门后,进入编号5的与门,这个与门的作用与编号4的与门类似,用于引入事件屏蔽寄存器的控制;最后脉冲发生器的一个跳变的信号转变为一个单脉冲,输出到芯片中的其它功能模块.从这张图上我们也可以知道,从外部激励信号来看,中断和事件的产生源都可以是一样的.之所以分成2个部分,由于中断是需要CPU参与的,需要软件的中断服务函数才能完成中断后产生的结果;但是事件,是靠脉冲发生器产生一个脉冲,进而由硬件自动完成这个事件产生的结果,当然相应的联动部件需要先设置好,比如引起DMA操作,AD转换等;

简单举例:外部I/O触发AD转换,来测量外部物品的重量;如果使用传统的中断通道,需要I/O触发产生外部中断,外部中断服务程序启动AD转换,AD转换完成中断服务程序提交最后结果;要是使用事件通道,I/O触发产生事件,然后联动触发AD转换,AD转换完成中断服务程序提交最后结果;相比之下,后者不要软件参与AD触发,并且响应速度也更块;要是使用事件触发DMA操作,就完全不用软件参与就可以完成某些联动任务了。

总结:

可以这样简单的认为,事件机制提供了一个完全由硬件自动完成的触发到产生结果的通道,不要软件的参与,降低了CPU的负荷,节省了中断资源,提高了响应速度(硬件总快于软件),是利用硬件来提升CPU芯片处理事件能力的一个有效方法;

参考:

1、Cortex-M3权威指南(中文)

2 、STM32参考手册中文版(第10版)

3、http://blog.csdn.net/tanyjin/article/details/53359883

4、http://blog.csdn.net/u010315587/article/details/50086395

上一篇:STM32F030使用RTC周期性唤醒STOP模式

下一篇:ARM Cortex-M3中断跳转过程

推荐阅读最新更新时间:2024-03-16 16:19

深入理解计算机系统

深入理解计算机系统 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号