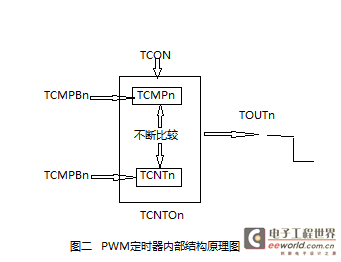

虽然定时器较多,但工作原理都是相同的,只需要理解一个定时器的工作原理即可。对于某一个定时器,其内部结构原理图如图二所示。缓存寄存器TCMPBn和TCNTBn用于缓存定时器n的比较值和初始值;TCON用于控制定时器的开启与关闭;通过读取寄存器TCNTOn得到定时器当前计数值。

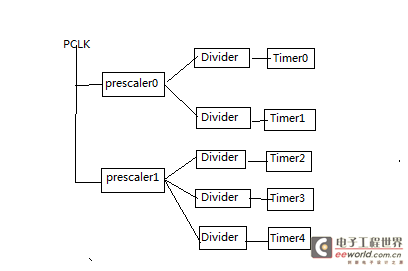

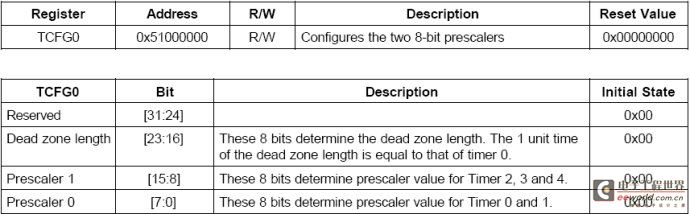

其中: prescaler value=0~255 (它的值由TCFG0寄存器设置,如下图)

| TCFG0 | 位 | 描述 | 初始值 |

| 保留 | [31:24] | 0x00 | |

| Dead zone length | [23:16] | 此8位决定死区长度。死区长度的单位时间等于定时器0的单位时间 |

0x00 |

| Prescaler 1 | [15:8] | 此8位决定定时器2,3,4的预标定器值 | 0x00 |

| Prescaler 0 | [7:0] | 此8位决定定时器0,1的预标定器值 | 0x00 |

| |

位 | 描述 | 初始值 |

| Timer 0 computer buffer register | [15:0] | Set compare buffer value for Timer0 | 0x00000000 |

| |

位 | 描述 | 初始值 |

| Timer 0 count buffer register | [15:0] | Set count buffer value for Timer 0 | 0x00000000 |

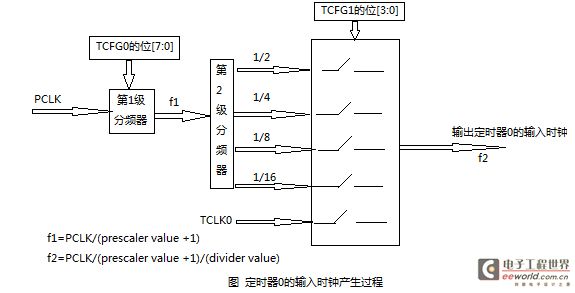

例1:结合上面讲解可知,定时器0的输入时钟是经过PCLK分频的得到的,下图展示了其产生过程。

-------------------------------------分割线---------------------------------------------------

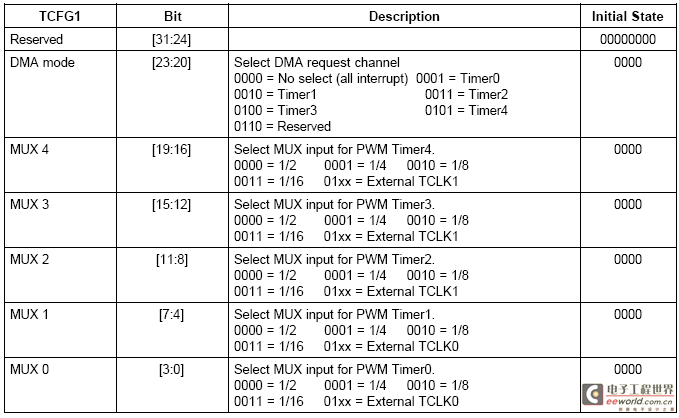

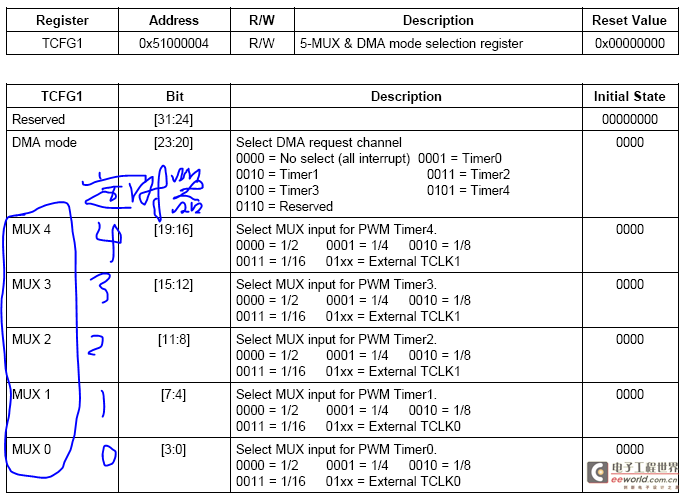

分析:在上题中出现了TCFG1和TCFG0两个定时器配置寄存器,其中TCFG0配置寄存器控制第一级分频器prescaler的分频系数,TCFG1配置寄存器控制多路选择开关,选择第二级分频器divider的分频系数。具体如下图所示:

-----------------------------------------分割线---------------------------------------------------

例2:PCLK为50MHz,请设置适当的分频系数,使定时器0的输入时钟为62.5kHz。

答:已知PCLK为50MHz,则50MHz/62.5kHz=800,即需要对PCLK进行800分频。所以,使第一级分频器的分频系数为100,第2级的分频系数为8即可满足要求。最后,只需要将分频系数写入定时器控制寄存器中相应的位即可,代码如下:

1

2

3

4

上一篇:S3C2440系统时钟

下一篇:ARM下的参数传递

推荐阅读最新更新时间:2024-03-16 14:50

mini2440裸机编程--------触摸屏驱动

mini2440上连接的是一个电阻式触摸屏,电阻式触摸屏是基于AD转换实现的,即某个位置按下之后,这点的电压会发生改变,通过电压就可以判断出是哪一个点被按下了,arm可以得到这个点的坐标。因为触摸屏和lcd是两个设备,因此,触摸屏得到的坐标一般不能够与lcd上的坐标对应起来,所以需要我们在程序中手动的进行校正(虽然不对应,但是他们之间的关系式线性的,因此通过三个点的采样,就可以把系数确定下来。) s3c2440是不支持中断嵌套的。 arm与触摸屏通过tsxptsxm tsyptsym 四根线相连接,数据手册中有一句话:When Touch Screen device is used; XM or PM is only co

[单片机]

STC89C52之定时器中断实验 ---- 自学笔记

一、简述 STC89C5X含有3个定时器:定时器0,定时器1,定时器2. 51 系列单片机一定有基本的 2 个 定时器(定时器 0 和定时器 1),但不全有 3 个中断,通常 我们使用的都是基本的 2 个定时器:定时器 0/1。 二、定时器计数器 2.1、CPU 时序的有关知识 ①振荡周期:为单片机提供定时信号的振荡源的周期(晶振周期或外加振荡 周期)【晶振振荡产生的脉冲,一个脉冲表示一个时钟周期 】。 ②状态周期:一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示)。一个状态周期等于两个时钟周期【 2 个振荡周期为 1 个状态周期,用 S 表示。振荡周期又称 S 周 期或时钟周期。】 ③机器周期

[单片机]

stm32f103——滴答定时器

滴答定时器: 定时器的本质就是计数器。我们设置一个定值,然后计数器开始计数,从我们给的定值开始往下一直数,当数到0时,就做相应的动作(也可以不做什么,当把它用作延时计时的时候)。 滴答定时器systick是一个内核外设(即:内核自带的) 所以在《STM32F10xxx参考手册中文版.pdf》手册中没有相关描述,我们需要参考内核手册 《STM32F10xxx20xxx21xxxL1xxxx Cortex-M3 programming manual.pdf》 Systick是一个24bit的系统定时器(stm32F407的寄存器名字与位数都与f103一样,但是有些芯片定时器位数不同),向下计数(从定值开始数到0),当计数到

[单片机]

6、PIC32系列 定时器TMR-32位定时器使用

1、PIC32参考资源 PIC32系列参考手册 中文版 链接地址:PIC32系列参考手册 第14章 定时器 2、32位同步时钟计数器Harmony配置 1、在左侧Available Components列表中将TMR3拖入到Project Graph中;若新建的工程则将TMR2一起拖入框内; 2、拖入后工程组件如下图所示; 3、TMR2以及TMR3初始配置信息如下; TMR3的配置信息; 4、修改TMR2的参数,设置分频系数为1,32-Bit模式选择32位计数模式,时钟源选择内部时钟,定时时间为1毫秒,空闲模式继续工作; 5、定时器3仅需配置使能中断; 6、组件配置完成后点击左侧的Generate Co

[单片机]

AVR第9课:定时器1的CTC模式

strong #include iom16v.h #include macros.h void main() { DDRD = DDRD|0x30; TCCR1A = 0x50; TCCR1B = 0x09; OCR1A = 65535; } /strong CTC模式下,相关的寄存器:TCCR1A、TCCR1B、OCR1A。相关的引脚是:PD4和PD5。当然你可以用示波器来检测某一引脚PD4或者PD5,就会看到方波。还有一个方法是,将周期调节到1秒,再将PD4链接到发光二极管,就可以看到发光二极管闪烁,有规律的闪烁。但是可惜看不到波形。f=fclk/(2*N*OCRnA)。N表示几分频,OCRnA表示它的最大值。

[单片机]

如何使用带定时器的中断

步骤1:在STM32CubeMX中创建项目 打开STM32CubeMX。点击“新建项目”。从系列选择‘STMF1’,从‘线’选择STM32F103。从MCU列表中,选择“STM32F103RBTx”。单击“确定”。 [1] 现在,需要完成两件事。首先,在STM32板上显示的STM32微控制器上,单击“PA5”并选择“GPIO_Output”。其次,在Peripherals选项卡下的‘TIM1’选项卡下选择‘Internal Clock’作为‘Clock Source’,如图所示: [2] 现在,切换到配置选项卡。在“控件”下,您将看到“TIM1”按钮。单击它,您将看到如下窗口: [3] 现在,在此计数器设置下的“

[单片机]

mini2440触摸屏驱动----非input子系统实现方法

触摸屏的驱动程序在不是使用input子系统的实现过程中,其实和普通的字符设备驱动没有太大的差别,只要按照触摸屏那几个步骤正常进行就可以。 ①s3c2410_ts_init函数,这是整个程序的入口处。实现了各类初始化的作用。 /*设备初始化函数*/ static int __init s3c2410_ts_init(void) { int ret; tsEvent = tsEvent_dummy; /* 注册字符设备 第一个参数为0表示自动分配 */ ret = register_chrdev(0, DEVICE_NAME, &s3c2410_fops); //普通的注册失败判

[单片机]

利用555定时器构成白光LED电压调节器的方法

本文以一个555定时器为主要器件构成电压调节电路(如图所示),用来控制一个或多个白光LED。定时器IC1与R1、R2、C2构成了可复位非稳态多谐振荡器。 首次输入电压V S 后,D1将使存储电容器C1充电直到其电压略低于V S 。最初,晶体管Q2处于截止状态,IC1的复位输入为高电平,输出端(OUTPUT)为高电平,以让电流能经过R1给C2充电。 这段时间内,R4拉动放电端(DISCHARGE)导通晶体管Q1,电感L1中的电流I L 开始斜线增大。由于Q1饱和,因此D3和LED都处于反向偏压状态。 当C2的电压超过IC1中管脚6的极限电压(THRESHOLD)时,输出端(OUTPUT)与放电端(DISCHARGE)都变为低电平

[应用]

小广播

热门活动

换一批

更多

设计资源 培训 开发板 精华推荐

最新单片机文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

11月13日历史上的今天

厂商技术中心

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号