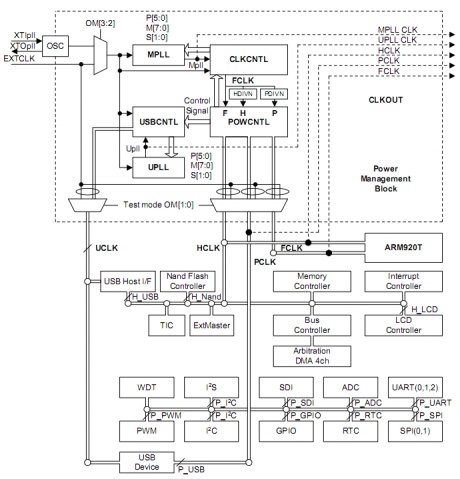

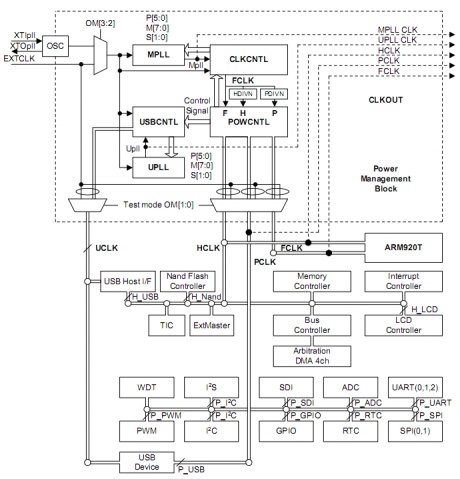

The clock & power management block consists of three parts: clock control, USB clk control, and power control.

Clock control logic

The Clock control logic in S3C2410X can generate the required clock signals including FCLK for CPU, HCLK for

the AHB bus peripherals, and PCLK for the APB bus peripherals.

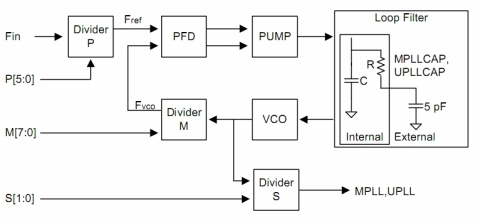

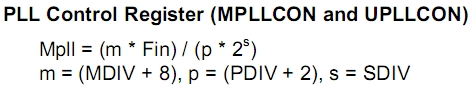

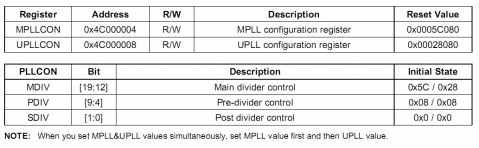

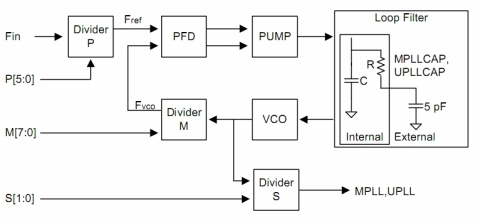

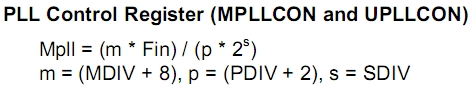

The S3C2410X has two Phase Locked Loops

(PLLs): one for FCLK, HCLK, and PCLK, and the other dedicated for USB block (48Mhz). The clock control logic

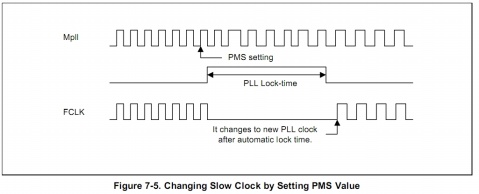

can make slow clocks without PLL and connect/disconnect the clock to each peripheral block by software, which

will reduce the power consumption.

The main clock source comes from an external

crystal (XTIpll) or an external clock (EXTCLK). The clock generator includes an oscillator (Oscillation Amplifier),

which is connected to an external crystal, and also has two PLLs (Phase-Locked-Loop), which generate the high

frequency clock required in the S3C2410X.

MPLL锁相环模块(提供FLCK/HCLK(AHB)/PCLK(APB)) UPLL锁相环模块(提供UCLK)相同

关键字:S3C2410 时钟 电源管理单元

引用地址:

S3C2410时钟&电源管理单元

推荐阅读最新更新时间:2024-03-16 15:03

STM32F407系统时钟设置

startup_stm32f40x_cl.s(启动文件) → SystemInit() → SetSysClock () if (HSEStatus == (uint32_t)0x01) { /* Select regulator voltage output Scale 1 mode */ RCC- APB1ENR |= RCC_APB1ENR_PWREN; PWR- CR |= PWR_CR_VOS; /* HCLK = SYSCLK / 1*/ RCC- CFGR |= RCC_CFGR_HPRE_DIV1; #if defined (STM32F40_41xxx) || defined

[单片机]

lpc1768的系统时钟

#define XTAL_FREQ 12000000 #define VECT_TAB_OFFSET 0x0000 void SystemInit(void) { //PLL0时钟配置 LPC_SC- SCS = 0X00000020; /*使能外部主晶振,频率范围1-20M*/ if (LPC_SC- SCS & (1 5)) /* 主时钟被使能 */ { while ((LPC_SC- SCS & (1 6)) == 0);/* 等待主晶振使能并稳定 */ } LPC_SC- CCLKCFG = 0x00000003; /*

[单片机]

【蓝桥杯单片机组】实时时钟RTC(DS1302)

1、寄存器表 注意: (1)ds1302.h中提供的寄存器地址是写地址,读寄存器时需要将地址加一 (2) #define ds1302_control_addr 0x8Ee //写保护命令字单元地址 对应上图倒数第二行:BIT7 = 0(取消写保护)、BIT7 = 1(上写保护) (3)读一次寄存器后需要增加一条写指令(不知道为什么): curtime = Ds1302_Single_Byte_Read(read_addr ); Ds1302_Single_Byte_Write(0x00, 0x00); (4)在提供的ds1302.c中使用到的函数为: /*****************************

[单片机]

基于多路移相时钟的瞬时测频模块设计

0 引 言 目前,脉冲雷达的脉内信号分析一直是研究的热点和难点,如何能更快速,准确的对脉内载波频率测量成为研究人员关注的目标,与此同时高精度频率源在无线电领域应用越来越广泛,对频率测量设备有了更高的要求,因此研究新的测频方法对开发低成本、小体积且使用和携带方便的频率测量设备有着十分重要的意义。本文根据雷达发射机频率快速变化的特点,采用目前新型的逻辑控制器件研究新型频率测量模块,结合等精度内插测频原理,对整形放大后的脉冲直接计数,实现对下变频后单脉冲包络的载波快速测频。具有测量精度高,测量用时短的特点,能作为脉冲雷达单脉冲瞬时测频模块。 1 移相时钟计数法测频原理 移相时钟计数法以等精度测频法为基础,是一种新的内插技术

[模拟电子]

STM32时钟配置及相关问题

Ⅰ、写在前面 最近有很多朋友问: 1.我的USART串口打印出来的数据是乱码? 2.我的TIM定时器延时或定时不准确? 常见可能原因: 1.晶振问题:外部晶振不起振、或频率与配置不匹配。 2.软件问题:分频、倍频、时钟源选择等。 总结来说,主要还在于软件的问题。因为即使没有外部晶振,也可以使用内部晶振。 其实,软件的问题是容易得到解决的,只要你了解了STM32时钟配置里面具体内容就知道了。 关于本文的详细内容请看下面章节 Ⅱ、本文要点 要了解时钟的配置,就需要知道它在哪里配置,也就是还需要了解软件执行的流程。 1.软件流程 说软件流程是让大家知道系统时钟配置的位置。不管是使用寄存器开发,还是使用库(标准库、HA

[单片机]

STM32F4时钟系统

1:STM32有5个时钟源:HSI,HSE,LSI,LSE,PLL HSI是高速内部时钟,RC振荡器、频率为16MHZ,精度不高。可以直接作为系统时钟或者用作PLL时钟输入 HSE是高速外部时钟,可接石英/陶瓷谐振器,或接外部时钟源,频率范围为4M~26M. LSI是低速内部时钟,RC振荡器,频率为32KHZ,提供低功耗时钟。主要供独立看门狗和自动唤醒单元使用。 LSE是低速外部时钟,接频率为32.768KHZ的石英石钟。RTC PLL为锁相环倍频输出。STM32F4有两个PLL。 主PLL,(PLL)由HSE或者HSI提供时钟信号,并具有两个不同的输出时钟 第一个输出PLLP用于生成高速的系统时钟(最

[单片机]

TI推出1.8V 可编程VCXO 3-PLL 时钟合成器

CDCE937 和 CDCEL937 均为基于 PLL 模块的、低成本、高性能的可编程时钟合成器,可以在单输入频率的不同频率下生成多达七个输出时钟。每一个输出均可以进行系统内编程,从而使用三个独立的可配置 PLL 就可用于任何高达 230MHz 的时钟频率。该器件具有简单的频率同步,使零- PPM 时钟生成成为可能。另外,这两种合成器还具有扩频时钟及片上 EEPROM 和通过 SDA/SCL 进行系统内热编程的特点。对于数字媒体系统、流媒体、 GPS 接收机、便携式媒体以及 DSP/OMAP/DaVinci TM 媒体处理器应用而言,这两种产品都是颇具吸引力的选择。 特性 : l

[安防电子]

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号