1.ARM的7种工作模式

ARMv4和ARMv5的指令集规定了ARM的7种工作模式,由寄存器CPSR[4:0]决定(见下表),分别是

用户(User)模式:ARM处理器正常的程序执行状态

系统(System)模式:运行具有特权的操作系统任务

快速中断(FIQ)模式:用于处理紧急的中断,如高速数据传输或通道处理

普通中断(IRQ)模式:用于处理通用的中断,通常在硬件中断信号后进入该模式

管理(Supervisor)模式:操作系统使用的保护模式,是CPU上电后的默认模式,主要用于系统的初始化

数据访问终止(Abort)模式:用于虚拟存储及存储保护,当访问非法地址或读取无权限内存地址时进入该模式

未定义指令中止(Undifined)模式:当执行未定义的指令时进入该模式,用于支持硬件协处理器的软件仿真

| CPSR[4:0] | 处理器模式 | 可访问的寄存器 |

| 0b10000 | USER | R0~R14;PC;CPSR |

| 0b11111 | SYSTEM | R0~R14;PC;CPSR |

| 0b10001 | FIQ | R0~R7;R8_FIQ-R14_fiq;PC;CPSR;SPSR_fiq |

| 0b10010 | IRQ | R0~R12;R13_irq-R14_irq;PC;CPSR;SPSR_irq |

| 0b10011 | SUPERVISOR | R0~R12;R13_svc-R14_svc;PC;CPSR;SPSR_svc |

| 0b10111 | ABORT | R0~R12;R13_abt-R14_abt;PC;CPSR;SPSR_abt |

| 0b11011 | UNDEFINED | R0~R12;R13_und-R14_und;PC;CPSR;SPSR_und |

现在ARMv6和ARMv7指令集做出了改变,由MSP(主堆栈指针)和PSP(进程堆栈指针),用户模式和特权模式组合成4种工作模式,将其他模式整合到异常向量表中,干净简洁舒服啦。

2.ARM寄存器

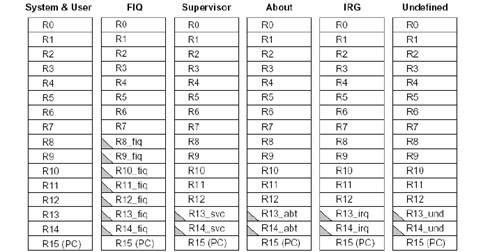

ARM共有37个32位物理寄存器,7种工作模式下可访问的寄存器见下表,User和System使用完全相同的物理寄存器。

2.1 R0~R7

所有工作模式下,R0-R7都分别指向同一个物理寄存器(共8个物理寄存器),它们未被系统用作特殊的用途。在中断或异常处理进行工作模式转换时,由于不同工作模式均使用相同的物理寄存器,可能造成寄存器中数据的破坏。

2.2 R8~R12

在User&System、IRQ、Svc、Abt和Und模式下访问的R8~R12都是同一个物理寄存器(共5个物理寄存器);在FIQ模式下,访问的R8_fiq~R12_fiq是另外独立的物理寄存器(共5个物理寄存器)。

2.3 R13和R14

在User&System、IRQ、FIQ、Svc、Abt和Und访问的R13_

R13在ARM指令中常用作堆栈指针(SP),但这只是一种习惯用法,用户也可使用其他的寄存器作为堆栈指针。而在Thumb指令集中,某些指令强制性的要求使用R13作为堆栈指针。

由于处理器的每种工作模式均有自己独立的物理寄存器R13,在用户应用程序的初始化部分,一般都要初始化每种模式下的R13,使其指向该工作模式的栈空间。这样,当程序进入异常模式时,可以将需要保护的寄存器放入R13所指向的堆栈,而当程序从异常模式返回时,则从对应的堆栈中恢复,采用这种方式可以保证异常发生后程序的正常执行。

R14称为链接寄存器(Link Register),当执行子程序调用指令(BL)时,R14可得到R15(程序计数器PC)的备份。在每一种工作模式下,都可用R14保存子程序的返回地址,当用BL或BLX指令调用子程序时,将PC的当前值复制给R14,执行完子程序后,又将R14的值复制回PC,即可完成子程序的调用返回。以上的描述可用指令完成。

执行以下任意一条指令:

MOV PC, LR

BX LR

在子程序入口处使用以下指令将R14存入堆栈:

STMFD SP!,{,LR}

对应的,使用以下指令可以完成子程序返回:

LDMFD SP!,{,PC}

R14也可作为通用寄存器。

2.4 程序计数器PC(R15)

所有工作模式下访问的R15都是同一个物理寄存器,由于ARM体系结构采用了多级流水线技术,对于ARM指令集而言,PC总是指向当前指令的下两条指令的地址,即PC的值为当前指令的地址值加8个字节。

在ARM状态下,R15[1:0]为0,R15[31:2]用于保存PC;在Thumb状态下,R15[0]为0,R15[31:1]用于保存PC。

2.5 CPSR和SPSR

R16用作CPSR(Current Program Status Register,当前程序状态寄存器),CPSR可在任何工作模式下被访问,它包括条件标志位、中断禁止位、当前处理器模式标志位,以及其他一些相关的控制和状态位。

每一种工作模式下又都有一个专用的物理状态寄存器,称为SPSR(Specified Program Status Register,备份的程序状态寄存器),当异常发生时,SPSR用于保存CPSR的当前值,从异常退出时则可由SPSR来恢复CPSR。

User模式和System模式不属于异常模式,它们没有SPSR,当在这两种模式下访问SPSR,结果是未知的。

2.6 CPSR各标志位含义

| 31 | 30 | 29 | 28 | 27 | 26 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| N | Z | C | V | Q | DNM(RAZ) | I | F | T | M4 | M3 | M2 | M1 | M0 |

N(Negative)---设置成当前指令运算结果的bit[31]的值。当两个有符号整数运算时,N=1运算结果为负数,N=0运算结果为正。

Z(Zero)---Z=1运算结果为零;Z=0表示运算的结果不为零。对于CMP指令,Z=1表示进行比较的两个数大小相等。

C(Carried out)---分四种情况讨论

1)在加法指令中(包括比较指令CMP),当结果产生进位,则C=1,表示无符号运算发生上溢出;其他情况C=0。

2)在减法指令中(包括减法指令CMP),当运算发生借位,则C=0,表示无符号运算发生下溢出;其他情况下C=1。

3)对于包含移位操作的非加减运算指令,C中包含最后一次溢出的位的数值

4)对于其他非加减运算指令,C位的值通常不受影响

V(oVerflow)---对于加减运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1符号为溢出;通常其他指令不影响V位。

Q---在ARM V5的E系列处理器中,CPSR的bit[27]称为Q标识位,主要用于指示增强的DSP指令是否发生了溢出。同样的spsr的bit[27]位也称为Q标识位,用于在异常中断发生时保存和恢复CPSR中的Q标识位。在ARM V5以前的版本及ARM V5的非E系列的处理器中,Q标识位没有被定义。

I和F---当I=1时禁止IRQ中断,当F=1时禁止FIQ中断

T---对于ARM V4以更高版本的T系列ARM处理器,T=0表示执行ARM指令;T=1表示执行Thumb指令

对于ARM V5以及更高版本的非T系列处理器,T=0表示执行ARM指令;T=1表示强制下一条执行的指令产生未定指令中断

M[4:0]---定义了的ARM工作模式,具体见1中表CSPR[4:0]定义的ARM工作模式

3 控制程序的执行流程的3种方式

1)在正常执行过程中,每执行一条ARM指令,程序计数器(PC)的值加4个字节;每执行一条Thumb指令,程序计数器寄存器(PC)加2个字节。整个过程是按顺序执行。

2)跳转指令,程序可以跳转到特定的地址处执行,或者跳转到特定的子程序处执行。其中,B指令用于执行跳转操作;BL指令在执行跳转操作同时,保存子程序的返回地址;BX指令在执行跳转操作同时,根据目标地址为可以将程序切换到Thumb状态;BLX指令执行3个操作,跳转到目标地址处执行,保存子程序的返回地址,根据目标地址为可以将程序切换到Thumb状态。

3)当异常中断发生时,系统执行完当前指令后,将跳转到相应的异常中断处理程序处执行。当异常中断处理程序执行完成后,程序返回到发生中断指令的下条指令处执行。在进入异常中断处理程序时,要保存被中断程序的执行现场,从异常中断处理程序退出时,要恢复被中断程序的执行现场。

上一篇:ARM的9种寻址方式

下一篇:ARM的异常中断和处理过程

推荐阅读最新更新时间:2024-03-16 15:32

设计资源 培训 开发板 精华推荐

- 苹果M1芯片MacBook Pro跑分解密:单核1714,多核6802

- 面向集成电路、人工智能等领域,四川提职业技能提升计划

- NetApp ONTAP数据管理软件,助力企业加快数字化转型步伐

- Nordic低功耗蓝牙传感器持续监测吉他温湿度,提供高效保护

- 福禄克携最新产品亮相2020进博会助力中国新基建

- 工博会抢“仙”看 | SEER重磅新品,全感知 AI 物流系统 RoboView首发在即

- 定了!英伟达宣布以400亿美元收购Arm

- 地平线成为首个ISO 26262功能安全流程认证的中国 AI芯片公司

- 物联网设备和机器人等技术正在引领货运业改革潮流!

- 刘涛牵手云鲸扫地机器人,让你与智能生活零距离

ARM Cortex-M0权威指南(中文)

ARM Cortex-M0权威指南(中文) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号