摘要

分布式基站系统中,RRU 通常会通过光纤拉远实现与 BBU 的远程互联。由于光纤自身的特性,传输过程中必然会引入抖动和漂移;尤其是漂移,因其低频特性,并且难于滤除,在SERDES 的 FIFO 深度不够的情况下有可能会造成 FIFO 的溢出。

本文首先会对这个问题进行一般性地分析,在此基础上我们将以德州仪器公司 10G SERDES 器件 TLK10002 为例,提出一个新的解决方案,即采用双时钟模式提供 SERDES系统时钟,并且探讨了这种模式的具体实现方式。同时,为了验证双时钟方案的可行性,我们搭建了相应的测试平台,并给出了相应的测试结果。

1、 光纤漂移引起的 SERDES FIFO 溢出问题分析

1.1 漂移及漂移形成的原因

漂移是一个数字信号的有效瞬时在时间上偏离其理想位置的,非累计性的偏离。所谓的“长期的偏离”是指偏离随时间较慢的变化,通常认为变化频率低于 10Hz 就属于较慢的变化。

实际数字信号存在的相位噪声,抖动时相位噪声的高频成分,漂移是相位噪声的低频成分,工程中以10Hz 来划分高、低频。产生这两种频率成分的机理有所不同。产生低频成分,也就是产生漂移的主要原因是传输媒质和设备中传输时延的变化,例如光纤白天受热变长,时延增加,信号迟到,相位滞后;光纤夜间受冷变短,时延减少,信号早到、相位超前。产生高频成分,也就是产生抖动的主要原因是内部噪声引起的信号过零点随机变化,例如振荡器输出信号的相位噪声,数字逻辑开关时刻的不确定性等。

漂移不会直接导致传输产生误码,因为传输设备的恢复时钟电路能跟踪相位的慢变化。漂移幅度变化虽慢,但长期累积幅度可能高达 1000UI[3]。

1.2 漂移引起的 SERDES FIFO 溢出问题分析

一个典型的 BBU 和 RRU 系统级联方案如图 1 所示,在 RRU 一侧,由于 JC PLL(主时钟芯片)会自动跟踪输入的串行数据流,当输入频率发生变化时,JC PLL 会调整输出频率以匹配输入频率的变化。在这个跳变瞬间,如果 SERDES 的 FIFO 的读写速率可能不一致,导致 FIFO 的冲突,从而造成溢出。但是,通过选择跳变速度足够快的 JC PLL,这种溢出是完全可以避免的,而一旦JC PLL 锁定到输入数据流,FIFO 读写工作在同一速率,就不会存在溢出问题。

在 BBU 一侧,值得注意的是时钟信号的抖动,尤其是漂移引起的 FIFO 溢出。如果这种漂移来自于 BBU 自身的参考时钟,由于输入数据数率是与 BBU 速率匹配的,不会造成任何问题; 但是,如上节所阐述的,光纤的温漂等特性有可能引入新的漂移,如果 RX FIFO 两侧工作在不同的时钟域, 这种光纤引入漂移会造成 SERDES 内部 FIFO 的碰撞,FIFO 自身的深度如果不足以吸收这种碰撞,就会引起 FIFO 溢出。

2、BBU SERDES 双系统时钟方案及具体实现

2.1 TLK10002 内部时钟架构

TLK10002 是德州仪器公司推出的双通道 10G SERDES 芯片,它可以支持目前所有的 CPRI 和OBSAI 速率,从 1.2288Gbps 到 9.8304Gbps,因而特别适合无线基站的应用。

TLK10002 内部的时钟架构如图 2 所示,它的 A/B 通道可以通过 REFCLK0P/N 或者REFCLK1P/N 管脚来提供参考时钟,这两个参考时钟的选择可以通过 MDIO 或者REFCLKA_SEL 和 REFCLKB_SEL 管脚来实现。

高速侧 SERDES 的 CDR 主要用于从输入串行数据中恢复时钟信号,恢复的时钟信号从CLKOUTAP/N 和 CLKOUTBP/N 输出。输出信号频率有多种选择:通过寄存器配置,用恢复时钟频率除以 1, 2, 4, 5, 8, 10, 16, 20, 或者 25 均可。

对于每个通道而言,高速侧 SERDES 和低速侧 SERDES 可以工作在一个时钟域,即两者使用同一参考时钟;同时,TLK10002 也提供了另外一种时钟模式,即高速侧 SERDES 和低速侧SERDES 使用不同的参考时钟,这种情况下,高速侧锁相环和低速侧锁相环会工作在不同的时钟域。

图 2 TLK10002 内部时钟架构

2.2 TLK10002 双时钟系统方案

基于双时钟 TLK10002 构建的系统级联方案如图 3 所示。在这种方案中,TLK10002 高速侧SERDES 和低速侧 SERDES 采用不同的参考时钟。

在 BBU 一侧,高速侧锁相环采用本地的参考时钟,一旦高速侧锁相环锁定,并且 BBU 和 RRU 之间建立稳定的链路,BBU 一侧 TLK10002 的 CDR 会有稳定输出,这个输出给 BBU 上的 Jitter Cleaner 提供参考输入。 一旦 Jitter Cleaner 正常锁定,它的输出又会作为低速侧锁相环的参考输入。

采用这种配置,由于 SERDES 本身可以处理最高 200ppm 的频率偏移,发射和接收通道的速率是完全相互独立的。这样,FIFO 的两侧完全工作在同一时钟域,FIFO 就不会存在溢出的风险。在这种情况下,FIFO 仅仅用来吸收不同时钟之间的相位偏移和补偿 jitter cleaner 的跟踪能力。

2.3 双系统时钟方案的具体实现

以 BBU 一侧为例,双系统时钟方案具体实现方式如下图 4 所示。在这个方案中,由于 LMK04808具有超低相位噪声特性,我们使用它作为抖动消除器。

图 4 采用双时钟方案构建 BBU SERDES 系统

对图 4 所示的系统,系统配置及操作顺序如下:

1) 正常配置 TLK10002 0X00 到 0X0D 寄存器。

2) 等待 TLK10002 高速侧锁相环 HS PLL 正常锁定。//只要本地参考时钟准备就绪,高速侧锁相环即可锁定(此时并不需要建立稳定的 10G 链路)。

3) 切换 TLK10002 ENRX:先置为 0,再置为 1。//使 HS SERDES 自适应链路状况。

4) 等待 10ms。 //等待 HS SERDES 设置参数,确保 CDR 为 LMK04808 提供有效的参考时钟。

5) 配置 LMK04808 确保其正常锁定。

6) 等待 TLK10002 低速侧锁相环 LS PLL 正常锁定。//只要 LMK04808 锁定并且正常输出,LS PLL 就可以正常锁定

7) 重启数据通路。//此时,低速侧和高速侧 SERDES 都具有有效时钟,重启数据通路可以优化 FIFO的指针位置和触发低速侧 Lane 重新对齐

3、双系统时钟方案实际测试

3.1 测试设置

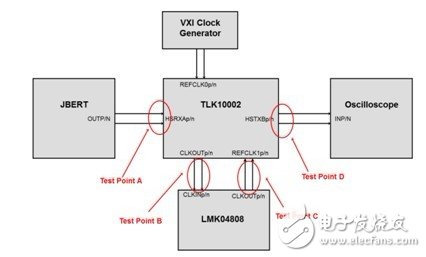

TLK10002 双系统时钟方案测试设置如图 5 所示。J-BERT 用来产生 9.8304Gbps 的 PRBS7 测试信号,在这个信号上会加载 45ps 的宽带随机抖动;VXI Clock Generator 用于产生 122.88MHz 的本地时钟,作为 TLK10002 高速侧锁相环的参考时钟;LMK04808 作为本地的 Jitter Cleaner,采用 LMK04808 评估板默认的配置,TLK10002 CDR 输出 122.88MHz 信号作为 LMK04808 参考输入,LMK04808 输出的 122.88MHz LVPECL 信号作为 TLK10002 低速侧锁相环的参考时钟;TLK10002 配置成 9.8304Gbps PRBS 测试模式,发射通道采用默认的设置;高速示波器用于观测 TLK10002 发射通道输出 9.8304Gbps 高速串行信号。

在 A、B、C、D 四个测试点,我们将分别测试 TLK10002 串行输入信号眼图、TLK10002 恢复时钟信号相噪、LMK04808 输出信号相噪以及 TLK10002 发射机输出眼图。

图 5 TLK10002 双时钟系统方案测试设置

3.2 实测结果

TLK10002 串行输入信号眼图如图 6 所示,它的随机抖动(Rj)为 2.98ps,确定抖动(Dj)为4.23ps,总的抖动(Tj)为 44.98ps,通常,这种类型的宽带随机抖动是很难通过均衡来消除的。

TLK10002 恢复时钟输出相噪曲线如图 7 所示,采用图 6 所示的输入信号,TLK10002 的恢复时钟 RMS 抖动为 3.98ps(1KHz~20MHz)。

LMK04808 输出相噪如图 8 所示,可以看到在通过 Jitter Cleaner(LMK04808)之后,由于LMK04808 的强劲抖动消除能力,其输出 RMS 抖动仅为 121fs(1KHz~20MHz)。

TLK10002 发射通道输出眼图如图 9 所示,其随机抖动(Rj)为 1.02ps,确定抖动(Dj)为5.79ps,总的抖动(Tj)仅为 19.6ps,眼图清晰。

4、结论

由上述理论分析和实际测试结果可以清楚地看到由 TLK10002 、LMK04808 构建的双时钟系统方案完全可以避免因光纤引入漂移从而导致 SERDES FIFO 溢出的问题;同时,由于发射机眼图主要是由本地参考时钟的相噪决定,采用这种双时钟模式对眼图以及发射机输出噪声性能没有影响。

上一篇:IDT 推出业界首个 16 通道、8 GT/s PCI Express 3.0 信号调理重定时器

下一篇:关于ADI混合信号处理技术产品解决方案

推荐阅读最新更新时间:2023-10-12 20:50

- 英飞凌推出OptiMOS™ Linear FET 2 MOSFET, 赋能先进的热插拔技术和电池保护功能

- USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

- ROHM开发出适合高分辨率音源播放的MUS-IC™系列第2代音频DAC芯片

- ADALM2000实验:变压器耦合放大器

- 高信噪比MEMS麦克风驱动人工智能交互

- 在发送信号链设计中使用差分转单端射频放大器的优势

- 安森美CEO亮相慕尼黑Electronica展,推出Treo平台

- 安森美推出业界领先的模拟和混合信号平台

- 贸泽开售用于快速开发精密数据采集系统的 Analog Devices ADAQ7767-1 μModule DAQ解决方案

Xilinx FPGA应用进阶——通用IP核详解和设计开发 (黄万伟)

Xilinx FPGA应用进阶——通用IP核详解和设计开发 (黄万伟) 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号