Encounter RTLCompiler与Conformal Equivalence Checking可改进时序、功耗和面积,从而提高竞争力,加快上市时间

加州圣荷塞,2007年3月1日 -- Cadence设计系统公司(NASDAQ: CDNS) 今天宣布,四家亚太芯片设计公司——Altek 公司、互芯集成电路有限公司(CoolSand Technologies)、韩国电子通信研究院(ETRI)以及 Moai电子公司已经选择具有全局综合技术的 Cadence Encounter RTL Compiler解决方案,以改良芯片设计,加快上市时间。Encounter RTL Compiler综合与Encounter Conformal Equivalence Checker是Cadence Logic Design Team Solution的关键技术,搭配Cadence Engineering Services,帮助客户实现其设计进度和满足时序、面积及功耗需求。

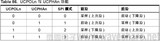

Altek 公司是台湾领先的系统厂商,着力于为数码相机市场提供一站式采购。该公司使用Encounter RTL Complier XL技术进行综合,并使用Enocunter Conformal Equivalence Checker XL技术对其使用某台湾晶圆厂0.13微米工艺的集成电路(IC)进行验证。“使用Encounter RTL Compiler,我们能够优化一个超过220万门规模芯片的时序和面积。”Altek公司ASIC业务部副总裁Simon Law说,“我们目前正在评估在今后的芯片中应用Encounter RTL Complier GXL综合所支持的多供应电压(MSV)和多模式功能,用于推动功能丰富但对低功耗极为渴求的便携成像系统的设计。”

互芯集成电路有限公司是一家系统级芯片设计公司,主要从事移动通信和多媒体设计。Coolsand总部位于北京,在美国和法国拥有研发基地,在中国的深圳和西安设有分公司。它是中国北部第一家采用Encounter RTL Complier解决方案的商业客户。“新一代全局综合工具Encounter RTL Complier具有卓越的性能,可以提高我们的设计效率。”Coolsand总裁梁祖珍说,“Encounter RTL Complier和Cadence First Encounter 硅虚拟原型技术的联合使用,能够帮助我们有效地控制和降低芯片的面积。”

韩国电子通信研究院(ETRI)成立于1976年,是由韩国政府出资的非赢利性研究机构。ETRI的系统级芯片产业促进中心是韩国芯片设计的孵化中心。它允许ETRI使用Cadence的各种技术服务中小型设计公司。ETRI使用Encounter RTL Complier XL综合、Encounter Conformal Equivalence Checker L、和Encounter Conformal Constraint Designer 加速整个设计周转时间。“Cadence Logic Design Team Solution提供了全面的前端解决方案,让我们用更短的时间实现具有竞争力的成效。”ETRI系统级芯片支持中心首席工程师Ho Gil Cho说。

Moai 电子公司是一家位于台湾的、高速成长的无工厂ASIC设计公司,专门从事网络和通信的系统设计,已经成功投片了两种应用于USB相关产品的芯片。“为了保持竞争力,我们需要最好的设计工具,能够应对不断提升的设计挑战。”Moai公司总裁兼CEO PF Lin博士说,“Encounter RTL Complier搭配Encounter Conformal能够帮助我们解决这些困难。”

“Cadence Encounter RTL Complier全局综合在亚太地区被广泛接受,反映了人们对Cadence Logic Design Team Solution技术优越性的不断了解。”Cadence前端设计部全球副总裁Nimish Modi说,“我们致力于进一步推动我们的综合技术,支持该地区高速发展的IC设计产业。”

Encounter RTL Compiler与Encounter ConformalEquivalence Checker是Cadence Logic Design Team Solution的一部分。Encounter RTL Complier能够用更短的时间提供更小、更快、更酷的芯片,而Encounter Conformal Equivalence Checker是业界领先的独立的等效验证解决方案。

关键字:时序 面积 功耗 厂商 编辑: 引用地址:https://news.eeworld.com.cn/news/eda/200703/8446.html

上一篇:瑞萨科技与西安“瑞微”、“风投”合作开发光盘驱动器和数字消费电子产品系统方案

下一篇:NEC退出结构ASIC领域,欲借整合走出困境

推荐阅读

- 芯原戴伟民:海南分公司致力于人才本土化战略,持续为海南输送集成电路产业人才

- 柔灵科技陈涵:将小型、柔性的脑机接口睡眠设备,做到千家万户

- 微灵医疗李骁健:脑机接口技术正在开启意识与AI融合的新纪元

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

最新视频课程更多

- 柔灵科技陈涵:将小型、柔性的脑机接口睡眠设备,做到千家万户

- 微灵医疗李骁健:脑机接口技术正在开启意识与AI融合的新纪元

- USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

- 意法半导体IO-Link执行器电路板为工业监控和设备厂商带来一站式参考设计

IoT开发实战:CoAP卷

IoT开发实战:CoAP卷 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号