消费电子的蓬勃发展,对低功耗技术提出了更为苛刻的要求——在更小空间集成更多功能,而且要求更长的待机时间。乍一看来,这似乎是个悖论:功能的增多意味着功耗的增大,虽然电池每5年提高30%的性能,也远远不能缓解市场对低功耗的需求。聪明的厂商通过不断的技术革新,为我们的消费类产品带来一轮又一轮的技术奇迹。

工艺节点前进,泄露功率凸显

CMOS电路的总共耗由切换功耗、短路功耗和漏电流部分组成。如果你正采用90nm或130nm工艺进行设计,就会明白泄漏在130nm时就是一个问题,当进入90nm和 65nm时会愈加严重。

有报道称,在 90 nm工艺节点时,泄漏消耗 25% ~ 40% 的功率;在65 nm 时,约有 50% ~ 70% 的总功率通过泄漏而耗散掉。这时,即使不需要低功耗的设计泄露功耗也是不可忽视的。

低功耗设计从何时入手?

那么,低功耗设计究竟从何时开始呢?

图1

在产品成功因素中,面市时间是重要因素之一,有时甚至决定着产品的成败。设计早期解决潜在低功耗问题对于提高生产率至关重要。当在RTL代码开发期间解决低功耗问题时,不仅能得到更优化的设计,而且还能提高设计过程中采用的其它工具流程的效率。 因此,设计中,我们不仅要整体考虑芯片设计的各要素,而且应尽量在设计早期引入恰当技术。

降低功耗的技术大集合

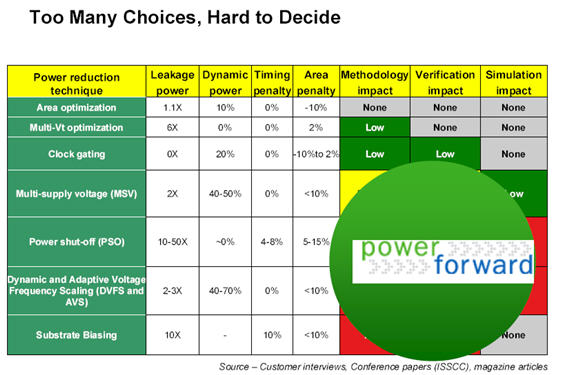

据Cadence公司Encounter数字实现工程副总裁吕丰荣先生介绍,设计师可以采用一系列创新技术降低功耗。通过时序和面积的权衡,以确定所采用的低功耗技术。

1.众所周知,功耗与供电电压的平方成正比,也就意味着我们可以通过降低供电电压从而大大降低功耗。因此,设计师可以在确保不会影响功能的前提下,选择关闭特定模块以节省电力,随后还可以在某时恢复此前状态。依此预计芯片上将会有越来越多的电源线和电压岛。

2.面积优化是提高芯片资源利用率的另一方法,通过面积优化可以使用规模更小的芯片,从而降低成本和功耗,为以后技术升级预留更多资源。

3.时钟网络是最活跃的,通常产生大部分的动态功耗。设计师可以在电路的某一部分处在保持或静止状态时,以适当的条件对时钟进行门控。此法最为广泛使用。

4.自适应电压调节(AVS) 是一个闭环电压控制系统,它无需配对的频率、电压,能提供很好节能效果。而一个典型的DVFS ( 动态电压频率调整 )系统的工作流程包括:1)采集与系统负载有关信号,计算当前负载。2)根据当前负载,预测下一时间段所需性能。3)将预测的性能转换成需要的频率,从而调整芯片时钟。4)根据新频率计算相应电压。

5.亚阈值漏电功耗正随着新工艺发展呈指数增长,90nm漏电功耗是130nm的5倍。电源选通-将电源从逻辑上断开以减小漏电。

6.利用增加基底偏压的方式来降低漏电流,目前这个方法并不普遍。

图2

不同低功耗技术的EDA支持是支离破碎的。结果,设计师不得不通过一系列特殊手段定义低功耗功能,更重要的是,设计的可预测性和验证变得极其困难。

从Common Power Format开始

06年5月,Cadence联合业界领导者提出“功耗前锋倡议”(Power Forward Initiative,简称PFI),旨在连接设计、验证和实现以降低风险,并提高降低功耗的可预测性。成立初期,成员包括AMD、应用材料、ARM、ATI、Cadence、飞思卡尔、富士通、NEC电子及台积电。

通用功率格式CPF(Common Power Format) 是由 Cadence 于06年12月向Si2低功耗联盟提交的,目前CPF1.0作为一个Si2标准向业内广泛传播。Cadence低功耗解决方案是业内最早的全套流程,将逻辑设计、验证、实现与 Si2 标准的通用功率格式相结合。

CPF将功耗 “连”起来

图3

可以想见,当前的设计,逻辑是相‘连’的,所有流程都处理逻辑信息。CPF的出现使得在各个流程中独立的功耗也‘连’了起来。设计师不仅可在整个流程中保存和使用统一的低功耗设计信息,而且能够以统一的设计视角对低功耗SoC设计进行验证、综合和实现。从而有效避免了繁琐的人工操作,大大降低了芯片故障,并在设计初期就提供了功耗的可预测性。

关键字:CPF 时钟 AVS 偏压 编辑: 引用地址:https://news.eeworld.com.cn/news/eda/200711/17062.html

上一篇:NEC 山形将投产40纳米的半导体产品

下一篇:业界呼吁提高电子垃圾回收利用率

推荐阅读

- 希润医疗孟铭强:手功能软体机器人,让脑卒中患者重获新生

- 睿瀚医疗万斌:“脑机接口+AI+机器人”是康复赛道的未来

- 芯原戴伟民:海南分公司致力于人才本土化战略,持续为海南输送集成电路产业人才

- 柔灵科技陈涵:将小型、柔性的脑机接口睡眠设备,做到千家万户

- 微灵医疗李骁健:脑机接口技术正在开启意识与AI融合的新纪元

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

CFP-MSA_CFP4_HW-Spec-rev1.1

CFP-MSA_CFP4_HW-Spec-rev1.1 文章比较了H.264和AVS两个标准在运动补偿中运动矢量预测算法的差别

文章比较了H.264和AVS两个标准在运动补偿中运动矢量预测算法的差别 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号