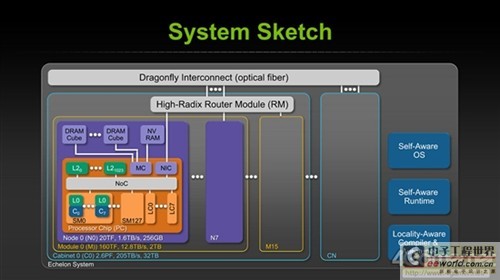

从图上可以看出,Echelon芯片和之前我们报道的相似,各个SM模块独立命名为"NoC"(Network on Chip)通过内部界面,经由L2 Cache和内存控制器与其他SM相互连接。有所不同的是,去年在美国西雅图举行的SC10超级计算大会上NVIDIA首席科学家Bill Dally透露的Echelon含128个SM模块,而在这里变成了256个。

其余指标大致相同,每个SM模块里面含8个SM Lane(类似CUDA Core),芯片中间的8个LOC即Latency Processor也就是Project Denver要制造的主要东西。整体芯片面积为17*17约290平方毫米,采用逼近硅芯片极限的10nm制程工艺制造。(看到这里先别说火星,毕竟DARPA给出的时间表是2017/2018年出最终成果)

CPU核心架构

SM Lane核心架构(不知道是不是Maxwell)

比起来SC10时,Echelon的双精度浮点运算能力降至16TFLOPS,cho称可能是新的数据没有算上CPU的原因。

最新的Echelon模块图解

SC10上的Echelon模块图解

SC10的情况:Echelon由128个SM模块和8个Latency Processor组成,后者就是Denver的核心。

上一篇:谷歌支持x86? Android 4.0 Andtel时代即将来临

下一篇:惠普曾支付7亿美元以让英特尔继续研发安腾芯片

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TS974D

TS974D

京公网安备 11010802033920号

京公网安备 11010802033920号