本次Hot Chips正好是第30届,开幕的欢迎词中简单回顾了会议的历史。比较有趣的是用关键词的方式对比了每十年发生的变化。

Hot Chips 1

Hot Chips 10

Hot Chips 20

Hot Chips 30

今年展示内容最多的三家是:Google(3个talk),Nvidia(3个talk)和Xilinx(4个talk,包括深鉴)。Google不仅talk多,参会的人也不少,感觉确实招募了大量IC领域的人才。Nvidia仍然很霸气,这次Xavier和NvSwith都透露了更多的细节,Xilinx在新CEO上任后也在发力。我会在后面分别介绍他们的工作。另外,ML仍然是热点,除了两个专门的ML

session之外,几乎所有的talk都会涉及到ML/AI,所以我也会写一篇文章专门介绍一下ML相关内容。在详细讨论这些话题之前,先来个流水账吧。

•••

Tutorial

会议正式开始之前的周末是Tutorial时间,上午的区块链相关内容基本是不知所云,就不说了。下午是“Architectures for Accelerating Deep Neural Nets”,包括来自Xilinx的Overview,MIT韩松的“Accelerating Inference at the Edge”,Cerebras的“Accelerating Training in the Cloud”。Tutorial主要是基础,不过内容还是比较丰富,大家如果感兴趣可以去找来PPT看看。

Xilinx的讲座里面有如下一页挺有意思,是在说模型准确度和运算代价(主要由模型设计和量化精度决定)之间的平衡。图中的例子是说,使用Resnet18,8b/8b量化,实现10.68%的错误率;但如果使用Resnet50,虽然模型复杂了,但可以在2b

weight下达到9.86%的错误率,而此时的计算代价从286减少到127。这种trade-off必须考虑更多的因素,意味着需要探索的设计空间会更大,而这可能成为未来神经网络设计的趋势。

在这几个讲座里,我主要关注的是Cerebras这个比较神秘的Startup。不过他们的讲座基本没有涉及任何自己的东西。除了在最后提了一下他们眼里未来的Training加速目标,我们也可以把这个看作是他们要实现的目标吧。

在讲未来的时候他们也把值得关注的竞争对手放在了一起,还专门强调了排序完全是按字母顺序的。

最后,他们还聊了几句关于Benchmark Cheats的问题,有点意思,大家自己去看看吧。

•••

Day 1

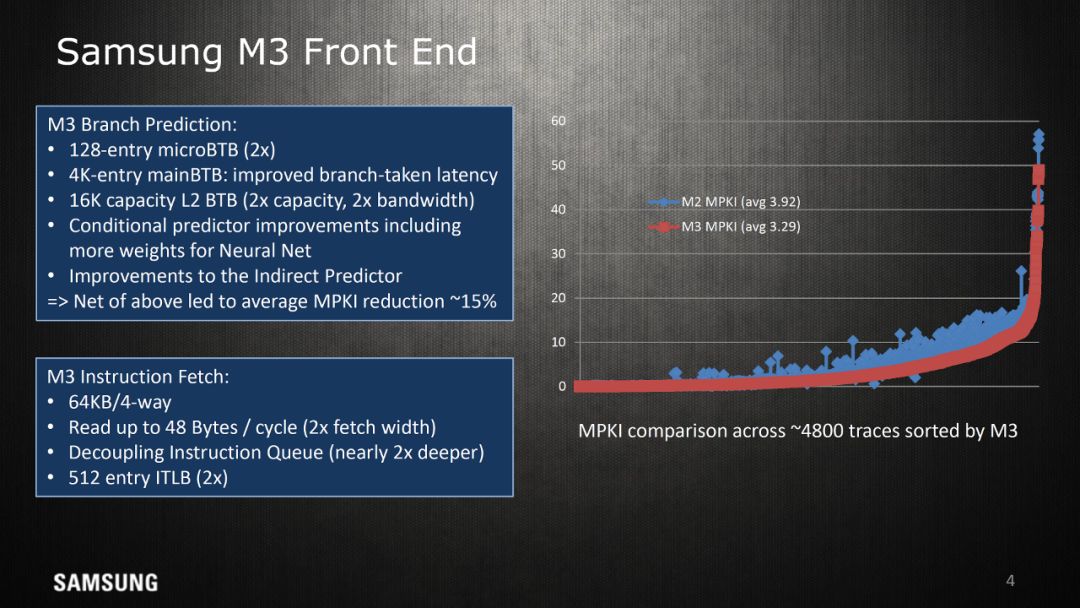

进入正式会议的第一天,第一个session是“Mobile/Pwr Efficient Processors”:有来自三星的“Samsung’s Exynos-M3 CPU”,Google的“ The Pixel Visual Core”,以及UCBerkeley的“BROOM: An open-source Out-of-Order processor with resilient low-voltage operation in 28nmCMOS”。

这次三星透露的M3已经有相关的文章进行了比较详细的介绍,我就不在多说了。讲演中有一页提到“Conditionalpredictor improvements including more weights for Neural Net”,我不是很明白,了解的朋友可以留言介绍一下。

UC

Berkeley的Broom是一个开源的RISC-V设计,其芯片部分我就不多分析了,比较值得讨论的是所谓敏捷开发的问题。这个talk多次强调他们是两个人4个月实现tape-out,还专门提出了Agile

Hardware Development的话题,这可能和他们的导师David Patterson有一定的关系。我们之前的文章(黄金时代)中简单谈到这个问题,DavidPatterson也经常把硬件的敏捷开发和RSIC-V/Chisel联系在一起。

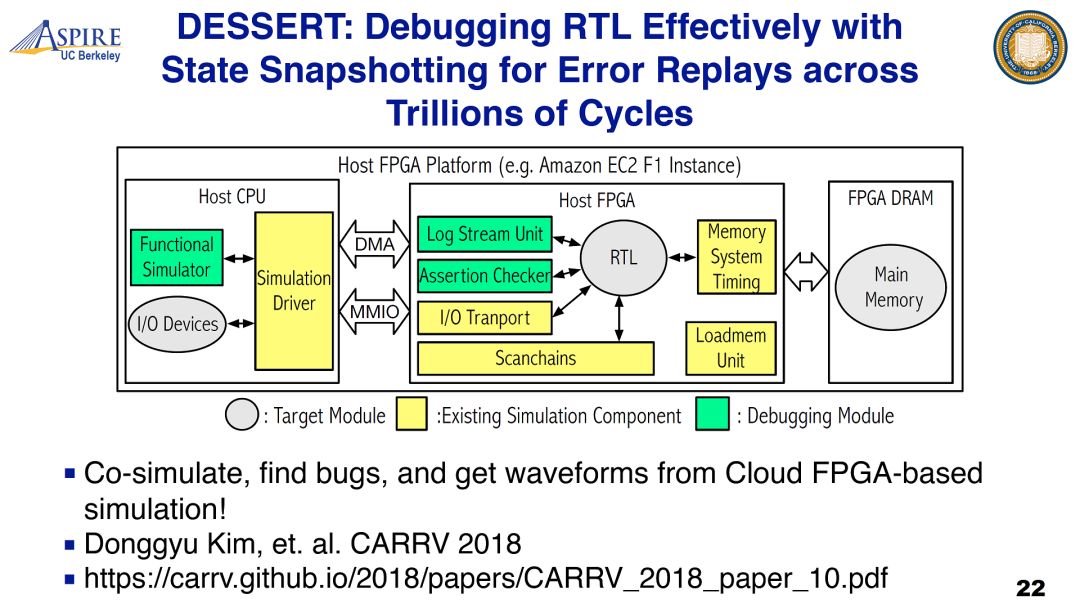

个人感觉这是有一定误导性的,如果仔细看BROOM芯片的设计,这个项目覆盖的内容是比较少的,基本就是BOOM核加cache再加一个简单的到FPGA的I/O接口。因此在设计流程中,需要验证的范围很小。加之是研究项目,综合后端这些任务也可以尽量简化。在这个talk中分享的一些经验顶多算一些技巧。在实际的商业项目是实现硬件的敏捷开发还是非常困难的问题,不是一两个点上的改进就能解决的。最近我们也在研究这个问题,欢迎大家找我讨论。这个talk中提到的DESSERT项目看起来挺有意思,可以关注一下。

第二个session是“Graphics Solutions”:有来自Intel的“Intel’s High Performance Graphics solutions inthin and light mobile form factors”和AMD的“Delivering a new level of Visual Performance inand SoC – AMD Raven Ridge APU”,这个部分没有Nvidia参与,按照我粗浅的认识,好像也没看到什么亮点,就略过吧。

在这之后是大会第一个Keynote:Spectre/Meltdown。讲演阵容很强大,新晋图灵奖得主John Hennessy亲自开场,分析了CPU架构漏洞爆发后,我们对安全问题新的认识。整个Keynote非常详细的分析了这类sidechannel attack的机制和更多的潜在威胁,并从软件和硬件的角度分析了问题的成因和可能的解决方法。总得来说,在过去几十年间,体系结构领域追求的主要是性能和效率,而这次事件确实大大提高了大家对安全性的关注度。但现在谈彻底的解决方法还为时尚早,这基本还是个没有答案的问题。目前能做的基本还是减轻它带来的影响,更多的是Mitigation。大家在后面的讨论中甚至提到要在计算机教育中增加大家对安全性的认识等等。

在讲演中有几个点还是比较有意思,和大家分享一下。首先是对问题成因的一个分析:软硬件割裂的问题。其实在AI系统设计中,我们已经看到更多的软硬件联合设计的趋势。相信未来不仅在应对安全问题的时候,在计算系统设计的时候会更多的采用全栈垂直模型来分析和解决问题。其实也很自然,分割可以简化问题;但优化则经常需要打破边界。当然这也对方法学,工具和模型提出了更高的要求,我们应该会先在Domain-specific的设计中进行更多的实践。这同样也是我们现在在研究的问题,欢迎大家的讨论。

另一个点是对解决方法的讨论,比如这部分最后一个talk提出的Architecture2.0的问题。我们目前遇到的安全性问题,不能说是微结构设计的Bug,而要解决它就需要新的架构规范,虽然我们还不知道是什么样的规范。

对于解决方法的两个讨论:1. 通过使用更多的硬件加速,减少对Speculation的依赖(目前漏洞的主要基础);2. 利用开源硬件的透明特点提高安全性。

当然,总得来说安全问题目前还没有解决方案。但按照Hennessy和Patterson的说法,安全方面的挑战也将是体系结构黄金时代的主要驱动之一。

当然,总得来说安全问题目前还没有解决方案。但按照Hennessy和Patterson的说法,安全方面的挑战也将是体系结构黄金时代的主要驱动之一。

第三个session是“IoT/Edge Computing”,首先是来自Harvard的“SMIV: A 16nm SoC with Efficient and FlexibleDNN Acceleration for Intelligent IoT Devices”。这是个研究项目,主要特点是在SoC中加入了嵌入式FPGA,和支持Cache Coherence的硬件加速器。感觉ARM给了很多支持,主要是围绕ARM的东西在做试验。这里就不细讲了。和之前的BROOM项目一样这里也提到了快速开发的问题,但基本也都是业界比较常用的方式。其中的HLS不知道具体的方法,但从SystemC开始的话应该还是描述了比较详细的硬件特征的,而不是从更抽象的描述开始,大概和Chisel方法类似。

这部分第二个talk来自,MIT

Vivienne Sze团队,“Navion: An Energy-Efficient Visual-InertialOdometry

Accelerator for Micro Robotics and

Beyond”。这是一个视觉SLAM项目,这个应用领域我不是很熟悉,不过据说他们是第一家做芯片的。Sze做的Eyeress项目和DNN

hardware tutorial在AI芯片领域还是很有影响力的,我之前也不止一次做过介绍。这次见到真人,最大的感受就是说话好快。

第一天最后一个部分是“Security”,包括来自微软的“The Hardware Security Platform Behind AzureSphere “和来自Google的“ Titan: Google’s Root-of-Trust Security Silicon ”。前者主要是一个基于云的IoT安全平台,而后者则主要是用专用安全芯片“Titan”解决云端芯片的可信性问题。这个领域我不太熟悉,就不多做评论了。不过Google最后提到会开源它们的“Titan”芯片。如前所述,在安全领域,开放和开源是一种增加可信度比较好的方式。

•••

Day 2

会议第二天的主要内容包括ML,Xilinx也贡献了好几个talk,这些我会在后面的文章中介绍。这里先看看几个相对独立的talk。

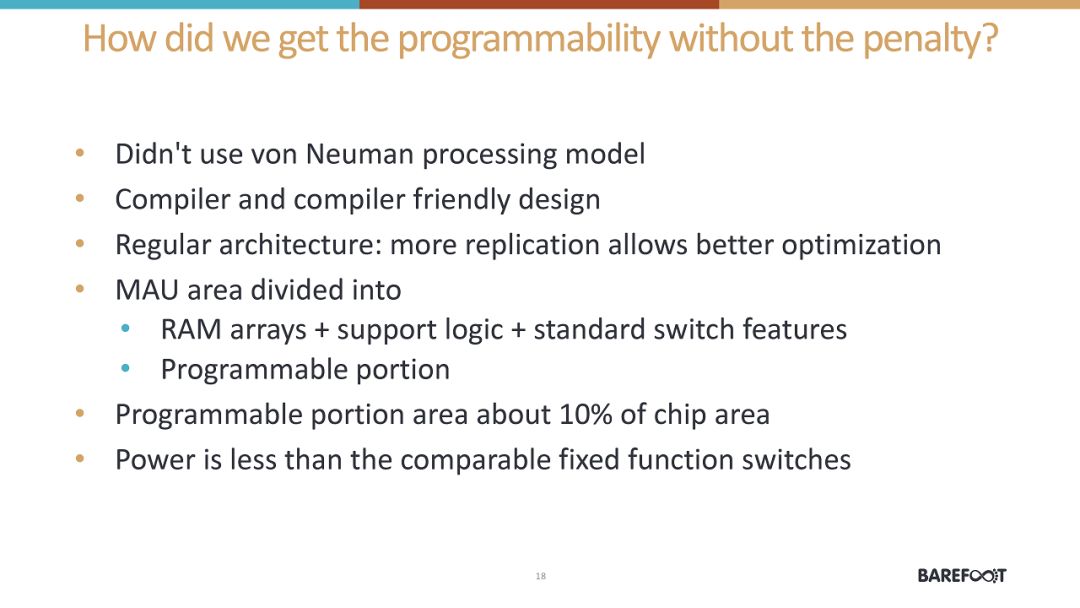

第一个是在“Switching Fabrics and FPGA Architectures”的session中,来自Barefoot Networks的“Programmable Forwarding Planes at Terabit/s Speeds“。在现在的大规模计算环境中网络和网络芯片的作用是非常重要的。这个talk可以作为这个领域一个非常好的综述。

另外,这个talk中提到的”get programmability without the penalty“,是个非常好的问题。

“New Technology” session中,Nantero介绍了“Architecture for Carbon Nanotube Based

Memory(NRAM)

”,即基于碳纳米管的新型存储。这个NRAM和我们之前听到的多种新型NVM存储还不太一样,其目标是替换现在的DRAM。它的基本原理是通过控制碳纳米管的弯曲来控制连接状态。在一个区域里有很多这里的碳纳米管,不同的连接状态可以改变这个区域的电阻,从而实现‘0’,‘1’值的存储。目前看到的各种指标基本可以说是完美,因此在问题环节中的第一个问题就是“It sounds too good to be true. Did I miss something?”不过讲演的哥们估计天天面对这个问题,应对还是非常自如的。结论是除了一点小的限制,基本就是这么牛。所以,我们外行也不好评价了,保持关注吧。

第二天最后一个session是“Server Processors “,这本来应该是Hot Chips的一个重头戏。在做演讲四家,IBM(The IBM POWER9 Scale Up Processor),Fujitsu(Fujitsu High Performance CPU for the Post-KComputer),NEC(Vector Engine Processor of NEC’s Brand-New supercomputer SX-AuroraTSUBASA)和Intel(Next Generation Intel Xeon(R) Scalable processor: Cascade Lake),两家日本公司讲的内容比较丰富一些,不过语言还是有点问题,听的不是很清楚。IBM和Intel讲的东西新的信息不多,而且在大家提问中也经常以无法透露来回答,总体感觉有点无聊。

•••

其它

除了正式的演讲之外,会议还有一些Demo和Poster。正好在会议期间SiFive宣布了一个RISC-V+NVDLA(NVDLA在FPGA上)的系统,好像也有展示。

其它的比如深鉴也做了很好的Demo,可能以后就是和Xilinx一起了。

Poster里面,我本来是比较关注阿里的“Ultra Low Latency and High Performance Deep LearningProcessor “。可惜负责的同学嘴很紧,什么都不说,所以也只能看看作罢。

•••

总得来说,这次Hot Chps 30确实是非常热闹的,注册人数又创了新高。这应该和AI芯片的火热以及非传统芯片公司自研芯片的趋势有很大关系。会上可以看到很多熟悉的面孔,也遇到一些读者,挺有意思。但愿这确实是“黄金时代“的开启,而不是虚假繁荣的投影。

System Management Bus 3.2

System Management Bus 3.2 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号