1 引言

完成某一特定任务的图像处理系统,其硬件方案大体上有三种:使用通用计算机、使用ASIC和使用DSP。使用通用计算机的方案优点在于开发周期短,费用较低,而且产品易于维护和升级;缺点是运算速度受到限制,对于算法的运算量和复杂度很高的应用场合,难以达到实时性要求。该方案有二种应用场合:算法开发初中期阶段及一些实时性要求不高的领域。使用ASIC的方案中,所有的运算都由硬件实现,因此实时性会非常好,但硬件的设计是一大难点,而且系统一旦定型,不方便对其进行升级。使用高速DSP可以说是二种方案的折衷,一方面在硬件实现上只需根据需求进行DSP外围接口电路的设计,另一

方面,随着DSP技术的快速发展,高性能芯片的不断推出,其运算能力也能满足一般图像处理的要求。而且,系统功能由算法软件来实现,对系统的维护和升级也很方便。

本文采用TI公司的多媒体DSP芯片TMS320DM642[4](简称DM642),实现了一种图像处理系统基本功能的应用平台,包含视频输入、视频输出以及串行通信等功能。

2、系统硬件设计

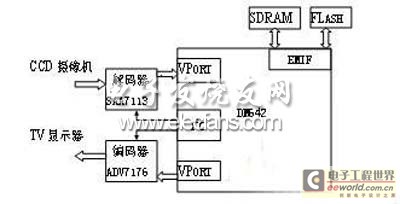

系统硬件组成如图1所示。以DM642为核心,外部扩展了存储器SDRAM和Flash,分别用于程序运行和程序存储;通过控制视频编解码器完成视频的采集和输出;并通过McBSP接口实现UART,方便视觉系统与外界的通信。

图 1 DSP视觉系统硬件组成结构图

系统中,扩展的外部存储器包括ROM和SDRAM。其中,ROM采用Atmel公司的Flash,型号是AT49BV1614,其容量为16MBits,在系统启动时作为Boot ROM使用;SDRAM由两片4Banks×512K×32Bits规格的芯片够成,型号是HY57V643220CT,用来储存程序、数据和视频。视频ADC采用Phillips公司的SAA7113,转换精度9Bits,拥有有4个模拟输入通道,可输入4路模拟视频信号,输出接口(VP0)有一个,支持PAL、NTSC、SECAM这三种主要的模拟视频制式。视频输出DAC芯片采用的是Analog Devices公司推出的ADV7176视频编码器,转换精度为10Bits,最高信噪比达80dB,它在DM642的行、场同步信号及自己的时钟控制下从DM642中读出数据,经过D/A转换后输出到TV显示器上进行显示。通信接口中利用DM642已有的同步串口McBSP与EDMA实现UART的方法,硬件上加入一片MAX3323E,实现CMOS逻辑电平和RS-232逻辑电平之间转换,以满足与控制计算机进行串口通信的要求。

3、系统软件设计

TI为了对自己的DSP 产品提供软件开发支持,推出了DSP /BIOS(Basic Input Output System)抢先型、可裁剪的实时多任务操作系统,它与CCS(Code Composer Studio)编译环境集成在一起。使用DSP/BIOS可以进行高效的应用程序开发。本文图像系统的软件开发是基于DSP /BIOS环境下进行的。3.1 软件设计流程

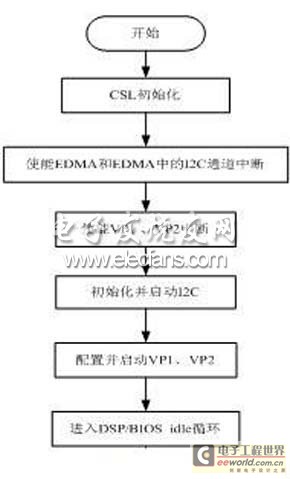

本文图像处理系统的软件流程如图2所示。应用主程序需要先完成CSL(Chip Support Library)库的初始化,以便在程序中能调用相关的芯片级支持库函数。随后,开EDMA中断,并使能EDMA中的I2C通道的中断;开VP1、VP2口中断;初始化并启动I2C的数据传输,完成对视频解码芯片SAA7113和视频编码芯片ADV7176的寄存器的参数初始化数配置;配置和启动VP1和VP2视频口;最后进入空闲等待循环。视频的采集以中断的方式进行,当一帧图像采集完后,触发VP1中断,系统调用相应的中断子程序对图像数据进行处理计算,求出位置和姿态等参数,最后将参数通过UART传输给控制计算机。

图2 主程序流程

DM642 的EDMA 控制器负责片内L2存储器与其它设备之间的数据传输。能提供超过2Gb/s 的外部带宽,有64 个通道, 每1个通道都有1个事件与之关联,由这些事件触发相应通道的传输。上面流程中A/D、D/A的芯片初始化的参数传输和视频数据的采集都是通过EDMA来实现的。

3.2 A/D和D/A芯片的初始化

A/D和D/A芯片的初始化过程通过EDMA中的I2C通道来实现。要传输的数据参数在EDMA 的参数RAM表中进行配置,其中主要包括源数据起始地址、目的地址、地址的修改方式、要传输的数据格式和大小。对二个芯片的初始化数据参数分别配置在二个不同的RAM表中。第一次I2C通道的EDMA数据传输完毕后由EDMA控制器向CPU发出中断,中断处理程序载入第二次I2C传输的RAM参数表,启动第二次传输过程。从而完成二个芯片的初始化过程。

3.3 视频采集与输出

对应于YUV 4:2:2的格式视频数据采集,EDMA中用于VP1的数据传输有三个通道。系统中将视频端口VP1配置为连续帧采集的方式,也就是启动第一帧的采集后,后面帧的采集连续进行不需要另外的帧同步信号。

在隔行扫描模式下,每帧分为两场,两场在时域上是分开的,通过EDMA 链表可自动实现场合成,不需占用额外的CPU 时间。EDMA 的参数RAM 存放了有关的传输参数, 这些参数用于产生EDMA 读写操作所需要的地址。在使用EDMA 通道传输奇数场与偶数场时,分别使用不同的EDMA 参数RAM。两组参数RAM 的目的地址分别指向存储图像的第一行与第二行象素的首地址, 并且两组参数RAM 通过链接地址(Linking Address)循环相连,并将源地址传输方式设置为1维的,目标地址方式设置为2维的。在EDMA 通道的传输中,奇数场传输任务的结束会自动地根据当前参数RAM的链接地址装载传输偶数场的参数RAM,进行偶数场的传输。通过设定帧索引(Frame Index)值可以让奇数场与偶数场数据在帧缓冲区中被隔行存储,这样在无需占用额外CPU 时间的前提下就实现了场合成。另外,由于两组参数RAM 通过链接地址循环相连,则奇数场与偶数场的数据传输连续不断地交替进行下去,这就形成了连续帧的数据采集。每一帧数据通过EDMA传输至SDRAM完毕之后,VP1会向CPU发出一个中断,相应的中断程序对会对采集到的图像数据进行处里。

大批量的图像数据传输和复杂算法的处理一直是高速数字图像处理器的速度瓶颈,从上面的数据传输过程上可以看出, 利用DM642 的EDMA 功能可以在不中断DSP算法处理工作的同时完成图像数据的搬移,在有效地解决了大批量图像数据传输速度瓶颈的同时,又能让DSP 的处理器核专门从事算法处理工作,极大地提高了系统的并行性能。

视频输出功能在本系统中主要用于早期开发阶段的调试。实际应用中可以根据需要将中间处理图像结果数据通过EDMA中的VP2通道直接写入视频FIFO。

3.4 通信接口功能的实现

系统中,通过软件的方法,不增加硬件的复杂度,利用已有的McBSP和EDMA实现UART功能。

同步串口依赖三条分离的信号线(数据、帧同步和时钟)来实现数据的传输,而异步通信只是在一根信号线上进行。要用同步串口实现异步传输,需要通过在数据的首尾加入起始位和停止位,让接收方知道数据传输何时开始和停止。用McBSP实现UART功能,除了对McBSP进行正确设置外,还需要正确设置EDMA,对McBSP收发数据进行软件处理。EDMA实现内存到McBSP之间的高效数据搬移,数据处理软件对待发送的数据进行编码,对接收到的数据进行解码。对McBSP和EDMA的设置及编解码程序的设计详见文献[5]。

4、结论

研究了一种基于DM642的图像处理应用平台的设计与实现,其实现的基本功能包括视频输入和输出,与外界的UART接口通信等。由于软件采用了模块化设计,针对具体的功能需求,通过配置不同的客户程序,可以实现特定的应用,因而系统具有好的应用前景。

上一篇:利用CoolRunner-II CPLD设计GPS系统

下一篇:基于TMS320C6711的数字语音压缩系统

推荐阅读最新更新时间:2024-05-02 21:33

机器视觉技术及应用 (韩九强, 胡怀中)

机器视觉技术及应用 (韩九强, 胡怀中) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号