随着以太网技术的普及和发展,以太网的通信速率从百兆网逐渐进入了千兆网,甚至万兆网,其通信速率已经满足了常用信号处理机所需要的吞吐率。而以前仅用来做信号处理的DSP器件逐渐也加入了以太网通信功能,常见的如TI公司的DM642,C6455,C6678等DSP器件都带有以太网接口,这给一些需要高速通信接口的信号处理板的设计提供了极大的便利。本文利用某处理板上的TI公司高端DSP器件TMS320 C6455,完成了信号处理板与人机界面之间的高速以太网通信功能。系统测试结果表明,利用C6455实现的以太网通信接口完全满足系统设计要求,并且系统具有组成简单、系统集成度高等优点。

1 硬件平台

信号处理板的主要硬件包括两路高速DAC,两路高速ADC以及一块Xilinx V5的FPGA和一块TMS320 C6455DSP处理器,其中网络通信接口部分主要包括C6455、PHY芯片和RJ45接口,如图1所示。C6455的EMAC接口与信号板上的PHY芯片以GMII方式连接,支持千兆双工通信模式。

2 C6455 EMAC接口介绍

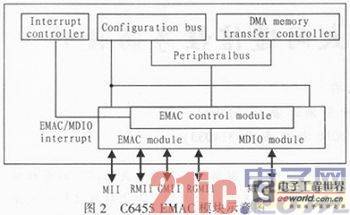

C6455的EMAC接口主要由3部分构成,包括MDIO模块、EMAC模块、EMAC控制模块。其中MDIO模块通过802.3协议规定的串行通信接口,完成以太网物理层芯片的配置和管理:EMAC模块负责以太网数据包的发送和接收;EMAC控制模块作为DSP核和EMAC接口之间的桥梁,实现DSP核对EMAC模块和MDIO模块的控制。

如图2所示,EMAC接口通过C6455提供的外设总线与DSP核连接,外设总线中的配置总线提供DSP核对EMAC寄存器的访问,数据总线完成DSP核与EMAC接口之间的以太网通信包的交换。此外,EMAC控制模块将EMAC模块和MDIO模块产生的18个中断信号综合在一起,对外提供一个中断信号,发往C6455的中断控制器,成为C6455处理器的第17号系统事件。C6455的DSP核在接到中断信号后,通过查询EMAC控制模块提供的中断状态寄存器判断中断产生的中断源。

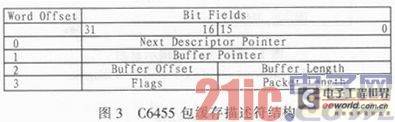

包缓存描述符(Packet Buffer Descriptors)在C6455的网络通信中起到关键的作用,应用程序和EMAC接口之间的信息交换主要是通过包缓存描述符来实现。包缓存描述符的结构如图3所示,每个包缓存描述符大小为16个字节,其中各个域的意义如下:Next Descriptor Poin ter表示指向下一个描述符的指针,这样多个包缓存描述符可以形成一个单向链表;Buffer Pointer表示指向接收或者发送数据内存空间的指针,EMAC模块根据该指针,启动内部的DMA引擎将数据放入到内部FIFO以便发送,或者从内部FIFO读出到该地址,以便应用程序处理;Buffer Offset表示从Buffer Pointer指向的地址到有效数据之间的距离;Buffer Length表示该缓存器指向数据的大小;Flags表示该缓存器指向的数据是否是应用程序数据包的起始包,或是结束包;Packets Length表示应用程序数据包的总长度,应用程序包可能是由一个或者多个包缓存描述符构成。

EMAC模块以链表的形式处理包缓存描述符,描述符链表的第一个地址需要写入EMAC的头描述符寄存器(head descriptor pointer),EMAC从头描述符寄存器指向的描述符开始,逐个处理链表中所有的描述符,直到遇到Next Descriptor Pointer为零的描述符。当链表中所有的描述符都处理完成时,EMAC向DSP核发出一个中断,并将处理完的最后一个描述符的地址写入发送/接收完成寄存器,DSP核通过中断和完成寄存器与EMAC进行发送或接收数据的同步。

3 以太网通信程序设计

文中设计的以太网通信程序是基于TI公司提供的DSP操作系统DSP/BIOS之上,由该操作系统提供时钟定时、任务同步、硬件中断管理等功能。如图4所示,以太网通信程序主要由DSP/BIOS操作系统、网络驱动程序和用户程序构成。DSP/BIOS操作系统为其他模块提供定时、任务同步等服务;网络驱动程序完成以太网通信功能;用户程序负责解释并执行人机界面发送的命令和数据。网络驱动程序主要包括以太网硬件驱动程序和几个基本的网络协议,包括ICMP,ARP和UDP协议,其中,以太网硬件驱动程序的设计是文中描述的重点,其主要包括MDIO驱动程序与EMAC驱动程序。MDIO驱动程序完成C6455 EMAC与物理芯片的交互,而EMAC驱动程序为用户程序提供了以太网通信接口。

3.1 MDIO驱动模块的设计

MDIO模块主要负责搜索、配置和监控外部以太网物理收发芯片。该模块主要包括如下几个部分:MDIO硬件初始化;PHY芯片搜索和配置;PHY芯片状态监控。详细的设计描述如下:

3.1.1 MDIO硬件初始化

MDIO硬件初始化包括如下步骤:

1)读取C6455设备状态寄存器(DEVSTFAT)中的MACSEL位,确定EMAC与PHY芯片之间的连接方式。文中所涉及的信号处理板上的C6455 EMAC与PHY芯片之间采用GMII方式连接。

2)初始化MDIO状态机,将状态机置为初始化状态。

3)配置MDIO访问PHY芯片的时钟并使能MDIO模块。

3.1.2 PHY芯片搜索和配置

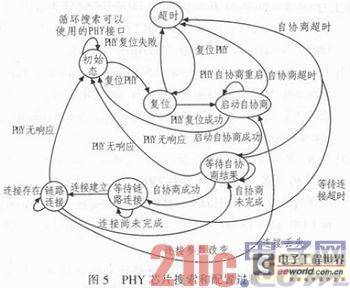

由于PHY芯片的搜索过程并无确定的时间,因此PHY芯片搜索和配置的实现采用状态机来实现,该状态机每隔100 ms根据查询到的PHY芯片的状态完成相应的操作并更新到下一状态,如图5所示。PHY芯片的搜索经过芯片复位,通信速率自协商等过程,最终与通信对端建立以太网物理层连接。

3.1.3 PHY芯片状态监控

在以太网物理层链路的建立后,有可能由于用户拔出网线、对端机器改变通信接口速率等情况而导致链路状态改变,因此MDIO模块需要每隔一段时间对网络进行监控。文中设计的状态监控模块由DSP/BIOS操作系统每隔100 ms查询一次网络状态,状态监控程序一旦发现链路状态有所变化,则根据引起链路变化的不同原因,进入相应的处理流程。该流程如图5中“链路连接”状态以及相应的转移状态所示。

3.2 EMAC驱动模块的设计

EMAC驱动模块主要负责以太网数据包的接收和发送,它是以太网驱动程序的主要组成部分。该模块主要包括如下几个部分:EMAC硬件初始化;EMAC接收模块;EMAC发送模块。各个模块详细的设计描述如下:

3.2.1 EMAC硬件初始化

EMAC硬件初始化主要的目的是将EMAC模块置于就绪状态,此时EMAC已经可以接收和发送以太网数据包。初始化过程主要包括如下步骤:

1)禁止EMAC中断,复位EMAC的HDP寄存器、统计寄存器等,设置EMAC的MAC地址,挂接应用程序提供的回调函数等操作。

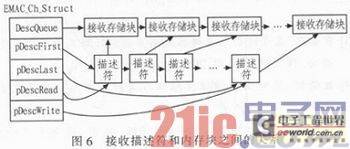

2)根据需求为发送模块和接收模块分配相应的包缓存描述符,并初始化接收模块的包缓存描述符,使之指向应用程序提供的数据接收存储块。文中设计的以太网驱动程序为接收模块分配了32个包缓存描述符,为发送模块分配了480个包缓存描述符,为发送和接收模块共分配了64块存储块,每个存储块大小为4 096个字节。图6是接收模块初始化完成后,接收描述符和接收存储块之间的关系。

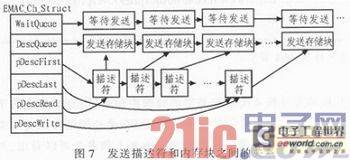

如图6,文中用EMAC_Ch_Struct结构体涵盖了接收模块所用到的链表指针。其中,DescQueue表示空的接收存储块链表,EMAC在接收到一块数据时,启动EMAC内部的DMA,将数据放入当前描述符指向的存储块,并通过中断通知应用程序有数据到达;pDescFirst指向接收描述符链表的首地址,pDescLast指向接收描述符链表的末地址;pDescRead指向第一个可使用的描述符;pDescWrite指向最后一个可使用的描述符;

3)配置MAC的是否为多播地址,使能以太网中断,EMAC处于就绪状态。

3.2.2 EMAC接收模块

EMAC接收模块主要由EMAC中断来驱动。当EMAC硬件接收完一个或多个包数据时,会向DSP核发出一个接收完成中断。DSP核在接收到中断后,调用应用程序提供的接收数据回调函数处理接收到的数据,并返回给中断服务程序一个空闲的存储块,中断服务程序将该存储块重新链接到接收存储块链表,完成接收数据流程。

3.2.3 EMAC发送模块

EMAC发送模块主要由一个发送接口函数ethSendPacket(char*Buffer,int Length)构成,用户程序通过调用该函数完成以太网数据的发送。该函数参数中,Buffer表示应用程序需要发送的数据,Length表示发送数据的长度。该函数首先将Buffer中的数据拷贝到空闲的存储块,并将该储存块加入如图7所示的WaitQueue队列中,WaitQueue队列表示等待加入EMAC发送队列(DescQueue)的存储块。ethSendPacket函数接着检查EMAC发送队列DescQueue是否有空闲的发送描述符,如果有,将WaitQueue链表中的存储块加入到DeseQueue。EMAC硬件将通过相应的描述符,将DescQueue中的数据发送出去。

当数据发送完成后,EMAC向DSP核发出一个发送完成中断。发送完成中断服务程序将发送后的存储块从DescQueue中移除并交还给应用程序,然后将使用过的发送描述符置为空闲状态,以便下次发送数据时使用。

3.3 ARP/ICMP/UDP网络协议模块的设计

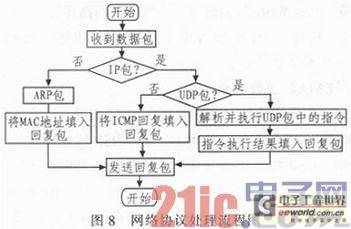

为了与上位机完成网络通信,信号处理机还必须提供基本的网络通信协议。文中在设计时,主要提供了ARP/ICMP/UDP 3种网络协议。ARP协议主要完成信号处理机IP地址和MAC地址的转换;ICMP协议主要完成测试信号处理机与上位机之间的网络连通性;UDP协议主要完成实际指令和数据的通信。

文中简化了这些网络协议模块的设计,设计的主要思路是解析3种协议的包格式,并根据不同协议,封装相应的回应包,发送给上位机。在UDP协议设计中,为了保证数据能够准确送达上位机,加入了CRC校验和出错重传机制。协议处理流程如图8所示。

4 结束语

文中以TMS320C6455为核心芯片,通过对C6455 EMAC硬件的研究,参考相关的以太网驱动程序,完成了C6455的以太网通信程序的设计。结果表明,文中设计的以太网驱动程序以及网络协议模块较好的满足了处理机对实时高效数据通信的基本需求,省却了对信号处理机硬件的修改,降低了系统的复杂度,为其他项目的开发提供了很好的借鉴。

但在对信号处理机网络吞吐性能的测试过程中发现实际的网络吞吐速率与千兆以太网的理论速率还是有较大的差距。如何进一步优化驱动程序的架构和关键数据结构的算法,以便进一步提高网络吞吐率,是笔者下一步的研究方向。

上一篇:FPGA+DSP的高速通信接口设计与实现

下一篇:使用TI 的低功耗C5x DSP的指纹识别方框图和解决方案

推荐阅读最新更新时间:2024-05-02 23:04

- Galaxy S21/ S21 Ultra渲染图曝光了

- iPhone 12 / iPhone 12 Pro 的预购表现好于 iPhone 11 系列

- iPhone 12/12 Pro 官方屏幕维修价格公开:均是2149 元

- LG或不会在2021年上半年发布搭载骁龙875的新机

- 内部文档曝露:目前iPhone 12双卡模式下无法启用5G

- HTC Desire 20 Plus正式推出:骁龙720G芯片售价近2000元

- Mate40发布之后华为或11月推出Nova 8系列新机

- 苹果或将通过软件更新来让iPhone 12支持双卡5G

- 苹果对Apple Watch S3用户发布watchOS 7.0.3:修复意外重启问题

- Apple Watch SE 现过热问题,佩戴者手腕被烧伤

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德)

嵌入式系统软硬件协同设计教程:基于Xilinx Zynq-7000 (符意德) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号