FPGA开发中常用到单脉冲发生器。一些文章介绍过产生单脉冲的电路,产生的单脉冲脉宽和相位都不能与时钟同步,只能用在要求不严格的场合。笔者目前从事的课题中需要一个与时钟周期等宽,相位与时钟周期相同的键控单脉冲发生器。键控单脉冲发生器需要按键产生单脉冲,但大多数带有FPGA芯片的开发板提供的是高频时钟脉冲,按键时会存在抖动问题。为此笔者专门设计了按键消抖电路消除抖动,为产生单脉冲提供稳定的按键信号。

1 按键消抖电路原理

为了使按键消抖电路模块简洁,移植性好,在此用计数器的方式实现按键消抖的功能。

计数器模值n根据抖动信号的脉冲宽度和采样脉冲信号CLK的周期大小决定。计数模值n=延时/脉冲信号采样周期。一般按键抖动时间为5~10 ms,甚至更长。笔者用的开发板提供的系统时钟为24 MHz,按公式计算,当计数器模值取20位,计数到219即h8 0000时,大约延时22 ms。计数期间认为是按键的抖动信号,不做采样;计数器停止计数,认为采样信号为稳定按键信号。这样就可以把按键时间小于22 ms的抖动信号滤掉。

引入一个采样脉冲信号CLK,并输入按键信号KEY。KEY输入低电平,计数器开始做加法计数,当计数到h8 0000即计数器中最高位Q19为1,计数器停止计数,输出Q19,作为按键的稳定输出,计数期间Q19输出为0;KEY输入高电平,计数器清零,Q19输出为0。所以该电路需按键22 ms才会得到有效信号。

2 键控单脉冲发生器电路原理

键控单脉冲发生器利用上述电路解决按键消抖问题,得到稳定的信号。用两个D触发器和一个与门产生单脉冲,如图1所示。

D触发器U2A收到稳定信号D1=1后被触发。触发器U2A中的Q1端得到与CLK同步的正向脉冲。输出Q1到D触发器U3A,得到比Q1延迟一个时钟周期的的正向脉冲,将Q2端输出取反得到一个负向脉冲。Q1与Qn2的输出作为一个与门的输入,会输出一个脉宽是原时钟周期2倍的单脉冲。

为了使得出的单脉冲脉宽与时钟周期相等,相位与时钟周期相同,对图1中电路设计做了改进,如图2所示。

图2中时钟送入D触发器前加了非门,使Q1端产生与nCLK(CLK的反向脉冲信号)同步的正向脉冲,与门输出单脉冲与CLK差半个时钟周期,作为D触发器U4A的输入D4,在CLK上升沿U4A被触发,使单脉冲脉宽与时钟周期相同,实现了等脉宽。并延迟了半个时钟周期使输出脉冲与时钟周期对应,实现了相位调整。整个单脉冲发生器的时序图如图3所示(图3中的t1,t2是任意键按下与键抬起时刻)。

[page]

[page]

3 基于FPGA下的按键消抖计数器和单脉冲发生器的Verilog HDL语言描述

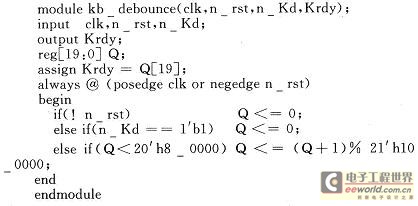

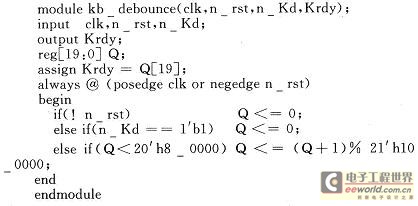

图1中的按键消抖计数器电路,其进行描述的Verilog HDL语言代码如下:

代码中的复位n_rst和按键n_Kd都是低电平有效。键控单脉冲发生器的Verilog HDL语言代码如下:

代码中还用到了D触发器DFF,实现这个模块的代码比较简单,此处从略。

4 结 语

该文中的设计,实现了键控单脉冲发生器,产生脉宽等于时钟脉冲,输出脉冲与时钟周期对应的单脉冲,并解决了按键消抖问题,可以应用到各种需要产生单脉冲的FPGA电路设计中。按键消抖电路可独立地应用于其他FPGA电路设计中。本文中设计的20 b计数器是根据笔者课题需要而定。其他设计中可以根据按键抖动时间可利用公式计算出计数器模值设计计数器。

关键字:FPGA 按键消抖 单脉冲发生器 电路

引用地址:

FPGA开发中按键消抖与单脉冲发生器电路

推荐阅读最新更新时间:2024-05-02 20:58

整流、滤波电路—示波器的使用

示波器是一种常用的电子仪器,主要用于观察和测量各种电信号。配合各种传感器把 非电量转换成电量,示波器也可以用来观察各种非电量的变化过程。示波器有多种类型和 型号,但它们基本原理是相同的。本实验是利用示波器观察周期性改变信号和测量其主要 参数。 交流电的电压(或电流)随时间作周期性变化。实际上,所谓交流电包括各种各样的 波形,如正弦波、方波、锯齿波等。本实验中,我们主要讨论正弦交流电。其原因在于, 正弦交流电在工业中得到广泛的应用,它在生产、输送和应用上比起直流电来有不少优点,而且正弦交流电变化平滑且不易产生高次谐波,用傅里叶分析法可知各种非正弦的交流电都可由不同频率的正弦交流电叠加而成,可用正弦交流电的分析方法来分析非正弦交流电

[测试测量]

基于FPGA的数字核脉冲分析器硬件设计解析

多道脉冲幅度分析仪和射线能谱仪是核监测与和技术应用中常用的仪器。20世纪90年代国外就已经推出了基于高速核脉冲波形采样和数字滤波成型技术的新型多道能谱仪,使数字化成为脉冲能谱仪发展的重要方向。国内谱仪技术多年来一直停留在模拟技术水平上,数字化能谱测量技术仍处于方法研究阶段。为了满足不断增长的高性能能谱仪需求,迫切需要研制一种数字化γ能谱仪。通过核脉冲分析仪显示在显示器上的核能谱帮助人们了解核物质的放射性的程度。 1 数字多道分析仪的优势 国内很大一部分学者采用核谱仪模拟电路的方式实现脉冲堆积的处理。由于整个过程都是由模拟电路来实现,所以一直受到多种不利因素的困扰:模拟滤波成形电路有限的处理能力达不到最佳滤波的要求;

[测试测量]

中环领先集成电路大直径硅片项目开工启动

集微网消息,12月28日,中环领先集成电路用大直径硅片项目开工仪式在宜兴市举行。该项目总投资约30亿美元,是由中环股份携手无锡市政府、浙江晶盛机电三方投建的大型半导体材料研发制造基地,致力于促进无锡集成电路产业链的优化与发展。 据了解,中环领先集成电路用大直径硅片项目是由浙江晶盛机电、中环股份及其全资子公司中环香港、无锡市人民政府下属公司三方共同投资组建,并设立中环领先半导体材料有限公司(简称“中环领先”)运营,中环领先注册资本50亿元,其中浙江晶盛机出资5亿占比10%;中环股份出资15亿(以现有半导体资产出资),占比30%;中环香港出资15亿,占比30%;无锡市人民政府下属公司出资15亿,占比30%。 中环股份副总经理、董秘秦世

[手机便携]

上海临港今年集成电路总投超千亿元,国内领军企业集聚

日前,在上海市政府新闻发布会上,上海市发展改革委副主任朱民表示,临港新片区焦集成电路、人工智能、生物医药、航空航天等产业的核心领域和关键环节,建立健全功能性产业政策和制度体系,强化与长三角地区的产业布局合作,引领带动国内相关产业链的高级化进程。 朱民还表示,近期,临港新片区还将重点建设“东方芯港”“生命蓝湾”“大飞机园”和“信息飞鱼”四大重点产业园区。预计到今年年底,仅集成电路领域的落地项目总投资就将超过 1000 亿元。 就在今年 6 月,临港新片区自挂牌以来已有 40 余家集成电路产业相关的企业落地,形成了 IC 设计、制造、封装、测试、材料、装备等全产业链。目前集成电路在新片区落地企业数占四分之一。临港新片区管

[嵌入式]

加速FPGA发展,英特尔助绘中国数字经济新蓝图

三年前,被誉为“西部硅谷”的重庆引入英特尔全球最大、亚洲唯一的FPGA中国创新中心,将其视为重庆数字经济建设的重要一环。三年后,数字经济蓬勃兴起,成为助推中国经济的新引擎。在刚刚闭幕的两会上,政府工作报告指出,“十四五”时期将加快数字化发展,打造数字经济新优势,协同推进数字产业化和产业数字化转型,加快数字社会建设步伐,提高数字政府建设水平,营造良好数字生态,建设数字中国。 在此背景下,作为近年来深度参与中国数字经济建设的重要一员,英特尔FPGA中国创新中心日前宣布加入“重磅” 新成员英特尔FPGA PAC N3000,用于多工作负载网络基础设施和应用加速,支持移动和电信行业应对互联网协议流量和5G部署的激增,再度引来业界高度关

[嵌入式]

辐射对FPGA应用的影响及解决方案

以前很多人认为,半导体器件只会在太空应用中受到辐射的影响,但是随着半导体工艺的进步,很多地面的应用也会受到辐射的影响。今天,我们会介绍不同的辐射效应和对FPGA的影响,比较不同的FPGA的耐辐射性。 辐射的影响 按照是否能造成原子或者分子的电子脱离,辐射主要分为电离性和非电离性两大类,如图1所示。高能粒子或者电磁波包括X射线和γ射线都能够产生电离的作用。半导体器件受电离性的辐射影响较大,日常应用中以粒子引起的电离性辐射最常见,而其中,以α粒子和中子的影响力较大。 图1 辐射分类 对于太空和地面的应用而言,辐射效应可以分为两大类,单事件效应(SEE)和总离子剂量/总剂量(TID)。在对地面的应用中,单事件

[嵌入式]

基于DSP/FPGA的超高速跳频系统基带设计与实现

跳频通信 系统作为扩频通信体制中的一种重要类型,以其出色的抗远近效应、抗干扰能力,在军用、民用通信领域得到了广泛应用。跳频通信方式是指载波受一伪随机码的控制, 不断地、随机地跳变,可看成载波按照一定规律变化的多频频移键控(MFSK)。跳频通信的频率受伪随机码控制不断跳变,跳频图案可以设置几千乃至上万个,收发两端只要跳频图案一致,跳频时间同步,就可在信息传输过程中不断跳变空间频率信道,实现跳频通信。 近年来随着半导体工艺和计算机技术的发展, DSP (Digital Signal Processor )、 FPGA (Field Programmable Gates Array)等现代信号处理芯片越来越成熟和普遍使用,以前只能理

[嵌入式]

数字功放中的限幅压限电路分析

1、背景介绍 如下图,当我们对着话筒说话或者唱歌时,声音通过话筒传到功放,将声音进行放大。正常情况下,音频信号的幅度有高有低,也就是说话声音有大有小,但也可能出现较长时间处于比较高的幅值的情况,幅值越高,功放输出的功率越大。 如果持续输入幅值较高的信号,功放就一直处于功耗较大的状态,里面的管子发热就很严重,甚至烧毁。这时候我们就要用到限幅压限电路。 限幅压限电路的作用是功放设备在长时间处于高幅值输入时,通过反馈,将输入信号无失真的进行缩小(路径②),待管子温度降到正常范围,又继续正常工作。 在我们平时使用功放时,为什么我们说话或者唱歌没有明显感觉到声音变小了呢?那是因为我们研发早就设计了参数,做了充分的实验,尽可能保证不影

[嵌入式]

[page]

[page]

《汽车电路维修》复习题

《汽车电路维修》复习题 新能源电路分析及常见故障与诊断

新能源电路分析及常见故障与诊断

京公网安备 11010802033920号

京公网安备 11010802033920号