前言

电子技术的飞速发展,尤其是消费类电子产品在成本、产品功能及品质的更高要求,使消费类电子产品的设计不是简单地要求设计出来,而是要考虑低成本高品质。 CPLD的成本低,占用PCB面积小,功耗低和灵活的后期可编程特性在嵌入式设计中得到越来越广泛的应用。

由于CPLD资源较小,大部分工程师都用CPLD来实现整合逻辑电路,扩展主处理器的I/O功能,或做电源管理功能,由于CPLD内部没有振荡器,而振荡器的功能对于CPLD做电源管理,产品的系统管理尤为重要,如果在CPLD外部加一个振荡器就增加了整个设计的成本。利用CPLD内部的反向器,再加上外部简单的RC,即可以实现一个简单的振荡器供CPLD内部设计使用,可以降低设计成本,灵活性强,稳定性高。

CPLD内部施密特触发器

CPLD内部施密特触发器电器特性见表1。目前大部分使用的CPLD都需要两个电源VCC和VCCIO,VCC就是CPLD内部的核电压,VCCIO是CPLD所有I/O 引脚电压。

从表1看出,VT+和VT-是取决于VCCIO的电压。目前大部分设计都选用VCCIO为3.3V,所以,VT+ (min.) = 0.5 × 3.3V = 1.65V,VT+ (max.) = 0.8× 3.3V = 2.64V

VT- (min.) = 0.2 × 3.3V = 0.66V VT-(max.) = 0.5 × 3.3V = 1.65V

从上面给出的VCCIO 为3.3V计算可以看出,对于施密特触发器当输入电压在1.65V下输出都为低电平,当输入电压在1.65V之上都为高电平,1.65V为高低电平的临界点。

[page]

[page]

振荡器实现

利用CPLD内部的施密特触发器使输入波形得到校正,再加上反向器反向和外部RC实现振荡器,只需要在使用CPLD的任意两个I/O PIN引脚(当然从CPLD内部原理来看最好是使用相邻的两个PIN引脚,会减小CPLD内部资源的占用)。其中一个PIN 引脚串入电阻,外接一个对地电容,当内部的A点为高电平时,PIN1会通过R1对C1充电,由于电容的电压不可越变,电压是对电流的积分,所以电压会逐渐上升,当电平上升至0.5 × VCCIO,CPLD施密特触发器才认为是高电平,再经过内部的反向器会反向,所以A 点会变成低电平,这时C1 会通过R1逐渐放电,当放电电平低于0.5 x VCCIO时,反向器反向A点又变回高电平,这样反复的振荡就构成了一个稳定的振荡器时钟源(见表1)。

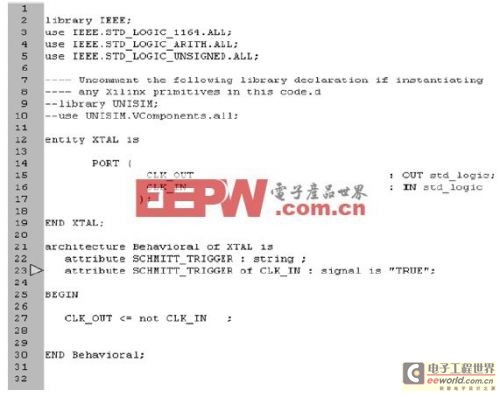

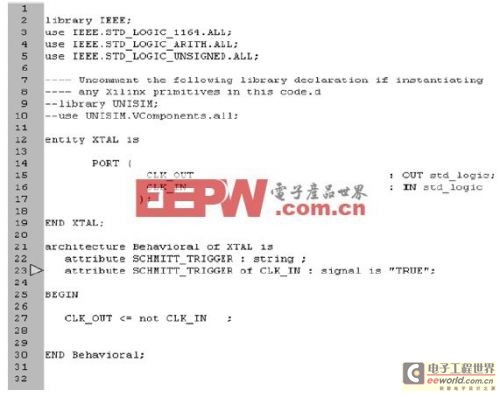

CPLD实现代码

本设计使用VHDL语言,选用XILINX 公司的COOLRUNNER-II系列的CPLD器件, 基于0.18nm CMOS CPLD, 3.8ns PIN-to-PIN延时,快速JTAG下载,2个bank,具体实现见代码列表。[page]

振荡器应用

上述代码通过XILINX的编译综合器后,会产生一个可下载档案,此档案可以通过JTAG直接下载到芯片中使用,由于代码示例的为一个实时振荡器,也就是只有芯片上电,振荡器部分会一直工作,对于用于电源管理的嵌入式产品设计,由于一直振荡带来额外的电功耗损耗,功耗的损耗和振荡的频率是相关的,当频率越高时,功耗越大。所以,设计还可以再被优化使用。比如,当符合什么条件时振荡器才开始振荡,或者达到什么条件时振荡器停止振荡,这样灵活的优化设计会给产品带来更多的附加价值,延长电池的使用寿命。

振荡器的振荡频率是通过外部引脚的电阻和电容来调整的,当电阻越小,电容越小时,振荡的频率就很高。当电阻很大时,电容也变大,振荡的频率就会变低。振荡器的精度取决于外面电阻和电容的精度,电阻的精度以现在工艺可以做到1%的正负误差,电容可以选择5%的正负误差,高精度的电阻和电容会带来比较精准的振荡频率。

结语

本文的设计充分利用了CPLD内部的硬件资源和VHDL灵活严谨的编程和外加简单的RC实现了一个振荡时钟源,既可供CPLD内部设计使用,也可以供给外部其他设计使用,该设计减小了设计的复杂性,通过CPLD的灵活可编程性降低了产品的成本,具有一定的商业应用价值。

关键字:CPLD 振荡器 反向器 施密特触发器

引用地址:

基于CPLD内部的反向器实现振荡器应用

推荐阅读最新更新时间:2024-05-02 21:14

精密幅度稳定的低失真正弦波振荡器的设计

很多应用都需要频率和/或幅度稳定的正弦波做为定标或测量的参考。对于LVDT信号调理、ADC测试、谐波失真测试等应用也要求低谐波失真。很多正弦波产生技术不可能简单地实现精密正弦波参考所要求的低谐波失真和幅度稳定度。本文所示的正弦波产生技术能实现小于0.003%失真和0.1幅度稳定度。 图1示出1个简单的振荡器 电路 ,它是由1个Wein桥振荡器核心和1个幅度稳定回路组成的。Linear公司的LT1632高速低失真放大器和正反馈RC网络产生振荡。由LTC1968RMS-DC振荡器、LTC2054缓冲器和LTC1632误差放大器构成的负反馈回路 控制 正弦波的幅度和幅度稳定度。 图1 精密幅度稳定的低失真正弦波振荡器电路

[模拟电子]

收购不到 2 年,AMD 弃用 Xilinx CPLD 芯片

1 月 18 日消息,AMD 公司近日发布产品停产通知,表示不再提供所有 CoolRunner 和 CoolRunner II CPLD 芯片,以及 Spartan II 和 Spartan 3 FPGA 芯片。 停产通知写道: 由于运行率下降和供应商可持续发展的原因,AMD 将停产 XC9500XL、CoolRunner XPLA 3、CoolRunner II、Spartan II 和 Spartan 3、3A、3AN、3E、3ADSP 等商业 / 工业“XC”产品,以及面向汽车行业的“XA”系列产品。 AMD 在通知中明确砍掉现有 CPLD 或 FPGA 芯片之后,不会提供任何直接替代产品。AMD 公司如果未来选择不再

[半导体设计/制造]

用CPLD实现DSP2407A与S3C4480的通信

在现代汽车电子中,一般有多个微控制器共同协调工作。DSP控制器采用哈佛结构,运算速度快,所以在汽车电子中广泛采用DSP芯片来实现汽车动力系统的控制。ARM是一种32位微控制器,有丰富的外扩接口,因此在汽车电子中一般用ARM来实现大容最的数据存储和人机交互或GPS全球定位系统,故在DSP和ARM之间需要进行数据交换。 CPLD(Complex Programmable Logic Device)是一种复杂的用户可编程逻辑器件,由于采用硬件可编程技术,从而使没计硬件电路也像设计软件一样方便。DSP2407A是T1公司设计的一款专为满足大范围的数字电动机控制应用的微控制器。S3C4480是三星公司专为手持设备设计的高性价比的微控制器。本设

[应用]

采用CPLD增强单片机P89C669外部设备扩展能力

P89C669是PHILIPS半导体一款51MX(存储器扩展)内核的微处理器,其指令执行速度2倍于标准的80C51器件,线性地址经扩展后可支持高达8 MB的程序存储器和8 MB的数据存储器,这是他相对于标准51内核的最大优点。目前的单片系统越来越复杂,扩展的外部设备也更多,如果能充分利用P89C669的丰富的线性地址资源,将能大大增强系统能力。在一个嵌入式系统开发中,笔者采用ALTERA公司的CPLD芯片EPM7032利用这款单片机的线性地址扩展了丰富的外部设备资源。 1 P89C669的存储器结构 1.1 存储结构 P89C669的存储器结构为哈佛结构,地址分配如表1所示。 从表1可见,P89C669对传统的51内核

[单片机]

基于DSP与CPLD的I2C总线接口的设计与实现

带有I2C总线接口的器件可以十分方便地将一个或多个单片机及外围器件组成单片机系统。尽管这种总线结构没有并行总线那样大的吞吐能力,但由于连接线和连接引脚少,因此其构成的系统价格低、器件间总线连接简单、结构紧凑,而且在总线上增加器件不影响系统的正常工作,系统修改和可扩展性好。即使有不同时钟速度的器件连接到总线上,也能很方便地确定总线的时钟。 如今,为了提高系统的数据处理精度和处理速度,在家用电器、通讯设备及各类电子产品中已广泛应用DSP芯片。但大多数的尚未提供I2C总线接口,本文将介绍一种基于CPLD的已实现的高速DSP的I2C总线接口方案。

1 I2C通信协议

I2C总线是一种用于IC器件之间的二线制总线。它通过SDA(串行

[嵌入式]

基于CPLD与μC/OS -Ⅱ的断路器智能控制单元设计

本文介绍的智能控制单元采用数字信号处理器(DSP)及嵌入式实时操作系统完成各种数据的处理、通信和算法的设计,而状态量的采集和执行信号输出将由复杂可编程逻辑器(CPLD)完成,主要是基于CPLD内部硬件电路结构的可靠性和对状态采集的实时性,该系统可以满足系统控制实时性及可靠性的要求。 硬件设计 TMS320F2812DSP介绍 TMS320F2812DSP是德州仪器公司(TI)推出的32位高性能数字信号处理器,它具有峰值运行每秒150万条指令(MIPS)的处理速度和单周期完成32×32位MAC运算功能,同时它还具有128k×16的片上Flash,18k×16的片上RAM以及大量的片上外设,包括A/D转换模块、2个事

[嵌入式]

基于CPLD的LED显示屏控制电路设计

引言 近年来,随着计算机技术和集成电路技术的飞速发展,得到广泛应用的大屏幕显示系统当属视频LED显示系统。在LED显示技术中,由于红色、绿色发光二极管的亮度、光效色差等性能也得到了很大的提高,加之计算机多媒体制作软件的发展,现在伪彩视频LED显示系统的制造成本大大降低,应用领域不断增加。这种伪彩色视频LED显示系统采用了计算机多媒体技术,全同步动态显示视频图像,图像清晰,亮度高,无拼缝,每种颜色的视频灰度等级已经由早期的16级灰度上升现在的256灰度,随着大规模集成电路和专用元器件的发展,256级灰度的全彩色视频LED显示系统随时都可能实现。 LED电子显示技术发展迅速,已成为当今平板显示领域的主导之一。本文着重介

[电源管理]

循环冗余校验码的单片机及CPLD实现

摘要: 循环冗余码校验(CRC)是一种可靠性很高的串行数据校验方法。介质循环冗余码校验的基本原理,并分别用单片机和CPLD作了循环冗余码验的软件实现和硬件实现。包括汇编语言和VHDL语言源程序。

关键词: 差错校验 查表法 CPLD

1 基本原理

串行数据的差错检验是保证数据正确的必要手段,通常采用奇遇校验法和循环冗余校验法。这两种方法都是通过冗余数据来提供必要信息。奇偶校验法适用于以字节为单位数据传输。例如用偶校验传送1个ASCII字符时,要附加1个校验位,从而使全部9位中“1”的个数为偶数。奇偶校验简单易行,但当数据崩溃或出现多位错误时,往往不能检验出来,因而可靠性不高。

循环冗余码

[应用]

[page]

[page]

电路与模拟电子技术(第三版) (殷瑞祥)

电路与模拟电子技术(第三版) (殷瑞祥)

京公网安备 11010802033920号

京公网安备 11010802033920号