红外成像技术是目前非常有用的新型高科技,具有极强抗干扰能力,属于被动式观测装备,隐蔽性很强。长波红外可不受烟雾等的影响,分辨率高。另外,红外成像不受地面和海面的多径效应影响,具有多目标全景观察、追踪及识别能力,具有很广阔的应用前景和价值。

本文采用的红外系统为凯迈广微160×120系列,由于原始图像大小为160×120,在某些应用场合其分辨率很难满足需要,必须对图像进行放大。

图像放大是一种常用的数字图像处理技术,在日常社会生活的许多领域有着广泛的应用,因此数字图像的放大是图像处理的基本操作之一。数字图像放大多用软件来实现。但随着现场可编程门阵列技术的突飞猛进,FPGA也逐渐进入数字信号处理领域,尤其在实时图像处理方面FPGA无可比拟的并行处理能力,所以国内外愈来愈多的实时处理应用都转向了FPGA平台。本文正是介绍了一种基于FPGA的固定倍率红外图像放大模块。

1 图像放大算法

目前图像放大处理通常都采用软件方法来实现,虽然其算法种类多样,且图像放大后的质量也比较高,但是,由于其运算时间往往较长,因此在某些实时性要求较高的数字图像处理场合不宜采用软件方法而适合采用硬件方法。硬件方法实现图像放大,其处理速度可大大提高,不过,采用硬件实现时,由于资源非常有限,许多处理算法因过于复杂而无法通过硬件实现。目前在进行硬件图像处理过程中,通常采用插值算法,利用图像的像素点间存在着的相关性进行插值而实现图像的放大。常用的差值算法包括最近邻域插值法(Nearest Neighbor Interpolation),双线性插值法(Linear Interpolation),双三次插值法(Bieubie interpolation)。

1.1 最近邻域插值法

从计算量的角度来说,最近邻插值是最简单的插值。在这种算法下,每个插值输出像素的值就是在输入图像中与其最临近采样点的值。算法的数字表示为:

f(x)-f(xk),1/2(xk-1+xk)

1.2 双线性插值法

双线性插值法的输出像素时它在图像中2×2邻域采样点的平均值,它根据某个像素周围4个像素(m,n),(m+l,n),(m,n+1),(m+1,n+1)的灰度值在水平和垂直2个方向对其插值。

设m

把按照上式计算出来的值赋予图像的几何变换对应于处的像素,即可实现双线性插值。

1.3 双三次插值法

双三次插值的插值核为三次函数,其插值邻域的大小为4×4。它的插值效果比较好但相应计算量也大。

1.4 本文采用的算法

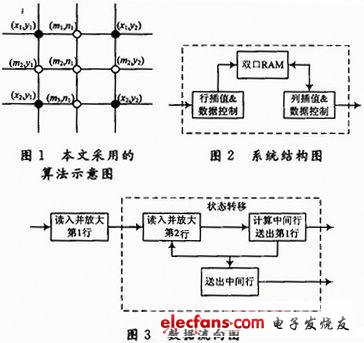

上述3种图像插值算法中最近邻插值放大实现最为简单,处理速度快,但它只是把原始像素简单的复制到其邻域内,放大图像就会出现明显的方块或锯齿,不能很好地保留原始图像的边缘信息。双三次插值算法的视觉效果最好,但计算复杂开发周期长,占用的硬件资源较大,不符合本系统的资源要求。使用双线性插值能够较好地消除锯齿,保留原始图像的边缘信息,放大后的图像较平滑,且有较好的视觉效果。本文选取改进型的线性插值(2×1邻域和1×2邻域)作为最终实现方案。如图1所示,实心表示原始像素,空心表示放大后的图像。本文采用的算法数学表达式为:

2 算法基于FPGA的设计与实现

2.1 系统结构

系统总体结构如图2所示,行插值和数据控制模块控制数据存入双口RAM中,并在存入的过程中实现行的放大,因为采用2×2领域放大,每个目标像素放大所需的原始图像相邻2行的2个像素,所以可以将相邻2行写入双口RAM。列插值和数据控制模块实现列放大和把插值后的数据送入到下一个模块。数据流向是图像放大模块的重点和难点,如何实现实时性,良好的数据控制很重要。在数据从上一个模块读入的同时,行插值模块就完成了行放大。在一帧图像的帧头,行插值模块对2行数据进行操作,在第2行到倒数第2行,行插值只对单行数据进行处理,处理完毕后并通知列插值模块进行下一步运算。列插值模块在收到行插值模块给的信号后,从双口RAM中读取已经存入的两行数据,并完成中间行的插值,在运算的过程中并把RAM中的第一行的数据逐个读出并送到下一个模块。当完成列插值运算后,立即通知行插值模块开始读入新的一行,并在读入的同时,把新产生的行读出。行插值模块完成新的一行读入后,通知列插值模块与RAM中上一次存入的第二行(第一次列插值的第3行)进行列插值操作,并重复上述操作,直至完成当前帧。具体流程如图3所示。

2.2 算法实现

图像处理模块的具体实现结构如图4所示。该模块由3个部分构成:ram_control模块实现RAM控制和行放大;calculate模块实现列放大和数据输出;dpram为双口RAM用于数据存储。

(1)ram_control模块。D_SYP为2倍的像素时钟输入,SYP为像素时钟,SYL为行同步信号,G_reset为全局复位信号,data_in为数据输入端口,cal_done为列运算完成信号指示,done为行放大完成信号,其余信号为dpram控制信号。

(2)calculate模块。caleulate模块与ram_control模块功类似,再运算完成后可以控制数据输出到下一个功能模块。

(3)dpram。dpram可以实现不同速率的输入和输出,还可以根据需求改变同一个RAM口的不同速率的输入和输出,本文采用了两路不同的时钟分别控制ram_a口和ram_b口,同一个口用同样的时钟读入读出数据。

3 系统仿真与实现

图5为quartus功能仿真结果,时钟速率和数据输入均为模拟产生,根据仿真结果可以看出,地址发生器和数据输出均按照设计要求输出,理论上可以实现放大功能。

图6为红外机芯组件GW160×120所采集到的原始图像,图7为采用本文放大算法后采集到的图像。对比发现图像质量较好,没有马赛克现象,可以满足观察需要,达到了设计要求。

4 结语

在以后的应用中如果硬件资源满足需求,可以把双三次插值应用于红外机芯系统。由于系统采用了FPGA进行设计,因此具有很强的扩展性,可以在不改变硬件系统的基础上进行算法改进,增加了系统的灵活性和适应性。

上一篇:CPLD初学者入门知识

下一篇:基于GPS无源雷达干扰抑制研究

推荐阅读最新更新时间:2024-05-02 21:44

【模拟工程师】电路设计指导手册:运算放大器

【模拟工程师】电路设计指导手册:运算放大器 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号