0 引言

在数字接收机的各种参数中,频率是最重要的参数之一,它能反映接收机的功能和用途、以及频谱宽度等重要指标。传统的顺序测频技术一般通过对接收机频带的扫描,对频域进行连续取样。该方法原理简单,技术成熟,但是,其频率截获概率与分辨力的矛盾难以解决,无法实现全概率信号截获。而多信道化的频率检测技术属于瞬时测频,其架构是采用多个频率窗口(多个信道彼此衔接相邻)来覆盖接收机的整个频段,这样,当信号进入任一个窗口时,该窗口的频率值即可被检测出。因此,该方法可解决频率截获概率与频率分辨力的矛盾,同时也为实现全概率频率捕获提供了一种参考方案。

1 多信道模型

当一个实信号经过A/D采样之后,再进行正交下变频处理,即可得到I、Q两路相位正交信号,它们所构成的是一个复信号。该复信号的信道化示意图如图1所示。

图1所示的信道是一种相互交叠的信道,它们涵盖了整个零中频信号的频率范围。一般情况下,多信道往往采用数字滤波器组来实现,但该方法需要设计M(M为信道数)个中心频率不同,而其它性质完全相同的带通滤波器。这种结构设计过于复杂,同时还加大了后续信号处理的运算速度,对实时处理极为不利。而数字滤波器组的低通型实现方法则是先将每个通道乘以一变换因子,就相当于将实际信号搬移到零中频,然后再通过LPF得到该频率信号。该方法可对带通信号的频段进行信道化分离,但是带来的新问题是当LPF用FIR滤波器实现M个滤波运算时,将占用较大的硬件资源,而且系统工作效率较低。目前,该结构已被高效DFT多相滤波器组结构所代替。

图2所示是一种具有普遍性的基于DFT多相滤波器组的信道化高效结构,从图2中可以看出,在滤波之前,先对数据进行D倍抽取可降低滤波过程的运算量,gn(m)是低通原型滤波器hLP(n)的多相分量,其阶数可减小到原来的1/D,因而DFT可以用FFT实现。事实上,在此结构中,系统的复杂度和数据速率大大降低,实时处理能力得到了提高。 [page]

2 滤波器的设计及仿真

低通型滤波器结构中的每个通道都是由原型低通滤波器乘以旋转因子形成的。根据要求,图3所示是由256阶原型低通滤波器形成的滤波器组及其信号输出仿真波形。该信号的有效带宽为300MHz,共分为32通道,每通道带宽为9.375MHz。如给此滤波器组送入频率?=28.1MHz的单频信号,那么,通过理论计算可知,信号应在第3号通道有输出。图3 (b)所示就是第2、3、4通道的输出仿真结果,可以看出,仅第3个通道有比较强的信号输出,这与理论上的计算结果是一致的。

3 实现方案

本设计选用的FPGA芯片是Xilinx公司的Virtex-4SX55,该芯片时钟资源丰富,算术运算单元和专用存储模块以及可配置逻辑的使用都很灵活,非常适合当前信号处理系统的功能实现。因此,根据图2所示的结构,就可以得到一种基于DFT多相滤波器组的信道化解决方案,其具体实现结构如图4所示。

图4所示结构由延时器、系数存储器、乘加器和FFT组成。其中延迟器可实现对输入数据32个周期的延时,存储器用于存储滤波器系数。下面对该结构中几个主要组成模块的实现及仿真结果进行介绍。

3.1 延时器的实现

本延时器采用FPGA提供的专用存取模块FIFO来实现32周期延时,其架构体系如图5所示。图中,每个延迟单元即是一个FIFO模块,FIFO的数据输出特点为先入先出。在本设计中,第一级延迟器的输出数据将作为下一个延迟器的输入数据,就相当于第一级FIFO的数据按先进先出的顺序依次向第二级FIFO压入,相邻两级的将满标志与读使能信号进行握手协议,从而实现数据的延迟输出。这样,设计8个同样结构的FIFO并进行串行级联,即可满足该结构的设计要求。

[page]

3.2 系数存储模块

对于256阶原型低通滤波器,可以将h(0),h(1),…,h(255)这256个系数分成八组,每组32个,分别存储到八个存储器当中,存储器0存储的系数为:h(0),h(1),…,h(31);存储器1存储的系数为:h(32),h(33),…,h(63);以此类推。存储器可使用逻辑(LUT)实现,也可使用专用存储模块Block RAM来实现。FIFO中的目标数据和存储器中系数做乘法运算时,两者的对应关系如图6所示(以7号存储器为例)。

当8个数据存储器的最后一个单元数据被读出时,8个系数存储器的0号地址单元的系数也将同时被读出,然后分别作乘累加,最后作为y(0)输出。同理,当8个数据存储器的第二个数据被读出时,8个系数存储器的1号地址单元的系数也同时被读出,然后分别作乘累加,最后的结果作为y(1)输出,以此类推,得出全部y(2)~y(31)的输出。最后将y(0)~y(31)作为FFT的输入数据进行32点FFT运算。

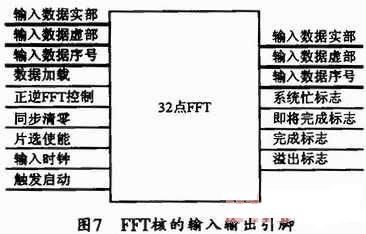

3.3 FFT的实现

设计中的FFT变换可通过调用Xilinx的IP核来实现。FFT采用流水型结构,该结构能够对连续数据流进行处理,只是结果上有若干周期的延迟。FFT核的输入输出的引脚关系如图7所示。

3.4 仿真结果

FPGA的设计软件可采用ALDEC公司的Active_HDL8.2,并可用Testbench文件对所设计模块进行仿真。Testbench文件读取时,可由Matlab产生的信号数据作为FPGA仿真的激励信号,信号形式采用28.1MHz的单频信号:

将信号数据送入图4所构建的系统后,即可在ALDEC下得到图8所示的仿真波形。

由图8可以看到,该仿真结果在第3号通道上有信号输出,这与图3中用Matlab仿真的结果一致,从而验证该模块设计的正确性。

4 结束语

本文针对多信道频率检测技术进行了研究,并在传统检测方法的基础上,结合FPGA的特点,构建了一种基于DFT多相滤波器组信道化的高效结构。该结构可解决频率截获概率与频率分辨力的矛盾,同时也为实现全概率频率捕获提供一种参考方案。经过仿真及测试验证,该方案能满足检测指标要求,从而为多信道频率检测技术提供一种设计参考。

上一篇:智能型电缆测试系统的设计与实现

下一篇:摩尔定律用于测试领域

推荐阅读最新更新时间:2024-03-30 22:23

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著)

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号