在嵌入式微控制器应用中,通常都要用到非易失性存储器。无论是掉电时维持需要保存的设置,还是存储公司的重要记录,可靠的非易失性存储器都是现代微控制器领域的一个基本单元。

非易失性存储常常采用外部串行存储器实现。多年以来,该领域用到了数十亿颗类似存储器件,它们的可靠性得到了的广泛认可。目前,存储器可以做到几百字节到1兆字节甚至更大的容量,在每一个需要保持设置的设备中,都能找到这样一个紧凑、廉价的器件。

包括EEPROM、闪存和旋转式存储器在内,所有类型的非易失性存储器都面临一个共同的问题:写周期被中断时,数据会丢失。一旦在写周期执行过程中掉电,那么即使再恢复电源,也很难修复损坏的数据。 本文提出了一种基于事务的提交-回退机制,用于保护一个外部串行EEPROM存储器件的内容。这些措施同样适用于大多数MAXQ微控制器的内置EEPROM。可以下载本应用的代码文件(ZIP,20.5kb)。

I2C EEPROM的特点

串行存储器件有多种接口,但最常用的接口是I2C接口。这种总线接口有很多优点:高度标准化的接口;控制器和存储器之间只需两条线;而且具有灵活的时序要求,可以由软件驱动。一个I2C主机可以驱动很多I2C从机,从而最大程度减少了主机的引脚数。

在所有EEPROM器件中,写周期都要比读周期长的多。因为在写周期过程中,电荷需要借助隧道效应并通过绝缘层进行转移,而这个过程很费时间。虽然增加电压可以加快这个过程,但是过高的电压会导致绝缘层的介质击穿,从而损坏器件。典型的EEPROM器件写周期持续10毫秒左右;而读周期通常需要几百个纳秒。

为了显著缩短写周期的时间,许多I2C EEPROM器件采用页面模式。该模式允许将多个字节传送到缓存中,然后将数据一次性写入存储区。I2C存储器件的典型页面尺寸为32字节。因此,可以在一个写周期内向EEPROM填入32个字节。

这一点非常重要,因为串行EEPROM器件都具有特定的耐久度:即每个页面所能承受的写周期次数上限。典型的写周期次数从10,000到1,000,000次。然而,即使存储器件能够承受1百万次写周期,软件也会很快将其损耗殆尽。软件每秒仅执行100次写周期,那么不到3个小时就会耗尽器件的写周期次数。

考虑到这些基本的EEPROM特性,设计者为一个嵌入式处理器设计可靠的非易失存储系统时,需切记以下几点:

不要在同一页面上反复执行写操作。尤其是不要将某个页面设置成写入任何其它页面时都要更新的“目录”。

如果在写周期过程中电源被中断,必须提供以下机制:(1) 检测被中断的写操作;(2) 完成被中断的操作;(3) 或者将事件回退至写操作之前的状态。

必须通过某些数据校验机制(校验和、CRC或消息摘要)来保证数据的完整性。

设计目标

虽然上面提到的EEPROM问题可通过多种非易失文件系统加以解决,但这样的文件机制对于小型嵌入式微控制器来说负担过重。很多文件系统需要更多的RAM,远远超出了小型微控制器所能提供的容量,而且对于多数应用,也不需要一个完整的文件系统。

考虑到这一点,下面列出了EEPROM数据保护机制的设计目标:

精简:保护机制用于存储校验数据的空间不应超过EEPROM的10%,它应该只需要少量的计算开销。

块大小:被保护的块大小,应该和EEPROM的写操作页面大小一样。由于EEPROM器件的页面大小通常是2的偶数次幂,因此与每个块保留1或2个字节的做法相比,相同的尺寸大小更便于软件编码。

耐久性:每个保护周期不要对同一页面进行写操作。

可靠性:每次掉电情况下,数据都应是可恢复的。

这里提到的保护机制有6个接口函数:读、写、提交、回退、检查和清理。

读函数接收一个块编号和一个指向32字节缓存的指针。如果缓存地址和块编号处于有效范围内,程序就会将指定的块数据读入缓存,并校验数据的有效性。它会返回如下状态:有效读(valid read)、无效读(invalid read)、无效缓存地址(invalid buffer address)、无效页面编号(invalid page number)或保护失败(protection failure)。

写函数接收一个块编号和一个指向填好数据的32字节缓存的指针。如果缓存地址和块编号处于有效范围内,程序就会将数据写入非易失性缓存,并标记缓存状态以准备提交。

提交和回退函数,是可以在写操作之后执行的互补型操作。提交函数将最近被写入的缓存数据复制到对应的存储区最终位置,并为下一个待写入的数据块准备好缓存结构。回退函数实际上就是一个“取消”操作。它消除最近一次写操作产生的效果,并为下一个写操作准备好缓存子系统。 检查函数读取存储器件的每个数据块,并检查存储数据的有效性。该函数还检查缓存子系统,以确保没有未执行的写操作。任何无效块或未执行的写操作都会使检查函数返回一个错误状态。

清理函数修复一个数据损坏的EEPROM。实际上,它将试图找出发生的错误,并采取相应的解决措施。

关于这些函数的更多细节,参见下面的操作详解。

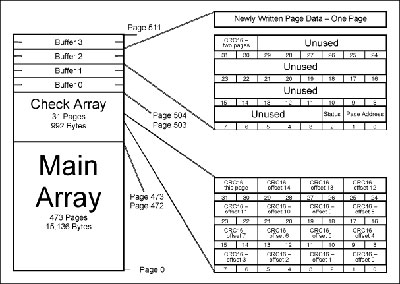

图1. EEPROM存储器的结构。存储器被划分为3个区域:主存储区,包含实际用户数据;校验存储区,包含主存储区每1页的CRC;缓存,包含存储临时写入数据的四个缓存。 |

参考上面图1给出的EEPROM结构。EEPROM包含三个主要区域:

主存储区:EEPROM的最大区域用于存储用户数据。在一个16kB器件内,包括512页、每页32字节的存储空间。在这样的器件中,开始的473个页面专门用来存储数据。

校验存储区:EEPROM的第二个部分,用于校验主存储区每个页面的数据。校验存储区的每1页都包含15个16位的CRC值。每1页的最后1个CRC用于校验本页数据。校验存储区占用31页(从473到503页)。

缓存:EEPROM的最后部分,包含由8个页面构成的4个写缓存。每个缓存包含4个域:数据域,它包含32字节数据,执行下一个提交命令时,数据将被写入主存储区;地址域,它表示缓存数据要写入的页面地址;状态域,它表示缓存的状态(包括可用(available)、占用(occupied)和终止(expired)状态);16位CRC域,用来校验整个写缓存。缓存结构见图1所示。

这种EEPROM结构可以实现主要的设计目标。首先,由于主存储区每1页数据的校验结果都存储在另一个位置,所以页面的所有位都用于存储用户数据。其次,由于主存储区的每1页都通过校验存储区的特定字来校验,因此校验存储区不会有单点错误,并且也不会在每个写周期中都去更新整个校验存储区的同一页面。最后,使用4个写缓存分散了写周期带来的损耗。

操作详解

对于一个不带保护功能的EEPROM,具体操作非常简单。一个读周期简单地将字节从所选择的地址传送给主机;一个写周期将字节从主机写入EEPROM,并等待操作完成(大多数器件需要几个毫秒的时间)。然而,在一个提供保护的EEPROM环境下,读和写操作就比较复杂了。在以下各节中,对每个操作进行了分解,以便了解函数被调用时到底是如何操作的。

读操作

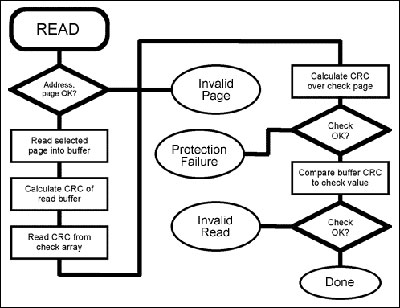

图2. 读操作的流程图 |

检查页面地址和缓存地址,以检验它们的有效性。如果地址无效,则就此结束操作,函数返回一个无效缓存地址或无效页面编号错误代码。

将所选页面读入缓存。

计算校验页面的地址,并将相应的校验页面读入暂存区。

计算校验页面的CRC。如果校验页面的数据无效,则返回一个保护失败错误代码。

计算数据缓存的CRC,并将其与暂存区中对应读取页面的CRC进行比较。如果CRC匹配,则程序返回有效读代码;如果CRC不匹配,则程序返回无效读代码。无论结果怎样,实际读取的数据都保存在返回缓存中,以供调用读操作的程序使用。

写操作

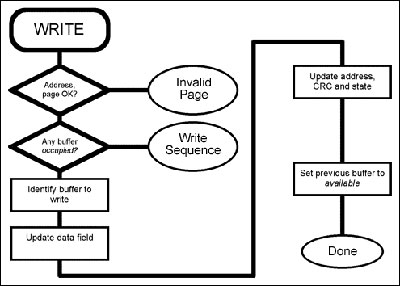

图3. 写操作的流程图 |

检查页面地址和缓存地址,以检验其有效性。如果地址无效,操作在这里结束,函数返回一个无效缓存地址或无效页面编号错误代码。

读取每个写缓存的状态域。如果任何缓存处于占用状态,则操作失败并返回写过程(write sequence)错误代码。

4个写缓存之一应处于终止状态。如果是这样,激活下一个缓存。

数据被复制到写缓存的数据域。

页面地址被写入地址域。计算CRC校验结果并将其写入CRC域。将状态改为占用。将前一个缓存置为可用状态(即更新原来的终止状态)。

需要注意,此时对新写的页面进行读操作,将返回页面原来的数值。只有等提交操作完成后,才会返回新值。

提交操作

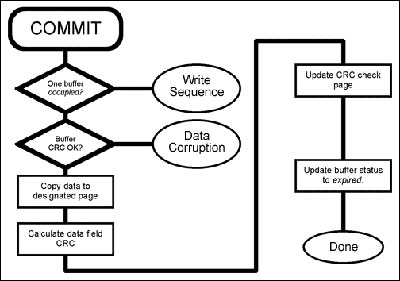

图4. 提交操作的流程 |

提交函数不需要参数。它的工作就是如实地将数据从写缓存传送到主存储区,然后将写缓存标记为终止状态。提交函数的操作流程如图4所示:

读取每个写缓存的状态域。应该只有1个缓存标记为占用状态。否则,函数在此结束,并返回一个写过程错误代码。

对被占用的缓存进行CRC校验。如果不匹配,则返回一个数据损坏错误代码。

提取页面地址,并将数据写入主存储区的指定页面。

计算缓存的数据部分的CRC。该值被保存在一个临时寄存器中。

找到对应所选主存储区页面的校验页面,并读取该校验页面的内容。

用前面计算的CRC更新校验页面,为校验页面计算新的CRC。

将校验页面数据重新写回校验存储区。

将写缓存更新为终止状态。

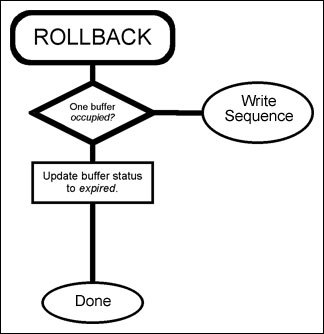

回退操作

图5. 回退操作的流程图 |

读取每个写缓存的状态域。应该只有一个缓存被标记为占用。否则,函数在此结束,并返回一个写过程错误代码。

将所选的写缓存状态域置为终止。

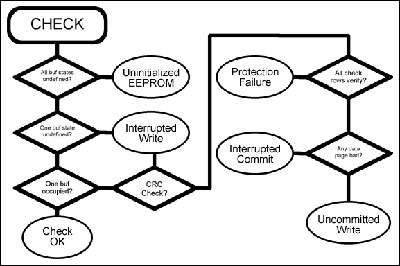

检查操作

图6. 检查操作的流程图 |

读取每个写缓存。确认只有一个缓存不是可用状态。如果只有一个缓存含有未定义的状态代码,则返回一个写操作中断(interrupted write)错误代码。如果所有缓存均包含未定义的状态代码,则返回EEPROM未初始化(uninitialized EEPROM)错误代码。

如果仅有一个缓存包含占用状态代码,计算此缓存的CRC。如果CRC不匹配,则返回一个写操作中断错误代码。

检查校验存储区的每一个页面。如果任何页面没有通过CRC校验,则返回保护失败错误代码。

最后,检查主存储区的每一页,并与存储的各页CRC进行对比。如果有1页未通过CRC校验,则返回一个提交中断(interrupted commit)错误代码。

清理操作

图7. 清理操作的流程 |

图7演示了清理操作是如何工作的:

如果检查操作返回一个EEPROM未初始化的错误代码,则初始化EEPROM。清除所有数据页面,并且初始化所有校验页面。除最后一个写缓存被初始化为终止状态外,清除其它所有写缓存并置为可用状态。

如果检查操作返回一个写操作中断错误代码,则找到那个不是可用状态的写缓存。将它的状态改为终止状态。

如果检查操作返回一个提交中断错误代码,则找到CRC不匹配的主页面。计算出它的CRC并更新相关校验页面。

如果检查操作返回保护失败错误代码,则表示紧随提交操作的更新校验页面操作被中断。读出所有与错误校验页面相关的主存储区页面,并刷新校验页面。

安全性证明

要证明系统的安全性,需要确定写操作过程中数据容易损坏的时刻。(读操作从本质上来说是安全的。读操作期间不会对EEPROM页面进行写操作,因此数据不会被损坏。) 确定了这些易损时刻后,只需要再确定一个恢复过程。如果恢复机制涵盖了所有可能的数据损失情况,而且如果我们假定在任何一个可能破坏EEPROM写周期的事件之后,都将首先执行校验/清理周期(例如上电),那么系统就是安全的。

在大多数串行EEPROM器件中,一个写操作首先将页面的每位数据都置为已知值,然后将所有需要改变的位设置为需要的值。因此在掉电时,中断的写操作极有可能破坏该页的所有字节。通常可以通过向损坏页面写入新数据,进而从这一失效事件中恢复出来。但这会失去原来的数据。

写操作过程中数据容易损坏的时刻如下所述(按发生的时间顺序排列):

对数据域进行写操作:如果此时发生电源失效事件,检查操作不会检测到错误。正在被写入的写缓存仍显示可用状态,但可用的缓存不包含有效的CRC值。

向当前写缓存写入状态信息:这个操作将状态域改为占用状态,设定CRC并为写操作填入页面地址。如果这个过程被中断,可能发生如下情况:(1) 状态无效,从而导致一个写操作中断错误;(2) 状态有效,但CRC错误,仍会导致一个写操作中断错误;(3) 状态和CRC域有效。在最后这种情形下,系统有未提交处理的写操作。可以检测到这一状态,因为此时一个缓存将处于占用状态而另一个缓存为终止状态。如果子系统的其它部分检查通过,则用户代码可通过发出提交或回退操作继续执行。无论发生何种情况,主存储区和校验存储区都是安全的。

前一个缓存状态清除为可用状态:缓存可能有损坏的状态或CRC,而下一个缓存为占用状态。这意味着清除该缓存的状态时操作被中断,这种情况下可以执行提交或回退操作。

在写操作和提交操作之间:只有一个写缓存将处于占用状态,并且通过了CRC校验。用户代码可以请求提交或回退操作。写缓存、校验存储区和主存储区都是安全的。

提交操作过程中数据容易损坏的时刻如下所述:

将数据域复制到主存储区:如果写操作被中断,主存储区的1个页面数据可能被破坏。检查函数会检测到两种状态:(1) 一个有效的占用写缓存;(2) 中断的提交操作导致主存储区页面数据损坏。写缓存和校验存储区是安全的。在这种情况下,清理操作会完成提交操作并返回一个干净的系统。注意:即使写操作已经完成,检查操作仍会因为校验存储区的CRC与计算出的CRC不匹配而报错。

更新校验存储区的CRC:如果对校验页面的写操作被中断,则整个页面的数据都可能被破坏。这意味着主存储区的15个页面都对应着无效的CRC。但是由于校验存储区的每一页都有自己的校验和,而且在写操作中断后会产生校验和错误,因此检查程序会发现这一点。在这种情况下,检查程序会返回保护失败。修复方法如下:首先重新计算所有受影响的15个页面的CRC值。然后将这些值和该页自身的有效CRC值一起写入校验页面。

更新写缓存的状态信息:如果当状态变量从占用状态变为终止状态时,写周期被中断,那么整个写缓存页面的数据都可能被损坏。但是,校验存储区和主存储区都是安全的。检查操作会找到数据损坏的页面,并返回写操作中断错误代码。当运行清理程序时,它将复位写缓存子系统,并完成提交操作。

最后,在回退操作中数据容易损坏的时刻为:

更新写缓存的状态:与提交周期的最终状态类似,该操作只是简单地将写缓存的占用状态复位至终止状态。如果它被中断,则检查程序会返回写操作中断,并且清理程序会重新初始化所有的写缓存区域。校验存储区和主存储区仍是安全的。

可以看出,无论电源何时掉电或处理器何时被复位,存储子系统都可保持数据的完整性。发生电源失效事件后,存储子系统会返回到可进行读或写的状态。如果一个提交操作被中断,子系统会返回到可执行提交或回退操作的状态。

设计起步

MAXQ微控制器的EEPROM存储系统功能完备。系统设计者可以根据需要来增强该系统的功能。但需要注意以下几点:

C封装程序:在多数C语言标准中,与汇编语言子程序双向传送数据时都有一套标准的方法。例如在IAR开发环境下,参数在低编号的累加器中传入和传出。由于参数已经传入A[0]和A[1],为这些程序建立一个C封装器,就像写函数原型一样容易。在其它C环境下,参数传递是通过数据栈进行的,需要一个简单的封装子程序。

并发处理:首先要保证写周期的完整性,并且提供一套能够保证完整性的机制,对于整个平台的成败至关重要。但很多应用都需要这样一种机制,即可以让一系列写周期排队并一次执行完毕,从而保证全都执行或全都不执行。但本文讨论的机制不能工作在这种方式下。如果一个系统存有跨越多个页面的信息记录,则可以中断一个写操作,这使得恢复之后的记录涵盖了包含部分新数据的页面和包含部分旧数据的页面。有一种方法可避免该问题,即在执行提交操作之前允许多重写操作。这种方法并不像听上去那么简单,因为一个部分提交的事务,可能同时包括新纪录片断、旧记录片断和损坏的页面。

平均读写机制:平均读写作为闪存文件系统的一个特点,是指虚拟化页面地址,使得被频繁写入的页面会出现在存储器的任何物理位置。但是很难找到实现这一目标的最佳方法。这是因为,最直接的解决方法(活动存储块的目录处于固定的位置,并且每次写操作后都要对它进行更新)会导致存储目录的页面迅速损耗。所以,就像处理数据页面那样,还必须虚拟化和离散化目录本身。

其它页面尺寸:这里给出的系统假定采用一个16kB、每页32字节的存储器件。如果所选择的器件具有更大的页面尺寸(64字节或128字节),这些函数仍可工作,只是会伴随一些额外的写入损耗。(更新128字节页面中的32字节区段时,会对整个128字节页面执行写操作)。但这些函数无法对具有更小页面尺寸的器件进行操作。可以构建一个能够在线确定EEPROM器件特性的系统,并可根据实际特性配置系统的参数。

增强的安全性:本系统对以下类型的错误提供保护:由于电源失效或不可预期的系统复位而造成的EEPROM操作中断。但EEPROM器件偶尔也会因为其它原因出错。例如,由于电路噪声或致电离辐射导致的软件错误。或者由于一个或多个存储单元损耗而导致硬件错误。

一种解决方法是计算并维护校正子(syndrome),而不是采用简单的CRC校验字。校正子和校验字类似,但是包含了足够的信息以修复简单的位错误。最简单的校正子系统可以用log2n + 1个校验位来检验n个数据位。因此,对于一个32字节(256位)的页面来说,一个仅包含9位的校正子就可以修正任何1位错误。对数据完整性的要求更加严格时,可以采用更加复杂的系统来解决类似问题。

结语

外部串行EEPROM为微控制器环境下存储非易失数据提供了一种可靠的方法。利用本文提到的技术,即使面临写操作中断的情况,串行EEPROM依然能够可靠地工作。在任何对数据完整性要求较高的应用中,设计者都可以考虑这些技术。

上一篇:带RTC的I2C总线铁电存储器FM31256

下一篇:内容可寻址存储器MCM69C232及其应用

推荐阅读最新更新时间:2024-05-13 18:16

- 热门资源推荐

- 热门放大器推荐

-

整车控制策略开发需求分析及新能源汽车动力总成测试系统

整车控制策略开发需求分析及新能源汽车动力总成测试系统 -

浅谈电子技术在汽车自动控制中的应用

浅谈电子技术在汽车自动控制中的应用 -

ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟)

ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟) -

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉)

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉) -

Electric Motor Control: DC, AC, and BLDC Motors

Electric Motor Control: DC, AC, and BLDC Motors -

东芝1200V SIC SBD “TRSxxx120Hx系列” 助力工业电源设备高效

东芝1200V SIC SBD “TRSxxx120Hx系列” 助力工业电源设备高效 -

MATLAB Simulink系统仿真超级学习手册

MATLAB Simulink系统仿真超级学习手册 -

ADS射频电路设计基础与典型应用

ADS射频电路设计基础与典型应用

整车控制策略开发需求分析及新能源汽车动力总成测试系统

整车控制策略开发需求分析及新能源汽车动力总成测试系统 ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟)

ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟) Electric Motor Control: DC, AC, and BLDC Motors

Electric Motor Control: DC, AC, and BLDC Motors

京公网安备 11010802033920号

京公网安备 11010802033920号