超声波电机(USM)具有能够直接输出低转速大力矩,瞬态响应快(可达ms量级)、定位精度高(可达nm量级),无电磁干扰等诸多优点。USM的运行需要有两路具有一定幅值,相位上正交(或可调),频率在20 kHz以上的高频交流电源。驱动信号源的幅值、频率及相位直接影响USM的性能。为便于USM的性能测试及研究,需要提供一种在幅值、频率、相位上均可调的测试电源。以往的超声波驱动器多采用分立器件构成如文献,其电路结构复杂。文献虽然改用FPGA或CPLD生成,但所生成的信号频率变化是不连续的。文献是用单片机和专用的DDS芯片,存在抗干扰性差,可靠性低的弊端。

本文介绍了基于DLL数字频率直接合成技术(DDS)用ALTERA公司的FPGA器件和VHDL语言编程,按相位累加的方法产生两相四路频率相位可调的高频PWM信号,经过驱动电路、光耦隔离电路作为外部功率控制电路H桥的四个闸门驱动信号,H桥主回路接入的是对市电经调压、隔离、整流及滤波后的直流电。由闸门驱动信号对该直流电进行通断控制,形成可调幅值、频率、相位差的两相高频PWM波的交流信号,再经外加电感平滑,将PWM波信号变成类正弦波信号,实现对USM的性能测试。

1 功率控制电路

如图1所示,加于USM的A、B两相交流信号是由FPGA产生的四路脉冲信号控制MOS管开关对整流滤波后直流电进行通断控制,在图1所示H桥逆变器的作用下,将直流电逆变为与逆变器开关频率相同的矩形波交流电,经串联电感平滑,就得到了USM所需的两相高频类正弦波信号。该信号可由主回路的调压器调节幅值,A、B两相的相位差取决于H桥两侧闸门驱动信号的相位差,即闸门S1与S2(或S3与S4)驱动信号的相位差。同侧桥臂不能同时导通,以避免大电流通过MOS开关管而损坏开关管,理论上同侧的两个控制信号应该相位互补,实现推挽输出,考虑到开关器件的延时特性,该信号开启闸门时要有一定的延时,即死区时间。鉴于以上分析及USM性能测试的需求,闸门控制信号应具有频率、相位、死区时间均可调的占空比大于50%的PWM高频波。

2 PWM调频调相高频信号的产生

参考文献的DDS设计,将一个周期的矩形波幅值进行2n等分后按顺序存于一个表格中,用高频时钟fclk依次按表中地址顺序读取其数据(幅值)。利用相位累加器可以每隔M个地址,读一个幅值信息。矩形波频率正比于输入时钟频率和相位增量M之积,即为基频时钟fclk/2n的M倍。通过调节步距M(频率控制字)可调节信号的频率。调节首次所读ROM表的地址,可调节矩形波的相位,称该调节参数为相位控制字。若ROM查找表中0,1各占一半则可得到频率、相位连续可调的方波信号;改变表中1的比例,就会得到不同脉宽的矩形波。若能从外部调节1的比例,就生成了一路频率、相位、占空比可调的PWM信号。由于表中只有两种数O和1,且均连续出现,因而可用比较器替换ROM表,将原来的地址发生计数器的计数值划分为2部分,一部分对输出信号清零,另一部分对其置1。2种方案相比,后者大大节约了FPGA资源。RTL级原理图如图2所示。

程序设计中的FWORD[16..O]为原理描述中的频率控制字M,连接于32位计数器F32[32..6],其输出信号FOUT的频率按如下公式计算FFOUT=fclk/222·FWORD,频率分辨率为Fmin=25fclk/222,最大输出频率为Fmax=Fmin FWORDmax。当系统频率fclk=50MHz时,Fmin=0.745 Hz,Fmax=97.648 kHz,即输出频率可在O.7~97.6 Hz之间调节。相位控制字为9位,输出信号FOUT的相位可按如下公式计算:POUT=360°/2°×PWORD,最小分辨率为360°/2°=0.7°。DIEIN[8..O]为占空比(死区)调节控制字输入,占空比按计算公式:(29-DIEIN)/210x1 00%,最大占空比为50%,最小接近于O,占空比的调节以使图一H桥同侧的两个MOS管刚好不同时导通为度(故占空比不能大于50%),占空比太小会使整个系统转换效率降低。

以单相调频调相PWM信号设计作为底层元件,利用VHDL的结构化描述方式(例化语句),按相位要求将4个单相调频调相信号DDS元件设置成不同相位来实现。相位字PWORD为9位,U0:PWORD=O,初始相位=0;U2:PWORD=“100000000”,初始相位为180°;U1元件的初始相位PWOR-D,U2元件的初始相位为PWORD+“00000000”,这就实现了UO和U1相位差为PWORD,U0和U2,U1和U2相位差各为180°,从而实现四路调频调相PWM信号设计。

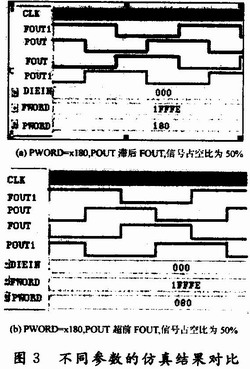

通过调节FWORD、PWORD及DIEIN来分别调节四路输出信号的频率、相位差、四路输出信号的占空比。仿真结果如图3所示。由仿真图可知超前90°和滞后90°得到的四路相序正好相反,若用其驱动图1的4个开关,得到两相互差90°的信号,一个为A相超前于B相,另逐个为A相滞后于B向。用其驱动USM,在不改变电机连线的情况下,通过调节相位差PWORD,方便的实现电机的旋转方向控制。

3 实验测试

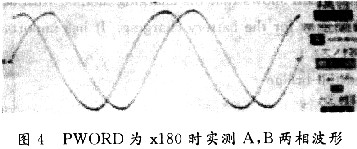

将上述四路控制信号下载于FPGA中,再经过资料介绍的驱动隔离模块后施加于图1的功率控制电路,通过示波器测得USM的A、B两相波形如图4所示。将上述电路获得的信号应用于USM45超声波电机的驱动中,该电机所要求的驱动信号频率为45.8 kHz,相位差为90°,峰峰值可达300 V。将其频率控制字设定为FWORD=x0F000,相位控制字为PWORD=x180(或x080),死区时间DIEIN=x33~xFF之间调整,成功地驱动了USM 45电机。运行10 min左右,电机转速下降,通过将FWORD调小至xED00,即信号频率为45.2 kHz时,电机速度又上升到开始时的值(65转/mi n)。超声波电机一般工作在定子导纳2频率特性的谐振和反谐振点之间。随电机运行温度的升高,导致谐频率和反谐振频率约有1.4 kHz的变化。由于USM45电机功率小,额定功率只有2 W,且是空载测试,因而温升较小,谐振频率的变化也较小(只有大约0.6 kHz的变化)。

4 结语

由FPGA按照相位累加振荡器的方法产生的四路调频、调相PWM信号,具有较高频率分辨率,在保持相位连续的前提下,能实现快速频率切换。该信号不但在外部的逆变电路作用下,成功地对USM45电机进行了驱动和测试,还可通过外加专用的L298N型驱动芯片方便地应用于步进电机和直流电机的驱动以及步进电机的调频调速和直流电机的PWM调速。

上一篇:一种混合信号通用电池充电器设计

下一篇:如何设计多重负载系统电源

推荐阅读最新更新时间:2023-10-18 15:01

Vishay线上图书馆

- 选型-汽车级表面贴装和通孔超快整流器

- 你知道吗?DC-LINK电容在高湿条件下具有高度稳定性

- microBUCK和microBRICK直流/直流稳压器解决方案

- SOP-4小型封装光伏MOSFET驱动器VOMDA1271

- 使用薄膜、大功率、背接触式电阻的优势

- SQJQ140E车规级N沟道40V MOSFET

- ADI有奖下载活动之21:ADI民用雷达解决方案

- 【EE征集令】LaunchPad学习全体验

- 等你报名做客黑科技直播间:基于 TI DLP®技术的工业创新应用介绍

- 【欢乐新年精彩共享】优秀主题/回复活动第19期如期到来啦~~

- 下载有礼喽!2017年泰克亚太专家大讲堂第三期: 超宽带复杂电磁信号产生与实时分析技术

- 悦览 PI 节能技术资料,参与测试、评论赢双重好礼!

- 喜迎新年,EE喊你抢新年福袋啦!

- 用富士通Cortex-M3 Easy Kit开发板,DIY出你的精彩!l

- 答题有好礼 | 是德科技《优化物联网设备电池续航时间的4个技巧》

- 【专题】TI MSP430FR59xx——将低功耗设计进行到底!

FPGA快速系统原型设计权威指南_(美国)

FPGA快速系统原型设计权威指南_(美国) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号