在电力系统中,由于电网的容量是一定的,这就意味着当接入负载时,其功率即为P=U*Icosφ,由于cosφ<1,则说明电网的容量得不到充分利用。在P、U不变的情况下,提高功率因数cosφ,能降低电网输电线路的功率损耗,提高电网的供电质量,降低生产成本。因此,提高功率因数是节能的重中之重。

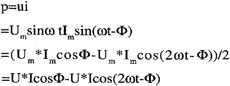

由电工学理论,负载的瞬时功率由以下推论:

由公式推导,瞬时功率由两个二次项组成,一项是与功率因数cosφ成正比的直流分量,另一项是与电网2ω频率相关的交流分量。

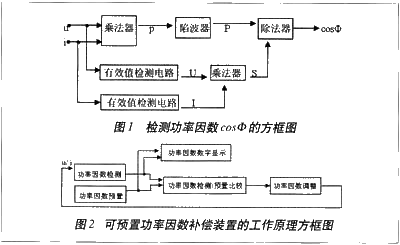

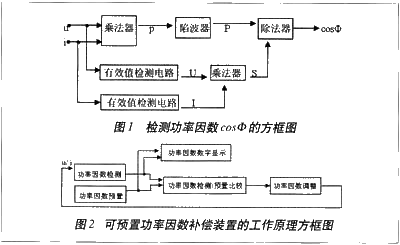

用乘法器将u、i相乘,得负载的瞬时功率。如果设计一个陷波器,去除负载瞬时功率的2ω频率的交流分量,那么,电路就只剩下与功率因数cosφ成正比的直流分量U*Icosφ。

另外,可用有效值检测电路检测u、i,从而得到电压u、电流i的有效值U、I,用乘法器将U、I相乘,得负载的视在功率。由公式cosφ=P/U*I可知,只要在电路多加一个除法器,就可以正确检测出负载的功率因数cosφ,图1为检测功率因数cosφ的方框图。

可预置功率因数补偿装置的工作原理

图2为可预置功率因数补偿装置的工作原理方框图。当负载接通电源后,功率因数检测电路自动检测电路的功率因数,待检测的功率因数值与功率因数预置电路的期望值进入可预置功率因数补偿装置中的比较器进行大小比较;当电路的功率因数大于期望值时,调整电路不工作,而功率因数小于期望值时,功率因数调整电路工作,调整电路通过并联电容补偿或调整负载电源的频率,从而改变负载的功率因数,当功率因数提高到期望值时,比较器输出为零,功率因数调整电路又停止工作。总之,可预置功率因数补偿装置的工作,使负载的功率因数在期望值上下的一定范围内波动,并保持稳定,这就是该电路的工作原理。

电路的基本组成

功率因数检测

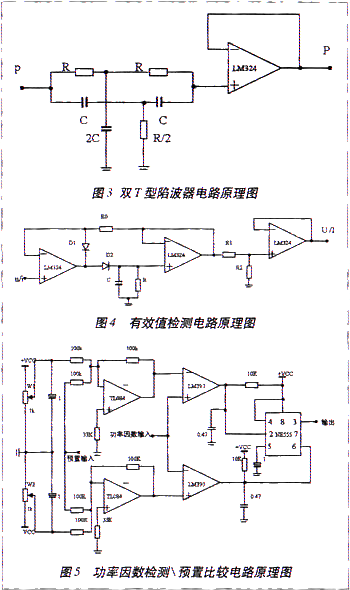

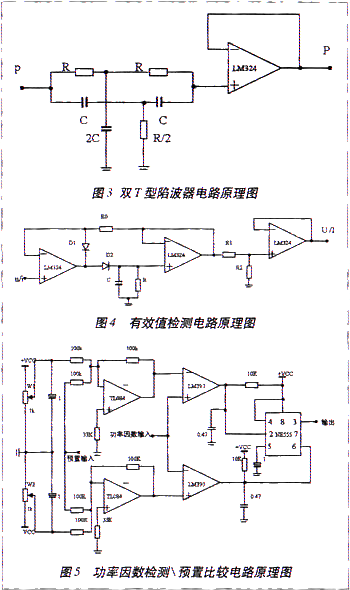

由乘法器、双T型陷波器、有效值检测电路以及除法器组成功率因数检测电路。乘法器为由MC1494和集成运算放大器LM324组成的电流/电压转换器。使用双T型陷波器(见图3)的目的在于去除电路中2f电网频率信号,那么,电路就只剩下与功率因数cosφ成正比的直流分量U*Icosφ了。

在设计功率因数检测电路时,以下几点应该注意:

1、双T型陷波器的频率选择应为电网频率的2倍,由fn=1/2πRC正确选择参数;

2、有效值检测电路图4中,RC应满足RC>>1/2πf,而R1、R2也应满足1.41=(R1+R2)/R2的条件。图中的第一、二集成运算放大器LM324组成峰值检测电路,而第三集成运算放大器则构成比例放大器;

3、除法与乘法互为逆运算,因此,除法器仍可采用上述由MC1494和集成运算放大器LM324组成的电流/电压转换器。

功率因数预置

功率因数预置由电源经桥式整流得2f脉动频率,由集成电路4518分频4Hz方波,作为功率因数预置信号。由40106、4001、4023、4516、AD558、LM324组成功率因数预置电路,将数字信号转换成0~1V电压。

功率因数数字显示

功率因数数字显示部分由0~2V数字式表头改造而成,由开关控制切换功率因数预置、功率因数检测信号的显示。

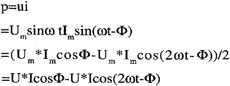

功率因数检测、预置比较电路 预置输入为反相输入信号,如图6所示,调节W1、W2,使功率因数预置值有上下限,通过LM393比较器,当功率因数输入电压低于下极限时,NE55的3脚输出高电平,电路中的功率因数调整电路工作,调整电路通过并联电容补偿或调整负载电源的频率,从而改变负载的功率因数,当功率因数提高到期望值上限时,NE55的3脚输出为零,功率因数调整电路又停止工作。

功率因数调整电路

对于电感性负载,功率因数的调整可通过并联电容补偿或调整负载电源的频率,以改变负载的功率因数来实现,功率因数调整电路所涉及的内容较多,本文不作逐一论述。

结语

本文提出了可预置功率因数补偿装置的设计方法,电路原理及构成清晰。文章分析了电路的关键技术及注意事项。

关键字:频率 负载 陷波 瞬时

编辑:金海 引用地址:可预置功率因数补偿装置的设计

推荐阅读最新更新时间:2023-10-18 14:39

基于状态观测器实现转速及负载转矩估计的直流调速系统

摘 要:

在双闭环直流调速系统中,需要传感器检测电流和转速的反馈值。介绍了运用状态观测器理论设计出的一种能够估计转速和负载转矩参数的二维观测器,并介绍了将估值运用到直流调速系统的设计中从而实现负载转矩的扰动补偿,使仿真结果达到了设计要求。

关键词: 直流调速系统 转速 负载转矩 观测器

目前直流调速系统广泛采用转速、电流双闭环调节回路,转速检测元件有测速发电机和光电码盘。直流测速发电机存在造价高、碳刷需经常维护、不易在现有系统上加装等问题;光电码盘也有造价高、需与电机轴弹性连接等问题。在构成转速负反馈时,通过状态观测器实现对转速的估值是一种可行的途径。在直流调速系统中

[传感技术]

卓联半导体推时钟产品率先满足最新同步以太网行业标准要求

现在开始提供满足所有同步以太网时钟要求的高性能1 GbE和10 GbE时钟卡和线路卡同步器件样品

2007年7月24日,中国北京 —— 卓联半导体公司(Zarlink Semiconductor Inc. (NYSE/TSX:ZL))日前宣布推出集成模拟/数字PLL(锁相环路)的系列器件样品。新器件满足所有同步以太网时钟要求,包括ITU-T(国际电信联盟)的最新建议标准。

2007年6月通过的ITU-T G.8262 标准 (原G.paclock)规定了同步以太网网络设备中使用的时钟器件的最低性能要求。该标准规定的PLL性能参数包括漂移、抖动、瞬态相位、时钟带宽、频率精度和保持等。

“卓联半导体公司是提供满足所有

[新品]

基于tc1的频率计设计

//***************FileName:Capature.C***************//

//***************ICCAVR V6.30编译*****************//

#include io8535v.h

#include macros.h

#define uchar unsigned char

#define uint unsigned int

#define CON 1000 //频率常数定义

uchar Flag=0; //捕获次数定义

//数码管字型表,对应0,1,2,3,4,5,6,7,8,9,A,b,C,d,E,

[单片机]

详解基于555定时器的电容测试仪设计

1 引言 随着电子工业的发展,电子元器件急剧增加,电子元器件的适用范围也逐渐广泛起来,在应用中我们常常要测定电容的大小[1]。因此,一种简单、实用的电容测试工具在实际中具有一定的实用价值。一般元件参数的数字化测量是把被测参数转换成频率后再进行测量[2],本设计采用555为核心的振荡电路,将被测电容值转化为频率,并利用AT89S51处理器测量出频率,再通过该频率值计算出电容参数值。 2 系统的原理框图 系统主要采用了555定时器构成的RC振荡电路和单片机技术。设计思路:被测电容C通过RC振荡转换成频率信号f,送入单片机测频,对该频率进行运算处理求出被测电容的值,并送显示器显示。系统框图如图1所示,其主要由测量

[测试测量]

扩展RF/微波测量的频率范围

前言

虚拟仪器和合成仪器,是近年来业内人士经常谈论的热门话题。与传统的机柜式产品相比,采用模块化方案,其更新和重构系统的成本更低廉。 VXI 和 PXI 是常用的两种标准,相比之下,PXI的体积更小、重量更轻、总线更快,因而使用也更广泛。 然而,习惯于常规仪器的行家里手会质疑,RF和微波仪器产品能否在PXI中实现。数字信号十分合适,低功率设备也不成问题。甚至数字示波器和任意波形发生器一类仪表也可以做成PXI格式,但RF和微波测试装置却不行。

图1 典型的单级下变频器方框图

图2 典型的单级上变频器方框图

对小型、经济实用和可重构的RF与微波测量系统和发生器系统的需求一直保持着强劲的势头

[测试测量]

安捷伦推出带有灵活频率选件的阻抗分析仪

2014年 5 月 22 日,北京――安捷伦科技(NYSE:A)日前宣布推出 Agilent E4990A 和 E4991B 阻抗分析仪。这两款分析仪专门面向研发、质量保证和检验工程师,用以对无源电子元器件、半导体设备和材料进行表征和评测。分析仪具有灵活的频率选件,并且都以适中的价格提供业内最出色的精度和性能。

随着低功耗紧凑型设备市场需求的激增,高效的电源转换器已经变得更加重要,而且需要知道产品设计阶段关键的低损耗元器件的真实特征。安捷伦的最新阻抗分析仪是业界唯一能在 20 Hz ~ 3 GHz 频率范围内对毫欧姆到兆欧姆的所有元器件执行高精度测量的仪器,因而能够轻松评估高质量元器件的真实特征。E4990A 可在宽

[测试测量]

用三位转速计测量超低频率

图中所示的电路是一个三位转速计,用来测量重复时间间隔为0.235至15秒内的低频信号。转速计的转速为每分钟4至255转,它应用在那些医疗设备,这些医疗设备中,用来测量心跳率、呼吸率、电解磨削、脑电图、低转速电机转速或机械装置转速之类的低频信号。

PIC16F872微处理控制处理转速计的数据。PIC感应输入频率(fin)的周期,计算出每秒产生的相应的脉冲数,并相应的更新LED显示器。输入信号需被预处理成0到5V的直流电压,脉冲高电平的宽度至少为4μs。

MCU所用等式为RPM = 60/T。T指感应输入的周期,常数60代表一分钟(60秒内)脉冲的读数或每分钟的旋转数。该电路的时间基准是出一个32kHz的晶振(爱

[医疗电子]

STM32的ADC采样频率及相应时间的确定

STM32 ADC 介绍 STM32 ADC 是一个12 位精度、 一种逐次逼近型模拟数字转换器。它有多达18个通道,可测量16个外部和2个内部信号源。各通道的A/D转换可以单次、连续、扫描或间断模式执行。 ADC的结果可以左对齐或右对齐方式存储在16位数据寄存器中。 ADC的输入时钟不得超过14MHz,它是由PCLK2经分频产生。转换时最快为1us,当ADC的输入时钟超过14MHz 时其会损失一些精度。当然如果可以达到我们的精度,输入时钟高点也没事。 在网上看到一回答ADC不超过14MHz 的答案:资料上的都是推荐,事实上很多芯片的设计都是有超额余量的,很多人都会超额的利用这些资源,并且很好的工作。

[单片机]

西电-印刷电路板(PCB)设计指南_1-99

西电-印刷电路板(PCB)设计指南_1-99 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号