1 引言

雷达恒虚警(CFAR-Constant False Alarm Rate)在雷达系统中有着重要的作用和地位。恒虚警处理可以避免杂波变化影响的检测阈值,提高雷达在各种干扰情况下的检测能力。

美国模拟器件公司(ADD的ADSP-TS201处理器具有高速运算能力、可时分复用、并行处理、数据吞吐率高等特点。该处理器片内集成大容量存储器,性价比高,并兼有ASIC和FPGA的信号处理性能、指令集处理器的高度可编程性与灵活性,适用于高性能、大存储量的信号处理和图像应用。本文主要讨论基于ADSP-TS201的恒虚警实现方法。

2 ADSP-TS201简介

ADSP-TS201采用超级哈佛结构,静态超标量操作适合多处理器模式运算,可直接构成分布式并行系统和共享存储式并行系统。ADSP-TS201的主要性能指标如下:

最高工作主频600 MHz(1.67 ns指令周期);

支持IEEE浮点格式32 bit数据和40 bit扩展精度浮点格式。同时支持8/16/32/64 bit的定点数据格式;

允许128 bit的数据、指令和I/O端口访问,内部存储器带宽33.6 GB/s;

32 bit的地址总线提供4 G的统一寻址空间;

14通道的DMA控制器支持硬件和软件中断,支持优先级中断和嵌套中断;

4个全双工LINK端口支持最达500 MB/s的传输速度;

JTAG仿真接口允许多片DSP仿真。

3 ADSP-TS201与TS101性能比较

ADSP-TS201与ADSP-TS101相比,主要在运行速度、存储器结构和链路口结构上有差别,如表1所列。通过比较可以看出ADSP-TS201的性能比较好,故选用ADSP-TS201实现雷达恒虚警检测。

4恒虚警检测原理

4.1选大单元平均CFAR(GO-CFAR)

云雨杂波和低分辨率雷达的海浪和地物杂波的包络服从瑞利分布,其概率密度函数为:

门限VT一旦确定,背景噪声(干扰)和杂波干扰会使虚警概率增加,因此恒虚警处理十分必要。杂波干扰环境通常采用单元平均恒虚警。实际工程中为了消除杂波边缘内侧虚警显著增大,采用选大单元平均恒虚警。

选大单元平均CFAR通过两侧2L个距离单元数据平均值估算杂波功率,用杂波功率对所检测的距离单元数据进行归一化并乘以门限,作为检测门限。检测门限与检测单元比较,超过门限判断为有目标,低于门限判断为无目标。

4.2杂波图

杂波图可认为是CFAR中的一种,采用参考样本估计杂波电平。将雷达周围的二维平面划分成许多方位距离单元,再将每个方位距离单元的接收信号存入存储器,每个存储单元对应一个方位距离单元。一个杂波图单元可以由一个或几个分辨单元组成。按照不同的距离和不同的波位计算并存储杂波图,利用杂波图数据设置门限并与雷达回波相比较,检测低速目标。

杂波图分为动态杂波图和静态杂波图。静态杂波图是在雷达建站时或者定期对雷达周围的杂波环境进行测量,静态杂波图对雷达回波信号按照特定公式进行归一化处理,一般用于接收机控制增益。而动态杂波图随着天线扫描,每个方位单元存储的信号递归更新,天线多圈扫描后,幅度杂波图存储相应方位距离单元的杂波均值。检测门限为相应方位距离单元杂波均值与门限之积。如果被检测信号大于门限,则判为有目标,否则判为无目标。

5 恒虚警在ADSP-TS201上的实现

5.1运算量、存储量分析及时间估计

首先分析选大单元平均CFAR的运算量和时间。以某一重复频率为例(重复频率为184μs,无模糊距离为27.6 km),整个距离的数据量约为3.6

K个32 bit的字。处理一帧数据的时间约185.5

ms。经多普勒补偿后数据量翻倍,实际处理一帧数据(定浮点转换、取模、CFAR)的时间约为314.5

ms。因此仅用一片ADSP-TS201是无法实现的。

然后分析杂波图的存储量。将雷达周围的二维平面划分为6个扫描区,每个扫描区有91个波位,每个波位存10层(前后各5层)杂波数据。若一个杂波图单元由2个分辨单元组成,则一个杂波图单元存储16

bit,一个扫描区最大存储量约为30 M,ADSP-TS201内存不能存储杂波图数据。

5.2硬件实现

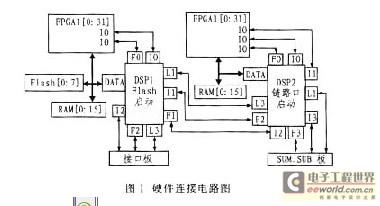

采用两片ADSP-TS201实现硬件设计,每个处理器都连接一个32 MB×16 bit的SDRAM。硬件连接图如图1所示。

图中,L表示链路口;F表示FLAG引脚;I表示外部中断引脚;IO表示输入输出引脚;DATA表示数据口。

DSP1与Flash相连接用于启动,DSP2与FPGA连接用于接收来自FPGA脉压后的复数数据。两个处理器之间的点对点通信是通过链路口互联实现的,每个链路口以双向全双工方式工作。两个DSP各自连接SDRAM用于存储杂波图数据。DSP1采用EPROM加载方式,DSP2通过链路口加载。

5.3软件实现

软件设计主要实现:定浮点转换、取模、杂波图检测以及CFAR处理。每部分程序都是一个子程序,便于调用、调试。考虑到实时性要求,程序采用汇编语言,片内利用ADSP-TS201的X,Y双运算块并行运算。由于选大单元平均CFAR处理要对两侧L个临近单元求和,取模可直接求和,把取模和CFAR用一个子程序完成,减少了读取数据的时间。图2、图3分别为DSP1、DSP2的软件处理流图。

DSP1主要完成加载,频率通道号为奇数行数据的杂波图检测和CFAR,并将一帧数据检测到的目标信息发送给接口板。DSP1的链路口3与接口板相连,将合并后的结果送给接口板用于模糊。

DSP2接收来自FPGA脉压后的数据,将频率通道号为奇数的数据发送至DSP1,偶数行数据DSP2自行处理。一帧数据处理结束,DSP2将检测到的目标信息送至DSP1,经DSP1合并后再送出。

6系统仿真结果

软硬件设计完成后,进行功能测试。图4是背景杂波服从瑞利分布时,采用ADSP-TS201汇编语言对整个雷达目标恒虚警检测过程仿真得到的结果。采样点数为1

024点。需要指出的是,恒虚警检测算法会带来不同程度的恒虚警损失,与邻近单元的个数L和积累周期数有关,因此在实现时要尽量减小恒虚警损失。

7 结束语

介绍了在ADSP-TS201上实现杂波背景中雷达目标的恒虚警检测方法,具体讨论了实现过程中软硬件设计,并给出了系统仿真结果。

上一篇:键盘显示专用器件HD7279A的接口设计

下一篇:基于AT77C101B的指纹识别系统

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 LM110H/883

LM110H/883

京公网安备 11010802033920号

京公网安备 11010802033920号