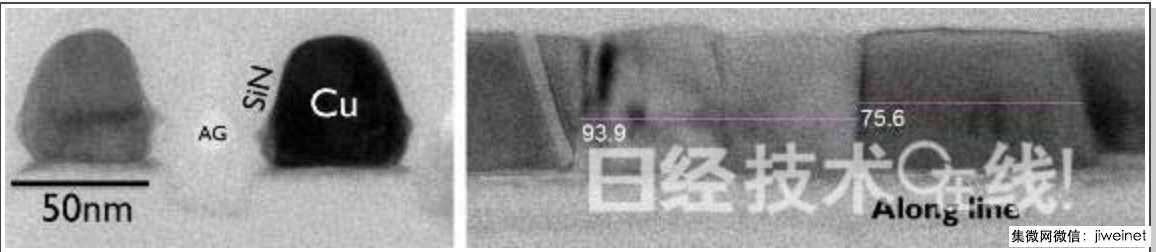

图1:使用直接蚀刻制作布线图案的Cu布线的TEM像。Cu布线使用Si氮化膜密封

图2:在钯/钨(Pd/W)底面的28nm直径孔穴(宽高比4.5)中,利用化学镀沉积的Co。左起依次是沉积途中、理想沉积、过度沉积状态

IMEC与东电电子合作开发的,是能够替代广泛普及的铜(Cu)布线的镶嵌工艺,通过对Cu布线进行直接蚀刻,制作布线图案的方法。展现出了解决布线电阻和可靠性课题的可能性。

直接蚀刻Cu布线制作图案

最尖端的器件使用镶嵌而成的Cu布线,但沟槽宽度会限制粒度,因此,在晶界增加引发的表面散射的作用下,布线电阻会大幅升高。而且,晶界增加后,电迁移将会加剧,从而出现布线内Cu的体积减少、可靠性降低的课题。

IMEC与东电电子很早就为替代传统的Cu镶嵌工艺,围绕利用直接蚀刻制作Cu布线图案的方法展开了基础研究(图1)。此次的研究结果表明,该方法在两点上具有优势。第一,通过使用直接蚀刻,可以扩大粒度,降低布线电阻。第二,通过在蚀刻后防止暴露在空气中,利用硅氮化膜进行密封,可以遏制Cu的氧化,使Cu/Si氮化膜成为电界面,从而可以遏制电迁移。

利用化学镀填入Co

另一方面,IMEC与科林研发公司合作开发的,是利用化学镀(electroless deposition:ELD)的方法,选择性地在通孔及接触孔中填入钴(Co)的技术(图2)。接触孔在钨(W)底面的上方、通孔在Cu底面的上方选择性沉积Co。Co可以遏制孔穴的发生,因此与使用Cu相比,可以降低布线电阻。ELD法与通常的CVD法相比,可以降低成本,而且成本有望低于填入Cu的方法。Co即使与低介电常数(low-k)的材料直接接触,也不会降低可靠性。

以上两项发表虽然都还处于基础研究阶段,但在今后,该公司还将锁定7nm工艺以后的技术,开展具体的应用研究。这次的结果得到了IMEC的核心CMOS项目的合作伙伴(美国GLOBALFOUNDRIES公司、美国英特尔公司、美国美光科技公司、韩国三星电子公司、台湾TSMC,韩国SK海力士公司、松下、富士通半导体、索尼)的协助,技术将优先提供给这些企业。

上一篇:FCI 推出 GCS™ 低电阻镀层技术

下一篇:上新闻联播的高功率半导体技术:给激光器安上中国“心”

推荐阅读最新更新时间:2023-10-12 23:35

- 创实技术electronica 2024首秀:加速国内分销商海外拓展之路

- 欧洲三大芯片巨头,重新审视供应链

- 一场IC设计业盛宴!10场论坛 200位演讲嘉宾,300+展商亮相2万平米专业展会!

- 富昌电子于杭州举办技术日活动,聚焦新能源“芯”机遇

- 消息称铠侠最快明天获上市批准,市值有望达 7500 亿日元

- 美国政府敲定对格芯 15 亿美元《CHIPS》法案补贴,支持后者提升在美产能

- SK 海力士宣布量产全球最高的 321 层 1Tb TLC 4D NAND 闪存,计划 2025 上半年对外出货

- 三星电子 NRD-K 半导体研发综合体进机,将导入 ASML High NA EUV 光刻设备

- 芯片大混战将启:高通、联发科涉足笔记本,AMD 被曝入局手机

- 微灵医疗李骁健:脑机接口技术正在开启意识与AI融合的新纪元

- USB Type-C® 和 USB Power Delivery:专为扩展功率范围和电池供电型系统而设计

- 景昱医疗耿东:脑机接口DBS治疗技术已实现国产替代

- 首都医科大学王长明:针对癫痫的数字疗法已进入使用阶段

- 非常见问题解答第223期:如何在没有软启动方程的情况下测量和确定软启动时序?

- 兆易创新GD25/55全系列车规级SPI NOR Flash荣获ISO 26262 ASIL D功能安全认证证书

- 新型IsoVu™ 隔离电流探头:为电流测量带来全新维度

- 英飞凌推出简化电机控制开发的ModusToolbox™电机套件

- 意法半导体IO-Link执行器电路板为工业监控和设备厂商带来一站式参考设计

- Melexis采用无磁芯技术缩小电流感测装置尺寸

- Avnet&On semi 带你看未来,3个你必须知道的行业趋势!

- 【EE团】TI M4开发板超低价尝鲜体验,分享心得赢百元返现!

- 论坛有5只冰墩墩等你来赢:一起 DIY 冰墩墩!

- 揭Altera MAX10神秘面纱,下载白皮书,抢楼赢好礼!

- 泰克WiFi预一致性测量方案介绍会 填问卷 赢好礼

- STM32嵌入式网络开发套件,超震撼冰点价火爆开团!

- DEYISUPPORT:【全新FAQ来袭】今夏且听风吟,你不能错过的精华!

- TE白皮书下载|《散热桥技术——电子设备散热领域的创新》

- 安全的革新,全新的验证方式 下载富士通 《频谱验证解决方案 》白皮书 好礼送!

- 英飞凌MERUS™ D类音频解决方案|【阅读赢好礼,下单送开发板】

System-On-a-Chip Design Challe

System-On-a-Chip Design Challe 算法和并行体系结构之三

算法和并行体系结构之三

京公网安备 11010802033920号

京公网安备 11010802033920号