自最初开始设计 PCB 以来,约束一直是定义成品物理电路板所必要的元素。尺寸和铜重量是最早的约束。而现在,高速的设计对电子设备的诸多参数有约束要求,尤其是差分对。

关键字:PCB 约束驱动 差分对布线 PADS Mentor Graphics

编辑:chenyy 引用地址:约束驱动型设计使差分对布线变得更简单

定义约束的目的在于尽可能多地消除错误来源,即消除那些需要设计返工的错误。而且,设计错误发现得越晚,返工成本就会越高。理想状况下,“设计即正确”的方法可使约束得到严格遵守,从而在设计过程中消除错误的可能性。但事实上,尽早验证信号完整性对确保满足所有约束至关重要。

设计不佳的用户界面往往是令约束设置既繁琐又耗时的原因之一。必须打开多个窗口,而且无法一次看到所有约束,这种设置方式往往令人晕头转向,极易出错,而且迫使用户一次只能手动更新一项约束。

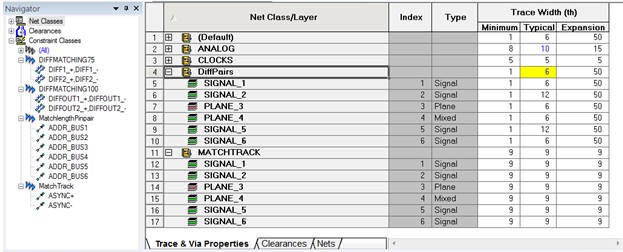

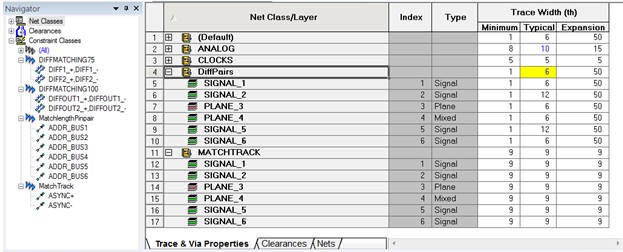

更多如Mentor Graphics PADS 产品等更为现代化的设计工具,均使用基于电子表格的方法简化了导入和评审约束的操作,相比基于对话框的传统方法具有明显的优势。

图 1:约束管理可能非常复杂,尤其在使用基于对话框的传统环境时。PADS 所使用的基于电子表格的方法简化了整个过程

利用强大的电子表格编辑功能(例如,多行/多列复制/粘贴和自动填充),可以快速导入或修改大量约束值。通过打开 PADS Constraint Manager 的两个实例,允许将约束值从一个项目复制到另一个项目,从而提供约束复用功能。

约束规范

一个特定的设计项目可能包含多个有用或无用的约束。常用的设计约束如下:

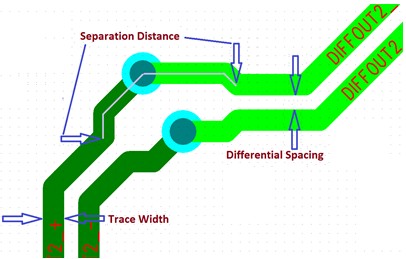

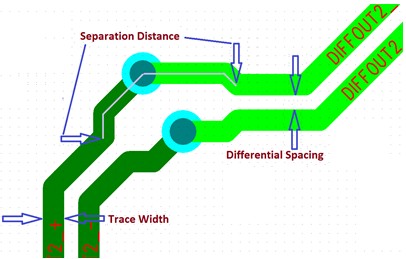

A.差分对约束包括:走线宽度、差分间距和最大分隔距离。最大分隔距离是一项层相关的约束,指定了走线在违反差分间距值的情况下能够并行布线的长度。

图 2:差分对约束

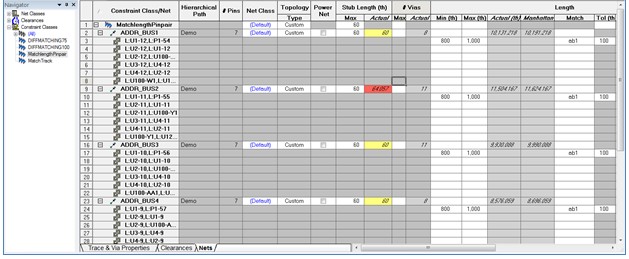

B.拓扑约束限制特定网络的布线模式。它们用于控制布线结构以及对网络分支(管脚对)施加长度限制。拓扑类型和最大支线长度是两类常见约束。拓扑类型可以不针对布线设置任何限制,或者以规定的方式限制布线。

最大支线长度约束应用于使用受约束的拓扑的网络类型。它限制了由邻近网络分支共用的走线长度。两项约束均可在约束类级别指定,或在单独的网络上加以覆盖。

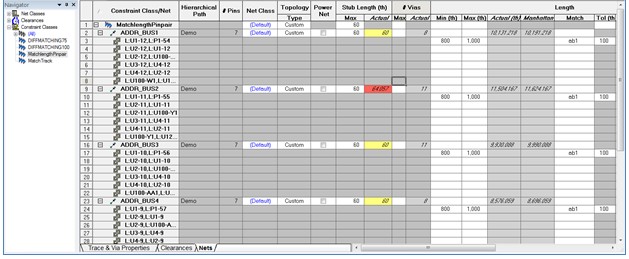

C.长度约束针对网络和网络分支的布线长度施加限制,包括最小长度、最大长度和匹配长度。最小和最大长度约束可分配给约束类、单独的网络或单独的网络分支(管脚对)。

要定义差分对的匹配长度约束,需要使用匹配长度组。此方法针对组成员的相对长度设定限制,即任意两个组成员之间的长度差不得超过指定的容差值。匹配长度组可能包含网络或网络分支(管脚对)。不允许在一个组内混合网络和管脚对。

D.布线约束针对布线层、过孔使用和走线宽度施加限制。布线约束在网络类级别定义,并应用于网络类中的所有网络。它们对布线层的使用、布线允许的过孔类型以及允许的走线宽度范围施加限制。

图 3:此份关于 Mentor Graphics PADS Standard 的样例电子表格视图显示了可为具有自定义拓扑的单独网络分支指定的约束类型。此处显示了匹配长度限制和支线长度违规

E.间距约束定义了特定布线层上两个布线对象(例如走线、焊盘和铜皮区域)边缘之间允许的最小间距。

F.电源网络约束——诸如 PADS 之类的工具会基于预定义的标准名称(例如 GND、VCC、+5V、-12V 等)自动识别电源网络。

按类分组

在设计流程的早期阶段对网络类和约束类进行正确的分组和定义,可显著简化约束的定义和管理。分组约束可提高 PCB 设计效率,缩短设计时间,以及最终节省 PCB 设计成本。

差分对是由实施差分信号的两个物理网络构成的组。随着差分对数量的增加,一次定义一个差分对的做法变得极为繁琐。而自动化可快速、轻松地创建差分对。网络名称通常遵循模式名称。使用这些模式查找您想要分配为差分对的网络名称。随即显示建议的差分对列表;取消选中您不想分配的匹配项。

对于差分对,可以定义层相关的差分对间距。网络类用于组织和加快具有类似特征的网络的布线约束定义。对于网络类,您可以定义允许布线的层、这些层对应的走线宽度范围,以及网络类中的网络所允许的过孔类型。

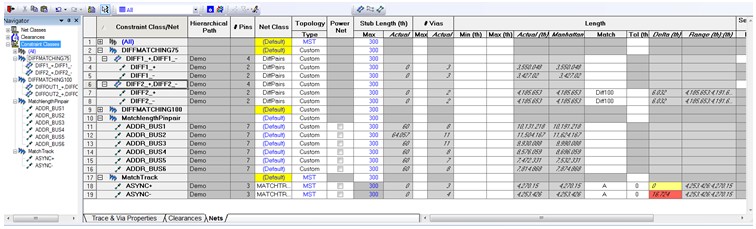

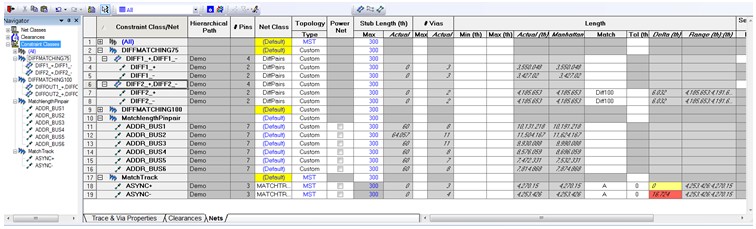

约束类用于组织和加快具有类似电气和时序属性的网络的长度、拓扑和其他约束定义。尽管分配给约束类的约束会自动应用于类中的所有网络,但也可以为单独的网络、管脚对和差分对自定义特殊的约束值。

图 4:利用 PADS 的约束类,无需为单独的网络创建长度和拓扑约束

违规

传统上,约束违规是在您的 PCB 设计工具中执行检查和评审。PADS 工具支持在 PCB 设计环境或在约束管理环境内查看约束违规。通过在定义约束的环境内查看违规,工程师和设计人员可采用类似的方法访问此过程,这对工作流而言也更为自然。

查看并分析违规可使工程师在发现违规后即刻做出纠正。这是至关重要的一步,因为随着设计的进一步执行,修复问题所花费的成本会变得更高。通过在设计工具内查看违规,错误可在最短的时间内以最低的成本得到修复。

总结

约束管理应专为满足设计人员的日常工作过程需求而设计,具有直观、快速和简易的特点。采用统一的方法可确保实现“设计即正确”方法,并且消除在原理图与 PCB 设计环境中使用单独的约束管理工具所造成的错误。整个流程期间所有约束应同步并可访问。Mentor Graphics PADS 是约束驱动型 PCB 设计的理想工具。

上一篇:Cadence中国用户大会 CDNLive八月上海盛大召开

下一篇:晶心科技推出Knect.me生态系统

推荐阅读最新更新时间:2023-10-12 23:35

PCB技术:电源与地之间接电容的原因

pcb技术:电源与地之间接电容的原因 G.高频滤波电容应尽可能靠近IC电路的电源引脚处。 滤波电容焊盘至连接盘的连线应采用0.3mm的粗线连接,互连长度应≤1.27mm 2.低频滤波电容的配置 A.每5只高频滤波电容至少配接一只10μf低频的滤波电容; B.每5只10μf至少配接两只47μf低频的滤波电容; TC.每100cm2范围内,至少配接1只220μf或470μf低频滤波电容; D.每个模块电源出口周围应至少配置2只220μf或470μf电容, 如空间允许,应适当增加电容的配置数量 ; E.低频的滤波电容应围绕被滤波的电路均匀放置。 原理图中是为了好看才画在一起 的.PCB中应该画在芯片电源管脚处.尽量靠近芯片。原理图上

[电源管理]

Mentor Graphics 推出用于多学科无缝协作的 Xpedition 多板系统

俄勒冈州威尔逊维尔,2016 年 10 月 24 日 Mentor Graphics 公司(纳斯达克代码:MENT)今天宣布推出全新的 Xpedition 多板系统设计解决方案,帮助多学科团队开展无缝协同协作,以便高效管理日益复杂的系统。Xpedition 流程可消除设计流程中的冗余工作,进而最大限度地提高团队效率,同时还可借助数据管理基础设施优化产品性能和可靠性。如此一来,便可确保数据完整性,以及将可重复使用的 IP 用于系统中的所有电路板、连接器和电缆。

要设计包含多个互连电路板(连接器和/或电缆)的系统,过去通常会使用多种桌面办公工具(例如,可确保电路板内部连接的电子表格、记录系统元件参数的文本文件以及可显示模

[嵌入式]

IPC报告显示11月份北美PCB行业延续走强态势

2018年1月3日,美国伊利诺伊州班诺克本 — IPC — 国际电子工业联接协会® 近日发布《2017年11月份北美地区PCB行业调研统计报告》。报告显示11月份订单量和出货量均继续增长。订单出货比维持在1.09的高位。 2017年11月份北美PCB总出货量,与去年同期相比,增长了4.0%;年初至今的出货量仍低于去年同期2.3%。与上个月相比,11月份的出货量增长了0.4%。 2017年11月份,北美PCB订单量,与去年同期相比,增加了15.8%;年初至今的订单量高于去年同期5.7个百分点。与上个月相比,11月份的订单量下降了3.8%。 IPC市场调研总监Sharon Starr女士说:“11月份北美PCB行业持续向好

[其他]

msp430的pcb设计小结

msp320的最小系统pcb设计总结,分为4个模块: (1)复位电路模块 (2)晶振电路模块 (3)电源模块 (4)JTAG下载模块 问题: gnd与agnd的处理:数字地和模拟地要隔离,防止互相干扰(数字地上的谐波成分要远多于模拟地,共地的话会影响模拟地的稳定性) ,可通过0Ω电阻连接起来。 待更。。。

[单片机]

Altium 赞助“PCB板级电路设计大赛”

本周初,为期五天的第二届海峡论坛在福建省厦门市取得圆满成功。本届“海峡论坛”的共同主办单位有国务院台湾事务办公室、商务部、文化部、工信部、教育部、等十多个部委和福建省人民政府。Altium为第二届海峡论坛之“PCB板级电路设计大赛”提供产品及技术支持,旨在为培养电子行业的创新型专业人才提供最先进的技术和最好的平台。

“我们非常高兴能够为本次大赛提供产品及技术支持,使两岸的青年电子工程师能够使用到最先进的电子设计工具和技术,以帮助他们实践创新理念,实现创新梦想。”Altium大中国区CEO沈宇豪说道,“Altium相信下一代设计解决方案可以帮助电子工程师扫除障碍,实现电子设计创新。Altium致力于全面培养中国新一

[半导体设计/制造]

法院驳回Synopsys申请延后执行Mentor Graphics诉求

俄勒冈州威尔逊维尔,2015 年 4 月 20 日 Mentor Graphics 公司(纳斯达克代码:MENT)今日宣布,美国联邦巡回上诉法院已驳回 Synopsys 申请延后执行俄勒冈州联邦地区法院就 Synopsys 硬件仿真器发布的禁制令(待决上诉)的诉求。该禁制令发布于3 月 12 日,禁止 Synopsys 公司在美国制造、使用、销售、提供销售、许可或租赁任何涵盖 Mentor Graphics 专利硬件仿真技术(美国专利号为 6,240,376)的硬件仿真器或软件。

该禁制令还禁止 Synopsys 从美国境外将任何涵盖 Mentor 专利技术的硬件仿真器进口至美国,以及销售或租赁侵权硬件仿真

[嵌入式]

可制造性设计 -- 促进生产力的强大工具

“DFM”- 一个由三个字母组成的缩写,其意义依据你在设计及制造流程链中所扮演的角色不同而不同,或是微不足道,或是举足轻重。

在今天的电子业,有几种力量正在推动着可制造性设计(DFM)的进程,其中最常见的三种为:

* 新技术带来的零件密度的增加

* 缩短设计周期时间的需求

* 外包及海外制造模式的实行

要求设计更小更轻,同时又要拥有更多功能的不断增加的需求为我们带来了新的印刷电路板制作技术,如顺序迭构,嵌入式被动及主动零件类的设计,以及零件封装技术的创新如Micro-BGA、CSP和POP。所有这一切都使PCB设计、制作及组装变得更加复杂化。

缩短“产品

[模拟电子]

小广播

热门活动

换一批

更多

最新半导体设计/制造文章

- 英特尔中国正式发布2023-2024企业社会责任报告

- 贸泽电子与Analog Devices联手推出新电子书

- AMD 推出第二代 Versal Premium 系列:FPGA 行业首发支持 CXL 3.1 和 PCIe Gen 6

- SEMI:2024Q3 全球硅晶圆出货面积同比增长 6.8%、环比增长 5.9%

- 台积电5nm和3nm供应达到"100%利用率" 显示其对市场的主导地位

- LG Display 成功开发出全球首款可扩展 50% 的可拉伸显示屏

- 英飞凌2024财年第四季度营收和利润均有增长; 2025财年市场疲软,预期有所降低

- 光刻胶巨头 JSR 韩国 EUV 用 MOR 光刻胶生产基地开建,预计 2026 年投产

- Imagination DXS GPU 已获得ASIL-B官方认证

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

11月13日历史上的今天

厂商技术中心

西电-印刷电路板(PCB)设计指南_1-99

西电-印刷电路板(PCB)设计指南_1-99 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号