“老虎不发威,你当我是病猫啊!”日前在京举办尖端制造日峰会时,英特尔公司全球副总裁兼中国区总裁杨旭霸气地表示,杨旭的信心则来自英特尔,来自全球首款真正意义上的10纳米晶元,“这是摩尔定律最实打实的证明,摩尔定律没有死,摩尔定律仍然在向前发展。”英特尔公司制造、运营与销售集团总裁Stacy Smith面对镜头,向全球展示了英特尔首款10纳米晶圆。

为什么要挑战摩尔定律

在1965年4月19日,戈登.摩尔在Electronics Magazine上提出了一个推测,既芯片中的晶体管数量每一年都会翻一番,10年后,修改为每两年翻一番。自此以后,便成为半导体领域的圣经,每个半导体业者都遵从的原则。

发明摩尔定律一词的加州理工大学的教授Carver Mead此前接受媒体访问时所说:“这(摩尔定律)几乎成了对人类创造力和对未来信念的宗教信仰,它使每个人都认为技术进步将永远持续下去。”

而在最近,越来越多的人开始质疑摩尔定律即将失效,开始出现更多关于more than Moore,beyond the Moore之类的词汇,甚至2016年自然杂志都撰刊称,“下个月(当时出版时间为2016年2月)即将出版的国际半导体技术路线图,不再以摩尔定律为目标了。芯片行业50年的神话终于被打破了。”

挑战摩尔定律的背后,实际上是业界对英特尔的挑战。2017年2季度财报的相继出炉,伴随着内存价格的不断攀升,外加PC市场的不断萎靡,三星最终以158亿美元的销售额超过了英特尔的147.6亿美元,取代英特尔成为半导体芯片市场新霸主。英特尔自1992年起,一直是全球排名第一的半导体公司,然而最近几年,随着手机等智能终端业的发展速度远超PC业,英特尔的销售增长乏力,这也给了其他公司机会。

而随着AI热潮的到来、GPU、ASIC以及FPGA也在不断挑战着CPU的领导地位。2016年4月,NVidia发布Pascal架构,峰值性能达到11TFLOPS/s,黄仁勋在彼时接受新智元专访时表示,半导体技术迭代在放缓,但GPU Pascal架构比上一代性能在两年内提升了近十倍,因此可以说我们正处在一个“超级摩尔定律”时代。

英特尔这只老虎是真的病了吗?真的落了平阳了吗?我想每个人都有自己的看法,拓墣产业研究院经理林建宏此前接受媒体访问时表示,英特尔2016年研发预算占到其年营业额的22%,为127亿美元,是全球全球半导体产业总研发经费的23%。这个数字足以证明英特尔在半导体产业界的领导力和话语权。

英特尔需要捍卫的不止是摩尔定律,更是公司在半导体领域的霸主地位。2005年公司曾经悬赏一万美金,以收藏当初发表摩尔定律文章的杂志。那时,AMD 64位CPU在市场广受好评,借助架构的调整创新,几乎就要打败英特尔,坚守摩尔定律的英特尔不得不做出让步以多核架构取代传统摩尔定律单纯的对于频率提升的要求。而这一悬赏环节,也被认为是英特尔捍卫摩尔定律的一次重要的公关活动。

今天,在英特尔出现坎坷之时,捍卫摩尔定律的口号被再一次提出。

摩尔定律的本质是经济学

“摩尔定律的核心反映了一个真理那就是经济学原理:按照特定节奏推动半导体制造能力的进步,我们就可以降低任何依赖于计算的商业模式的成本。”Smith道出了摩尔定律的本质,而英特尔一直以来的商业模式也是依此进行的。

“摩尔定律现在可能需要更长的时间,但是我们能够实现更高的密度提升,此外还有非常重要的一点,正是因为每个制程技术更高的生命周期,我们能够实现同一节点内每一年的增强。我们把它称为14nm+、14nm++的命名方式,对于10纳米制程技术也是这样。我们每一年都做捆绑的架构、性能、功能的优化,让我们的客户得到更好的优化惠及。”Smith说道。

Smith这么说的背后,是英特尔放弃了Tick-Tock模式。Tick-Tock的运行模式一度被认为是摩尔定律的经典提现,每一次“Tick”代表着一代微架构的处理器芯片制程的更新,意在处理器性能几近相同的情况下,缩小芯片面积、减小能耗和发热量;而每一次“Tock”代表着在上一次“Tick”的芯片制程的基础上,更新微处理器架构,提升性能。Tick和Tock之间的时间间隔通常为12到18个月。

英特尔公司全球副总裁、逻辑技术开发部联席总监白鹏透露,10纳米产品将会依然有三代,产品策略上不会回到Tick-Tock。“从技术节奏角度来讲,14纳米和10纳米,我们迈的步比较大一点。”实际上,这也是《自然》杂志质疑摩尔定律的重要原因,英特尔原计划2016年推出的10纳米Cannonlake处理器跳票了,直到此次尖端制造日上展示了10nm晶圆,几乎晚了一年左右。

随着制程尺寸的生命周期正变得更长,英特尔的芯片开发策略也将从两步变为三步:在制程工艺和架构升级之后再增加一个“优化”步骤,即制程-架构-优化。

Tick-Tock的失效并不意味着摩尔定律的失效,Smith以英特尔晶体管密度数据举例:

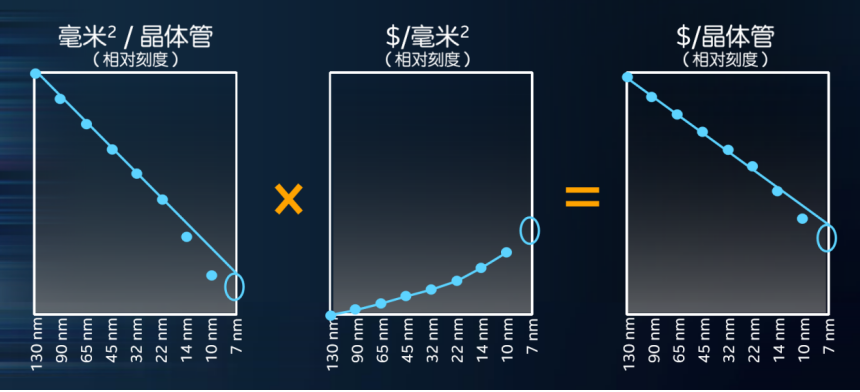

如图所示,根据计算,在10nm甚至7nm的制程中,晶体管的成本下降得更快,按照摩尔定律的经济学原理来说,依然有效。“我们卖的不是晶体管而是成本。”Smith强调。

如图所示,虽然技术演进过程延长,但晶圆面积缩小得更快。

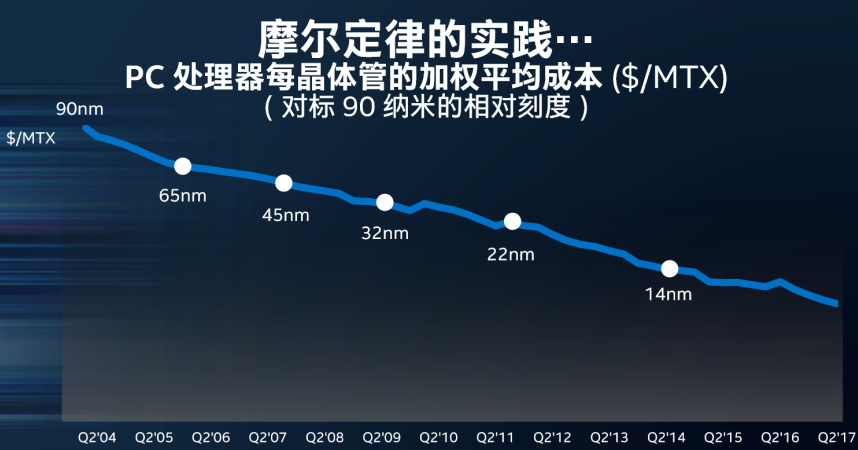

Smith指出按照成本分析,尽管14nm有了三代产品,但成本更低,依然满足了摩尔定律。

从2004年起,处理器每晶体管的加权平均成本如图所示,依然是不断下降的。“这其实展示了践行摩尔定律带来的好处,尽管每个节点拉长但是仍然能获得成本优势。”Smith说道。“我们在不同领域的产品都是居于领先的位置,同时还有60%的利润提升,这表明摩尔定律仍在生效。”

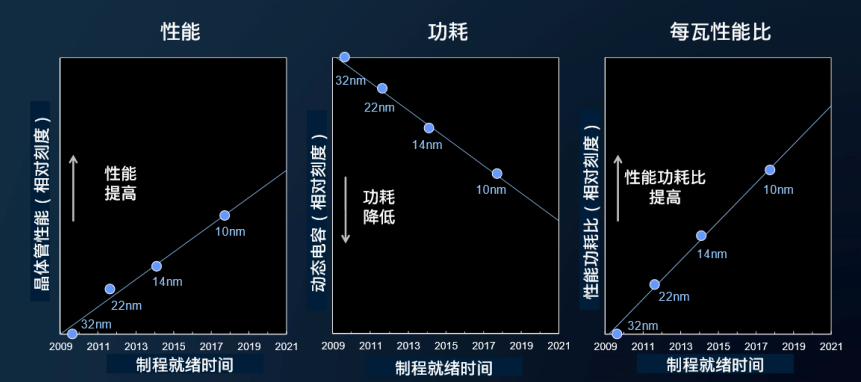

除了成本,性能功耗比也是不容忽视的,英特尔高级院士、技术与制造事业部制程架构与集成总监 Mark Bohr表示,“降低功耗也是摩尔定律的一个重要目标。”

从晶体管密度说开

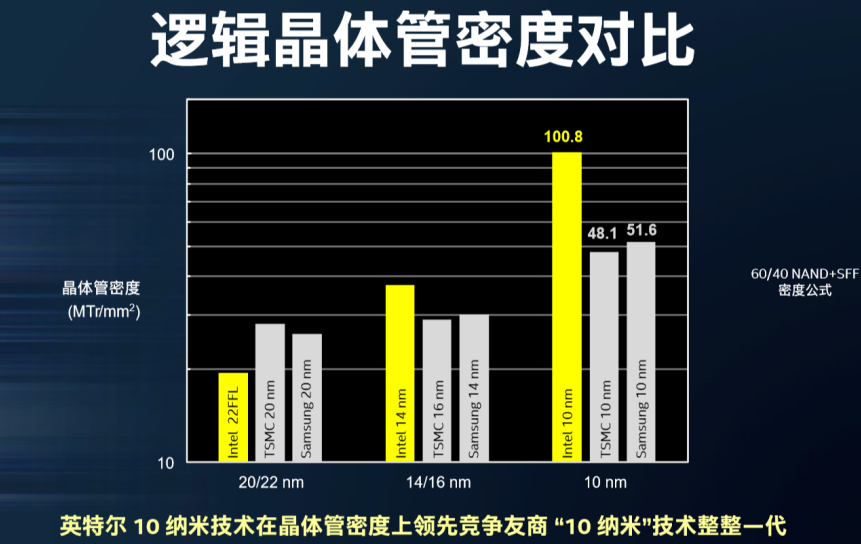

尽管三星和台积电的10nm产品已开始发售,但Smith强调,友商的产品在密度上并没有提升,“友商10纳米的制程技术晶体管密度只相当于英特尔14纳米制程晶体管密度,却晚于英特尔14纳米制程三年,业界沿用的这样一种节点命名的方式导致了观念的混淆,我们认为制程技术应该以实践来度量。”Smith说道。

从杨旭的玩笑话,到Smith的直接PK,可以看出英特尔确实是比较恼火,最重要的原因,是命名乱象破坏了摩尔定律。摩尔定律是指每一代制程工艺的晶体管密度加倍,纵观发展史,业界在命名新制程节点时会比上一代缩小30%,这种线性缩放意味着晶体管密度提高一倍,是符合摩尔定律的。近来,也许是因为进一步的制程升级越来越难,一些竞争友商公司背离了摩尔定律的法则,即使晶体管密度增加很少,或者根本没有增加,但他们仍继续推进采用新一代制程节点命名。这么做的结果是对摩尔定律产生了更多的质疑。

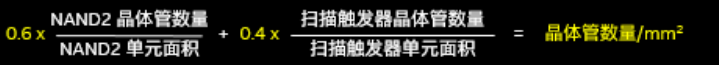

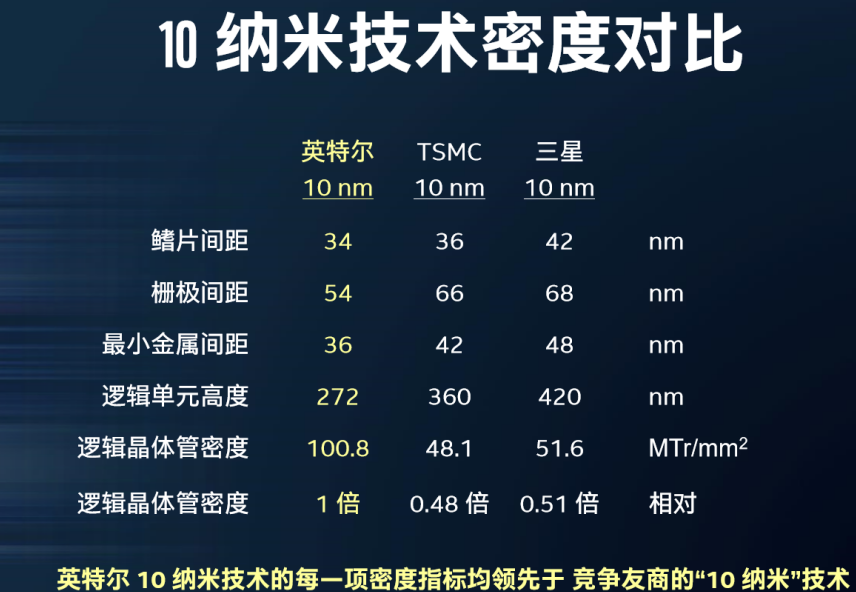

Bohr表示,此前的逻辑密度计算公式都是采用栅极间距×逻辑单元高度,这样使面积缩小,密度提高,然而目前来看该公式并不完善,业界普遍应采用以下公式更为准确,利用两个非常重要的逻辑概念,NAND单元和扫描触发器逻辑单元,分别计算密度后再进行加权,才可以更加准确地计算逻辑晶体管的密度。

若按照此公式进行评估,14纳米和10纳米密度提升得更多,分别为2.5倍和2.7倍。

开发历程超过摩尔定律的两年周期,但平均计算结果仍约两年一倍。

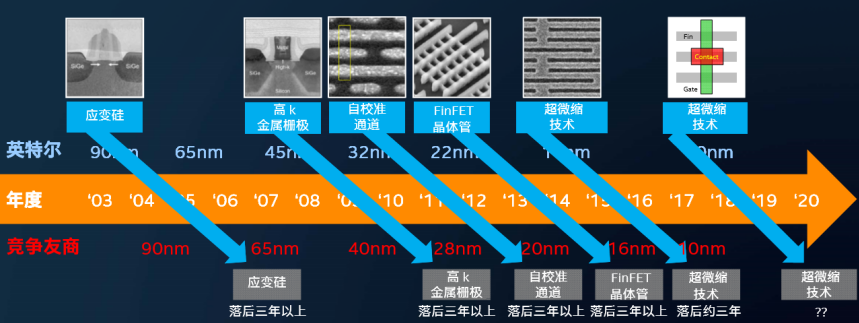

超微缩技术领先竞争对手3年

Bohr表示,从2003年起,英特尔的技术就领先对手三年以上。

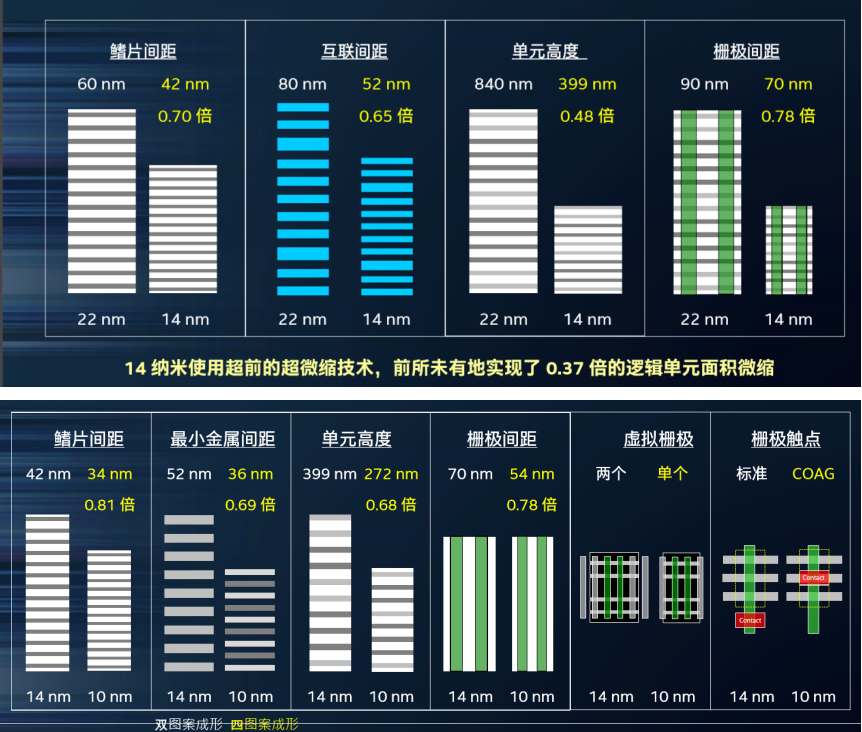

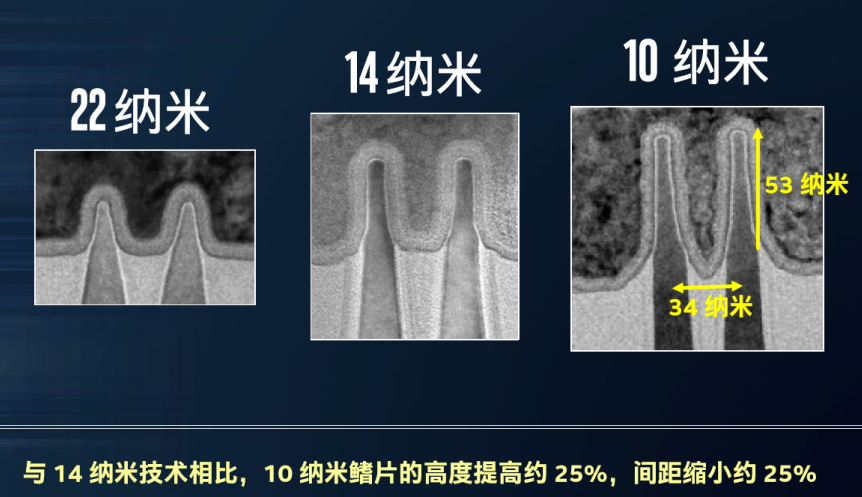

“我们在14纳米工艺上采用了超微缩技术,鳍片间距进行60纳米到42纳米的微缩,互联间距也从80纳米降低到了52纳米,极大的下降单元高度从840纳米下降到339纳米,栅极间距从90纳米降低到70纳米这也是一个非常巨大的提升,正是基于这一系列的提高,由于超微缩技术在14纳米工艺上的应用我们前所未有实现了0.37倍的逻辑单元性能提升。”Bohr说道,“而在10纳米上,鳍片间距更是从42纳米降低到34纳米,最小金属间隔从52纳米微缩到36纳米,单元高度、栅极间距也分别从399纳米降低到272纳米以及70纳米到54纳米。此外,虚拟栅极从两个降低到单个,并采用了栅极触点,将晶体管密度提升2.7倍,逻辑晶体管密度从37.5Mtr/mm2提高到100.8 Mtr/mm2”

Bohr特别拿出了与三星和台积电的逻辑晶体管密度对比,可以看出在10nm制程中,英特尔的密度远远大于竞争对手。“并不是所有声称10纳米技术就能够真正做到10纳米的。”他有些嘲讽地说道。“我们使用的并不是字节命名,真正关键的是详细技术规格本身,只有量化标准才能更好地衡量我们的技术究竟有多先进。”

Bohr强调,英特尔的超微缩技术不仅仅针对逻辑单元,也被用在了SRAM单元中,对比14纳米,SRAM单元面积缩小了约0.6倍。

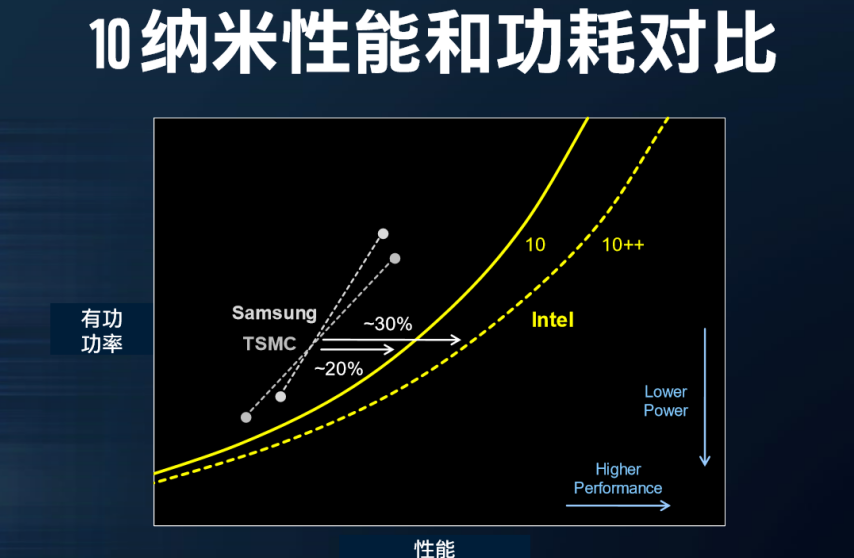

随着移动平台市场更强烈的需求,Bohr也特别拿出了性能功耗比比较图,图中可以看出,10nm工艺下,相同功耗下,通过增强驱动电流,英特尔可以提高20%的性能,10nm++工艺则可提升30%。“这些增强不仅仅为了持续优化产品性能,我们希望延长技术生命周期。”

Bohr特别强调,除了针对CPU的优化,10nm还有各类衍生技术,以针对不同种SoC,包括高性能晶体管、低漏电晶体管、模拟/射频晶体管、HV I/O晶体管,高-Q电感器等等。而针对多芯片堆叠选项,提供了包括低成本、高密度以及高性能等选项。

预测未来,更是创造未来

“作为英特尔来讲我们不仅仅做到预测未来,我们是创造未来。”Smith表示。

“每一次我们做新技术都会有很多很难的问题,我已经做了十代技术,每一代我们在制作的过程中都觉得很难,但是回过头想,比我们现在做得都容易太多了。10纳米也是这样,做的时候感觉很难,但我们迟早会做出来。一般说来微缩是比较难的,下一代的技术你想把晶体管变小,“光刻”技术还没有跟上,所以微缩会比以前花的精力更多一点。我想如果两年后你问这个问题,我会告诉你10纳米很容易,7纳米很难。”白鹏说。

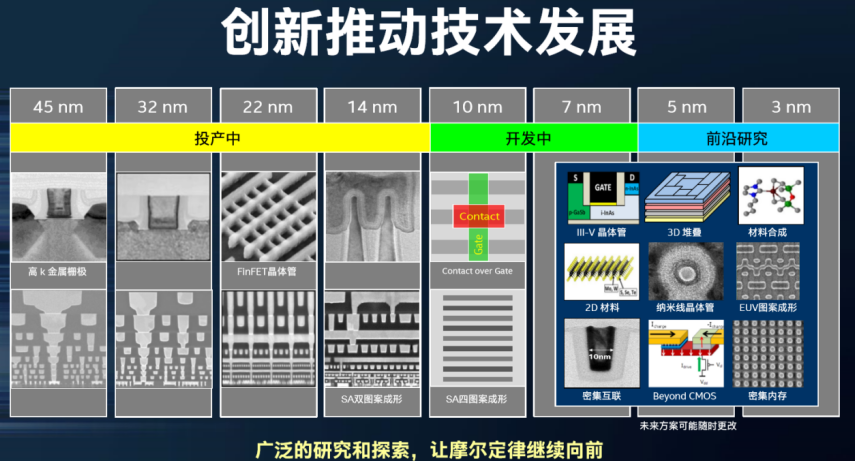

Bohr也表示,英特尔不断进行前沿技术开发,以保持摩尔定律继续向前。包括III-V晶体管、3D堆叠、材料合成、2D材料、纳米线晶体管、EUV、密集互联、神经元计算、自旋电子学以及密集内存等等。

“所有这些前沿性的研究都是在英特尔俄勒冈园区做的,这是英特尔逻辑技术主要的研发园区,也是主要的生产基地之一,那里有机房,有办公区域,所有核心的团队在同一个地方协同合作,从而快速、高效做决策。英特尔的技术领先性就是因为这种跨领域团队之间的密切合作带来的。”Bohr说道。

白鹏同样表示:“过去15年英特尔一直在工艺技术上领先业界,有几个很重要的因素。首先我们有一个行之有效的“科技规划模式”,就是从研究、开发到量产这几个步骤当中非常合理的安排,第二是在研发的资源或者资金方面投入没有一丝妥协,第三是有非常优秀的团队,这个团队在这个业界已经工作了至少二三十年,第四则是英特尔强调创新的企业文化。”

Bohr透露,目前7nm技术和5nm技术都在进行开发,“我希望给大家吃一颗定心丸,那就是摩尔定律还会继续推进整个行业以及英特尔的发展,并不仅仅是技术快速创新,我们的生产以及制程也会不断演进。”

“如果您是20年前问半导体业内专家,他们会告诉你摩尔定律还能继续十年,十年之前你再问行业专家,他们还会说十年,现在你问我,我还是会回答十年。我们就拿海平面做一个比方,你离海平线越来越近,但它还是不断往前推进的。”作为英特尔工艺制程的舵手以及延续摩尔定律的掌门人,Bohr能做到的就是继续航行。

上一篇:罗姆赞助的重要第十一届国际纳光电子研讨会圆满落幕

下一篇:英特尔一年举办两次精尖制造日 这次在中国有什么不同

推荐阅读最新更新时间:2023-10-12 23:54

- 贸泽电子与Analog Devices联手推出新电子书

- AMD 推出第二代 Versal Premium 系列:FPGA 行业首发支持 CXL 3.1 和 PCIe Gen 6

- SEMI:2024Q3 全球硅晶圆出货面积同比增长 6.8%、环比增长 5.9%

- 台积电5nm和3nm供应达到"100%利用率" 显示其对市场的主导地位

- LG Display 成功开发出全球首款可扩展 50% 的可拉伸显示屏

- 英飞凌2024财年第四季度营收和利润均有增长; 2025财年市场疲软,预期有所降低

- 光刻胶巨头 JSR 韩国 EUV 用 MOR 光刻胶生产基地开建,预计 2026 年投产

- Imagination DXS GPU 已获得ASIL-B官方认证

- arm召开2025二季度财报会,V9架构继续大获成功

鲲鹏处理器架构与编程 (戴志涛,刘健培)

鲲鹏处理器架构与编程 (戴志涛,刘健培) 无人驾驶 (胡迪·利普森)

无人驾驶 (胡迪·利普森) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号