在 Beligum 安特卫普的 ITF World 2023 上,英特尔技术开发总经理 Ann Kelleher 概述了英特尔在几个关键领域的最新发展,其中最有趣的启示之一是英特尔未来将采用堆叠式 CFET 晶体管。这标志着英特尔首次在其演示中展示这种新型晶体管,但 Kelleher 没有提供生产日期或确定的时间表。

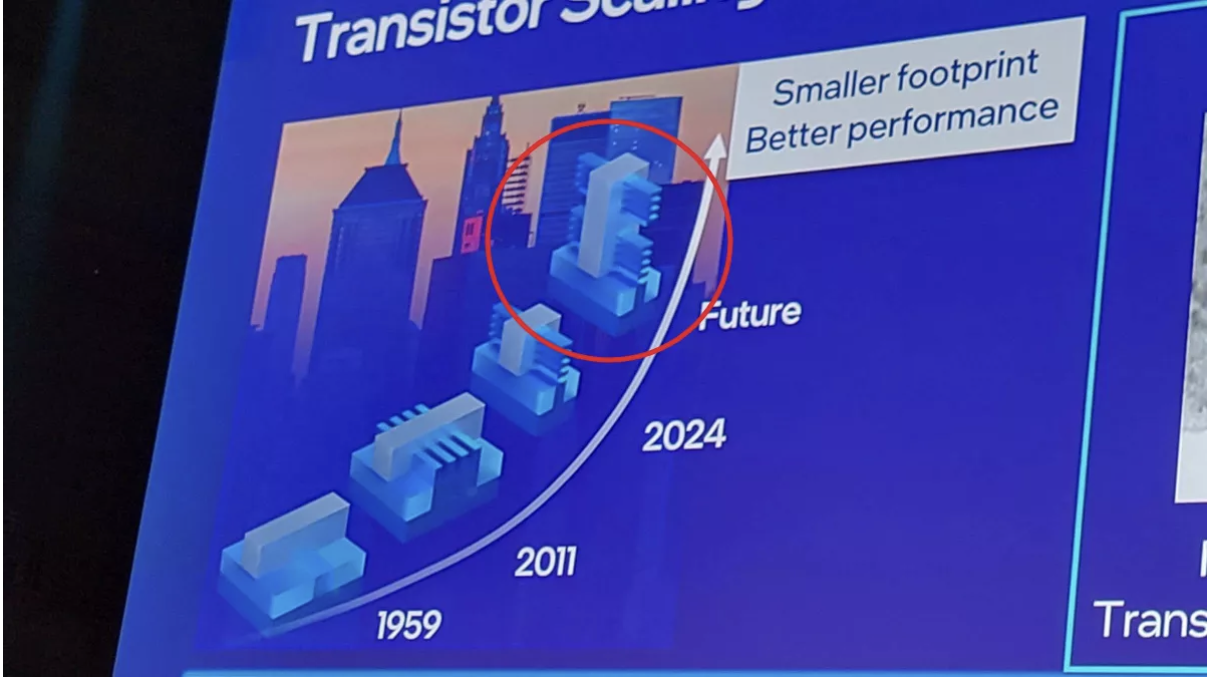

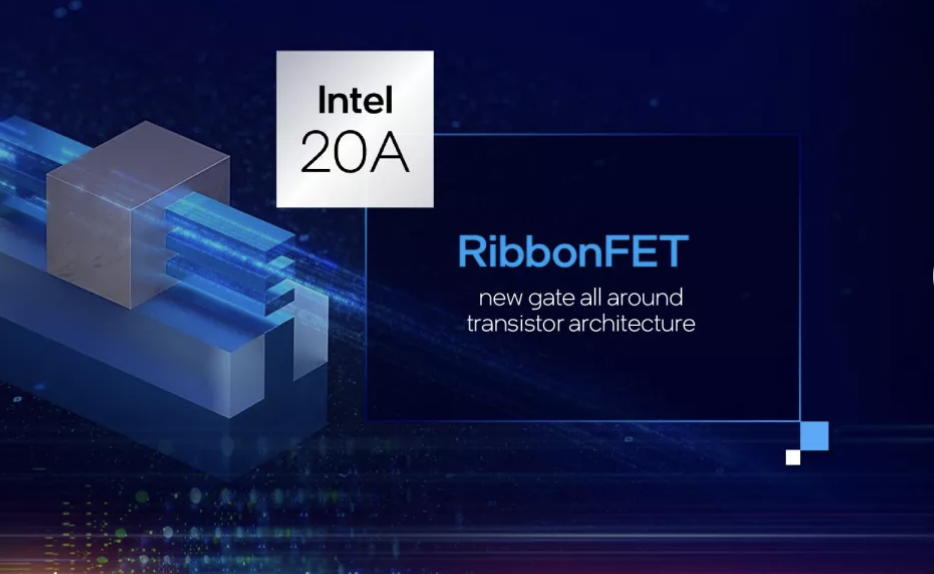

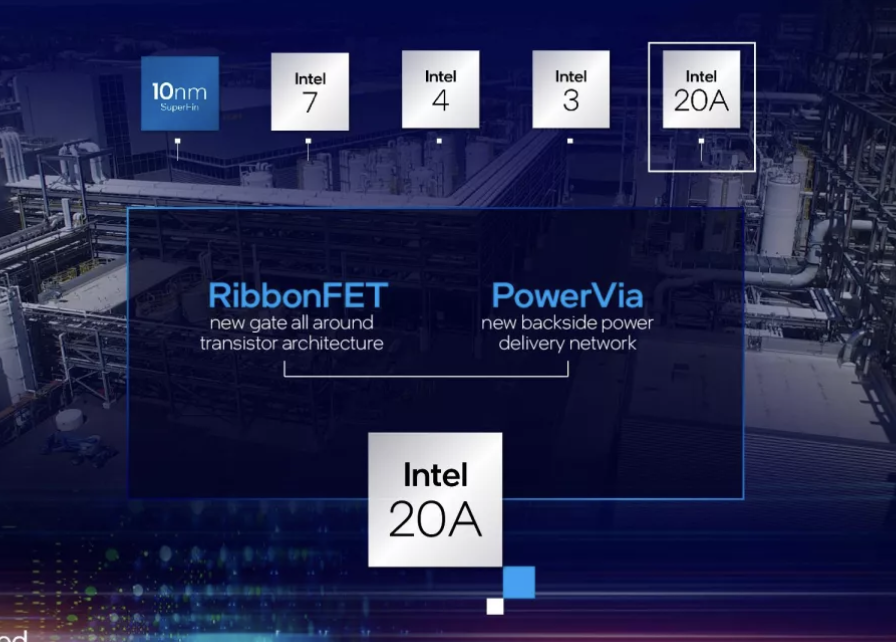

在这里我们可以看到放大版的幻灯片,在新型晶体管周围添加了一个环。幻灯片底部的前两种晶体管类型是较旧的变体,而“2024”条目代表我们过去广泛介绍过的英特尔新型 RibbonFET晶体管。英特尔第一代采用“intel 20A”工艺节点的设计具有四个堆叠的纳米片,每个纳米片都被一个门完全包围。Kelleher 说,这种设计有望在 2024 年首次亮相。RibbonFET 使用环栅 (GAA) 设计,它可以提高晶体管密度和性能,例如更快的晶体管开关,同时使用与多个鳍片相同的驱动电流,但在面积较小。

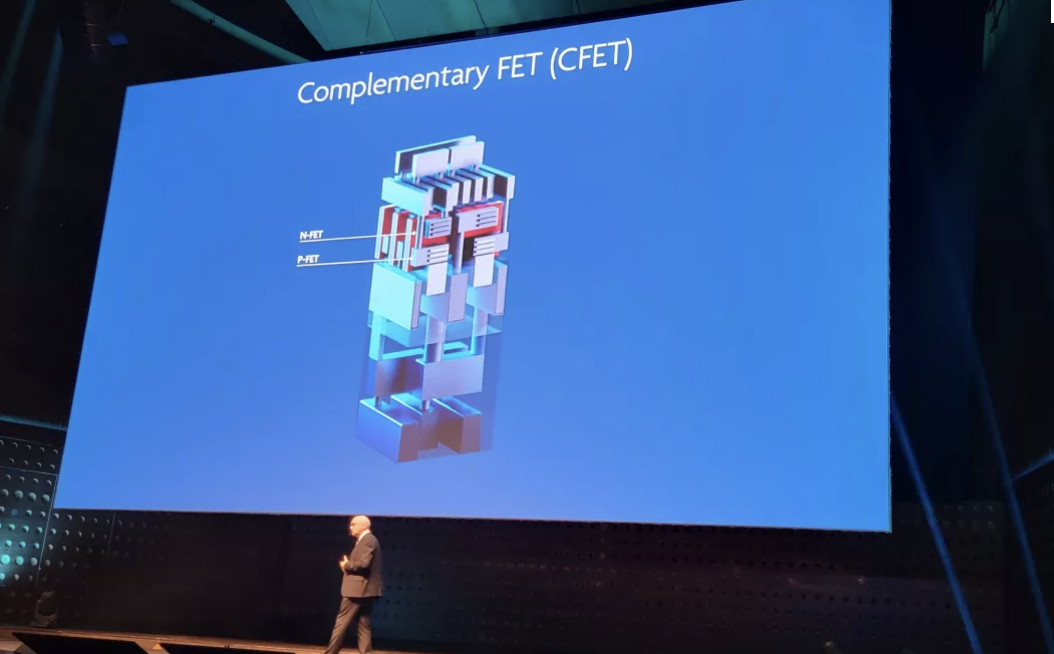

Kelleher 的幻灯片还展示了英特尔的下一代 GAA 设计——堆叠式 CFET。互补 FET (CFET) 晶体管设计已经出现在imec 的路线图上一段时间了,但我们还没有在英特尔幻灯片上看到它,也没有听说该公司表示计划采用这种设计。提醒一下,imec 研究所研究未来的技术,并与业界合作以实现它们。

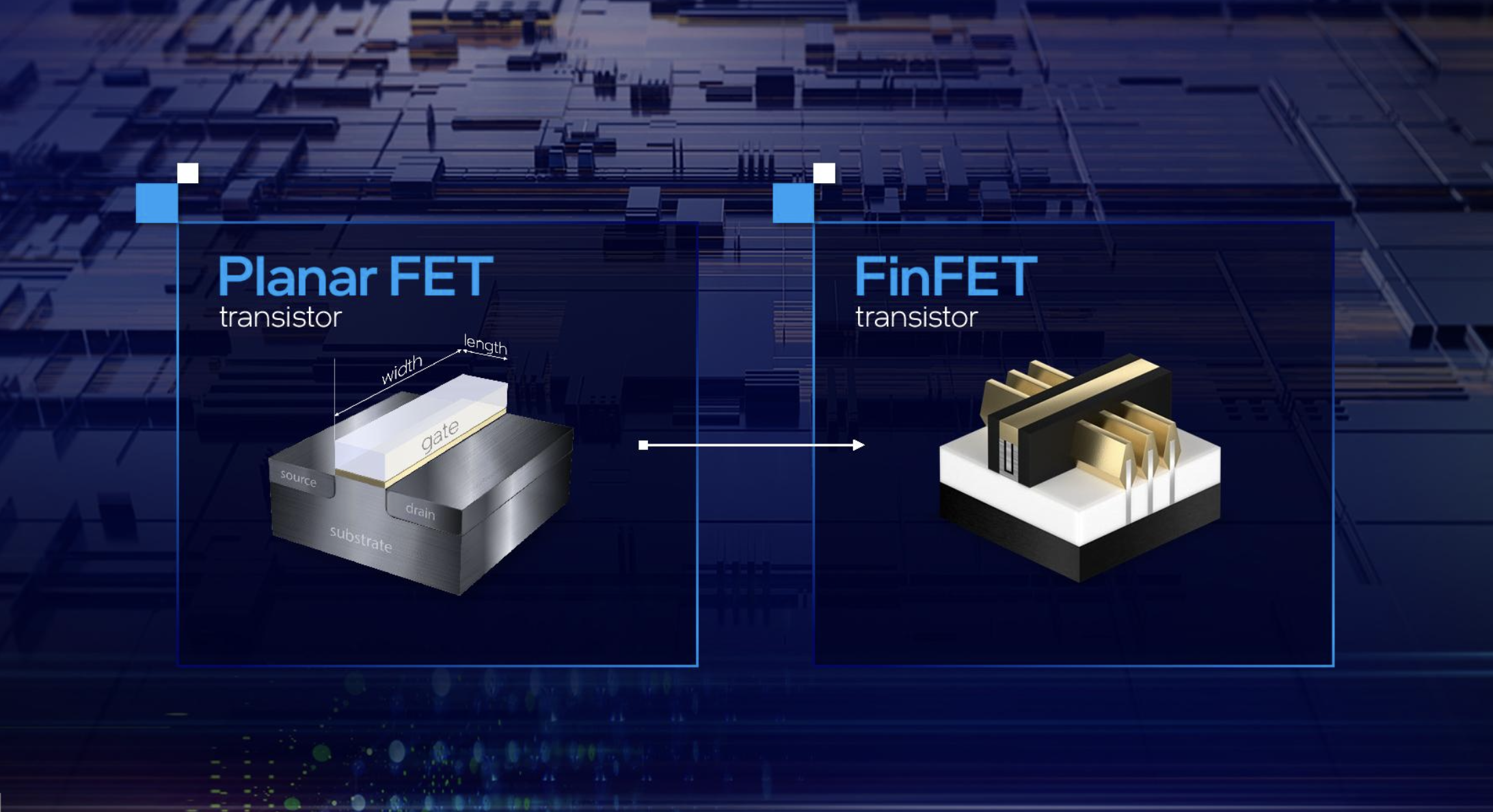

自然地,英特尔的程式化渲染与我们在上面相册的第一张图片中包含的 imec CFET 渲染之间存在一些差异,但英特尔的图片很好地传达了这一点——这种设计允许公司堆叠八个纳米片,是四个与 RibbonFET 一起使用,从而增加了晶体管密度。我们在上面的相册中还有其他三种类型的英特尔晶体管的图像——平面 FET、FinFET 和Ribbon FET。

CFET 晶体管将 n 型和 pMOS 器件堆叠在一起以实现更高的密度。目前正在研究两种类型的 CFET——单片式和顺序式。上图右侧的四个器件详细介绍了各种建议的 CFET 设计。目前,尚不清楚英特尔将采用哪种类型的设计,或者是否会设计另一种类型的实现。鉴于 imec 在其路线图上没有 CFET,直到芯片在 2032 年的时间范围内缩小到 5 埃左右,我们可能需要一段时间才能找到答案。

也就是说,不能保证英特尔会在那个时间段内瞄准 CFET:有趣的是,英特尔的幻灯片展示了其下一代 GAA 纳米片晶体管 (RibbonFET),然后直接跳到 CFET,省略了大多数人认为将是介于纳米片和 CFET 之间。您还可以在上面的幻灯片中看到这种类型的晶体管——它是左数第二个。

鉴于英特尔的形象不是很详细,该公司可能还计划在转向 CFET 之前使用 forksheet晶体管,但它尚未选择分享细节。我们正在跟进英特尔,看看是否可以了解更多细节。

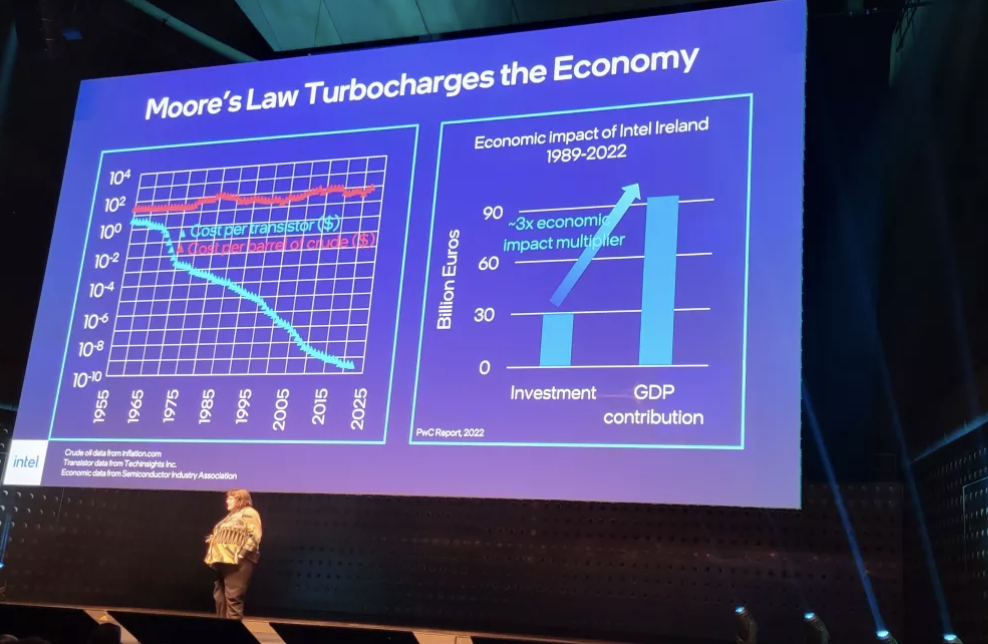

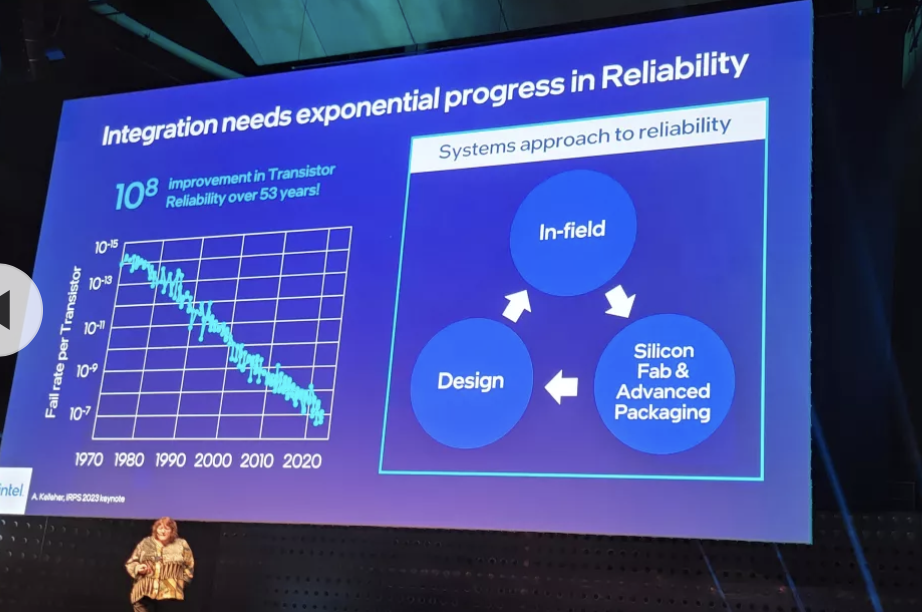

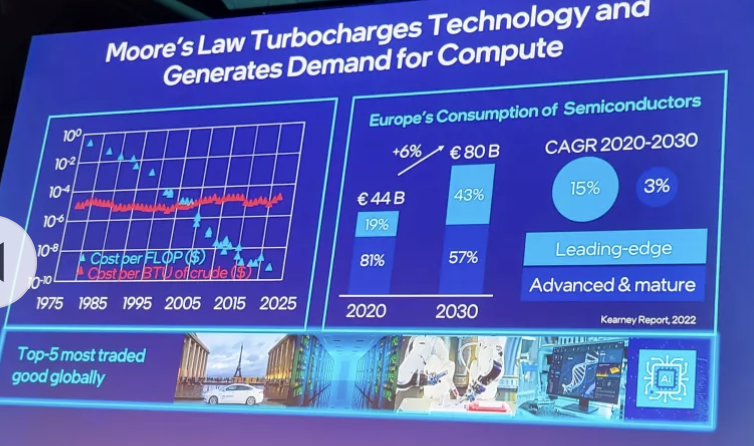

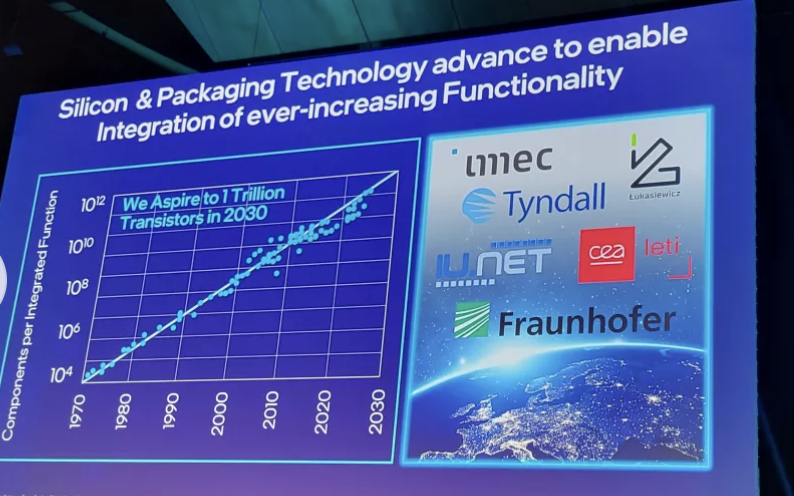

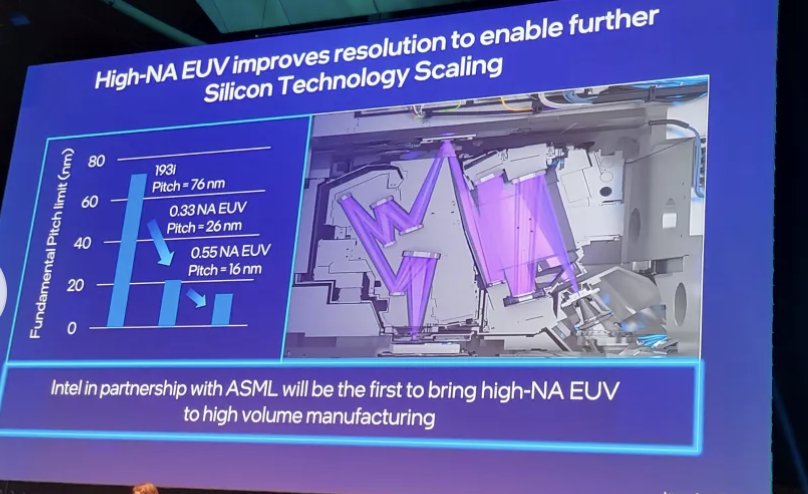

以下是 Kelleher 演示文稿中的其余幻灯片,供您细读。Kelleher 涵盖了广泛的主题,包括随着时间的推移每个晶体管支付的成本下降、晶体管的可靠性随着时间的推移而增加、日益复杂的封装过程以及转向系统技术协同优化方法的重要性为英特尔的设计工作。

Kelleher 的演讲是在 imec 的 ITF 世界会议上进行的,她通过回忆自己在 imec 的历史开始了她的演讲——近 30 年前,她作为一名学生首次在 imec 工作,最终在这家研究巨头工作了两年。在过去的 30 年里,英特尔还与 imec 建立了长期合作关系,这种合作一直持续到今天。

上一篇:台湾半导体业未见复苏迹象

下一篇:英国宣布87亿元半导体投资计划 侧重研究与设计

推荐阅读最新更新时间:2024-10-24 14:42

- 英特尔中国正式发布2023-2024企业社会责任报告

- 贸泽电子与Analog Devices联手推出新电子书

- AMD 推出第二代 Versal Premium 系列:FPGA 行业首发支持 CXL 3.1 和 PCIe Gen 6

- SEMI:2024Q3 全球硅晶圆出货面积同比增长 6.8%、环比增长 5.9%

- 台积电5nm和3nm供应达到"100%利用率" 显示其对市场的主导地位

- LG Display 成功开发出全球首款可扩展 50% 的可拉伸显示屏

- 英飞凌2024财年第四季度营收和利润均有增长; 2025财年市场疲软,预期有所降低

- 光刻胶巨头 JSR 韩国 EUV 用 MOR 光刻胶生产基地开建,预计 2026 年投产

- Imagination DXS GPU 已获得ASIL-B官方认证

- DN05075/D,用于 15W LED 的降压-升压转换器设计说明

- LMV324DTBR2G 运算放大器电压基准的典型应用电路

- DC2121A,使用 LTM4634 三路输出 5A/5A/4A 降压型 DC/DC 模块稳压器的演示板

- ESP32DUINO

- DER-114 - 21 W 备用电源

- LTC4219-12 演示板、12V、5A 集成热插拔控制器

- 网络钟表

- 在 SDM 接口、模拟电压输出的 5V 电源中嵌入 SHT2xS 应用说明

- LT1009 系列的典型应用 - 2.5V 基准

- 4012-LCDK1W-434、Si4012/Si4355 EZRadio 单向链路开发套件 434 MHz

深入理解FFmpeg (刘歧;赵军;杜金房;赵文杰;宋韶颍)

深入理解FFmpeg (刘歧;赵军;杜金房;赵文杰;宋韶颍) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号