在很久以前,EDA是一个很“不起眼”的行业,自从国产替代概念兴起,越来越多人意识到这块基石的重要性。如果没有EDA,整个芯片行业就会停摆。

2023年是国产EDA爆发的一年,现如今已有上百家国产EDA厂商。那么从技术上来讲,数字全流程和AI(人工智能)无疑是近几年的热词。

ICCAD 2023上,深圳鸿芯微纳技术有限公司CTO、联合创始人王宇成分享了鸿芯微纳SoC EDA平台的发展情况以及对国产EDA发展的看法。

已实现“数字全流程”最主要几步

“我们成立于2018年,2019年开始正式运营,至今已差不多四年,我们的产品方向是搭建国产数字EDA的全流程工具,虽然目前还没有完全覆盖全流程,但它已经达成了工具中最主要的几步,将来会通过自主研发、技术引进、合作开发等模式,逐渐补全产品线,形成真正的全流程部署。”王宇成这样介绍到鸿芯微纳。

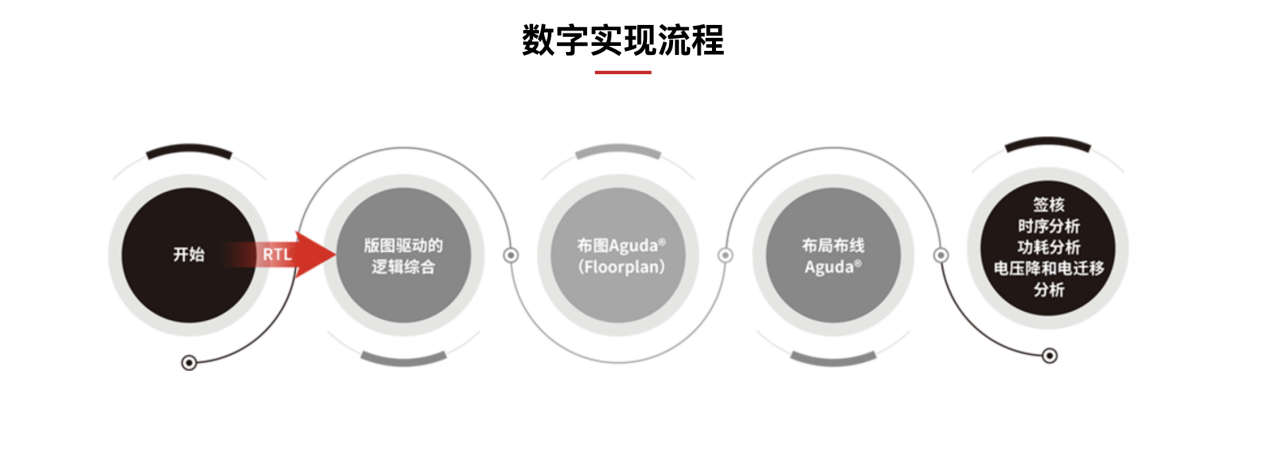

根据王宇成的介绍,鸿芯微纳的工具开发分成几个重要步骤。

第一步,先初步实现国产替代,事实上国外现有工具已经演变十多年甚至二十多年,我们用三、四年短时间开发的工具实现差异化很难。

第二步,新的EDA工具开拓市场, 从来就是充满了困难和阻力。 对于国内新生的EDA产品, 大多数设计公司仍然处在早期探索阶段。 评估工具是很复杂的过程, 决定采购, 直至推广使用更是充满了挑战。国外供应商也是大量的研发投入而不是止步不前。 国产EDA的成功, 仅仅迈开了一小步,从点工具迈向工具链。

第三步,实现基本的全流程之后,就要补全整个工具,达到真正的数字全流程。鸿芯微纳是国内第一且唯一实现数字后端全流程工具链的本土EDA企业。

“王宇成强调,作为国产EDA工具提供方,只有把数字全流程中每个环节都串在一起,才能形成生态,在生态的基础上才能不断超越国际,形成真正的国产替代。

四个SoC设计关键工具

SoC是现代信息技术的基石,也是数字IC公司的核心竞争力,强大的数字SoC实现工具能够帮助设计公司高效率地实现性能强大的产品,并缩短上市时间,减少开发人力投入。鸿芯微纳的“鸿图SoC设计实现平台”能够帮助中国IC设计公司打造数字领域全球竞争力。

根据鸿芯微纳官方信息显示,鸿芯微纳最主要几步和产品涵盖四个方面:Aguda®(以布线为中心的布局布线工具)、RocSyn®(版图驱动的逻辑综合工具)、ChimeTime®(静态时序签核工具)、HesVesPower®(功耗签核工具)。

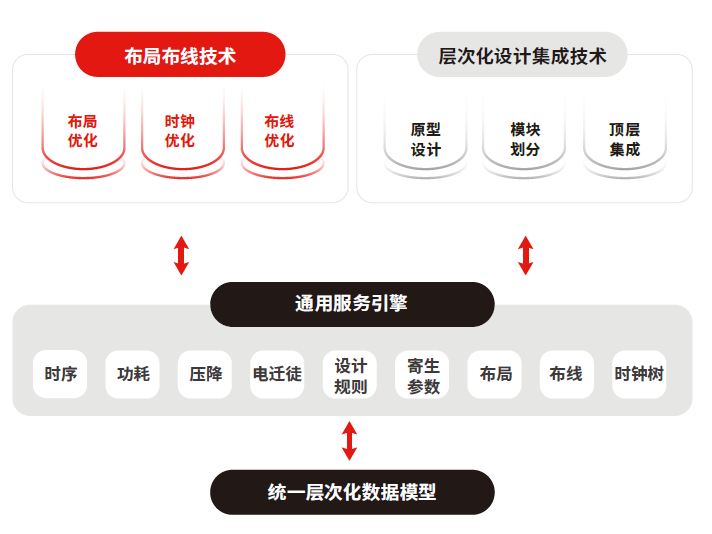

Aguda®是整个流程中非常关键的工具,与其它三款工具形成流程一致性。它是一款完整的数字芯片物理实现工具,提供从门级网表输入到GDS II 输出的电子自动化设计流程,涵盖从布图、电源网络设计、布局优化、时钟树综合、时钟树优化、布线优化和顶层集成的全部技术。其功能完备的模块级布局布线,内嵌强大的分析引擎为布局布线的每个技术环节提供实现和优化。支持业界标准的输入和输出数据格式,支持完整的自上而下层次化顶层设计需求,提供友好的工具界面和脚本支持。

它拥有五大特点:一是时序收敛速度较传统工具提高2倍以上,可使设计时间缩短一半以上,人力投入减少一半以上;二是超过75%的时序改善,超过2%的面积改善或绕线布通率,平均减少20%的运行时间;三是易于使用及专业技术支持;四是解决方案已在业界头部客户得到验证;五是广受客户赞誉。

RocSyn®是一款功能齐全的逻辑综合工具,实现从硬件描述语言(HDL)输入到门级网表输出的电子自动化设计流程,涵盖从HDL编译,高层次优化,低功耗综合,技术映射,时序驱动优化和版图驱动优化的全部技术。支持业界标准的输入和输出数据格式,内含多层次,多方位的优化引擎,提供多样化的报告输出,提供友好的工具界面和脚本支持。

它能够处理各个工艺节点下的超大规模数字集成电路设计,性能指标(延时,面积,功耗,即PPA)达到国内领先和国际一流水平。其优势是综合流程组件完全自主可控、拥有强大的高层次优化技术、精确的时序分析引擎、重映射和重优化技术、与布局布线工具紧密结合、灵活,高效的Tcl和C应用程序接口。

ChimeTime®是集静态时序分析、串扰延时和信号完整性分析等功能于一体的静态时序签核工具,提供达到SPICE精度的高性能时序签核解决方案。其强大的分布式分析引擎支持上亿规模单元的大规模设计,提供快速且准确的时序、信号完整性、多角多模(MCMM)等分析结果。支持业界标准的输入和输出数据格式,支持先进的片上偏差分析,支持层次化分析以及快速PBA分析能力。

值得一提的是,它提供友好的工具界面和脚本支持,贴近用户使用习惯,帮助设计人员快速精准定位设计缺陷,提高设计迭代效率。目前,ChimeTime®解决方案已在业界头部客户得到验证。

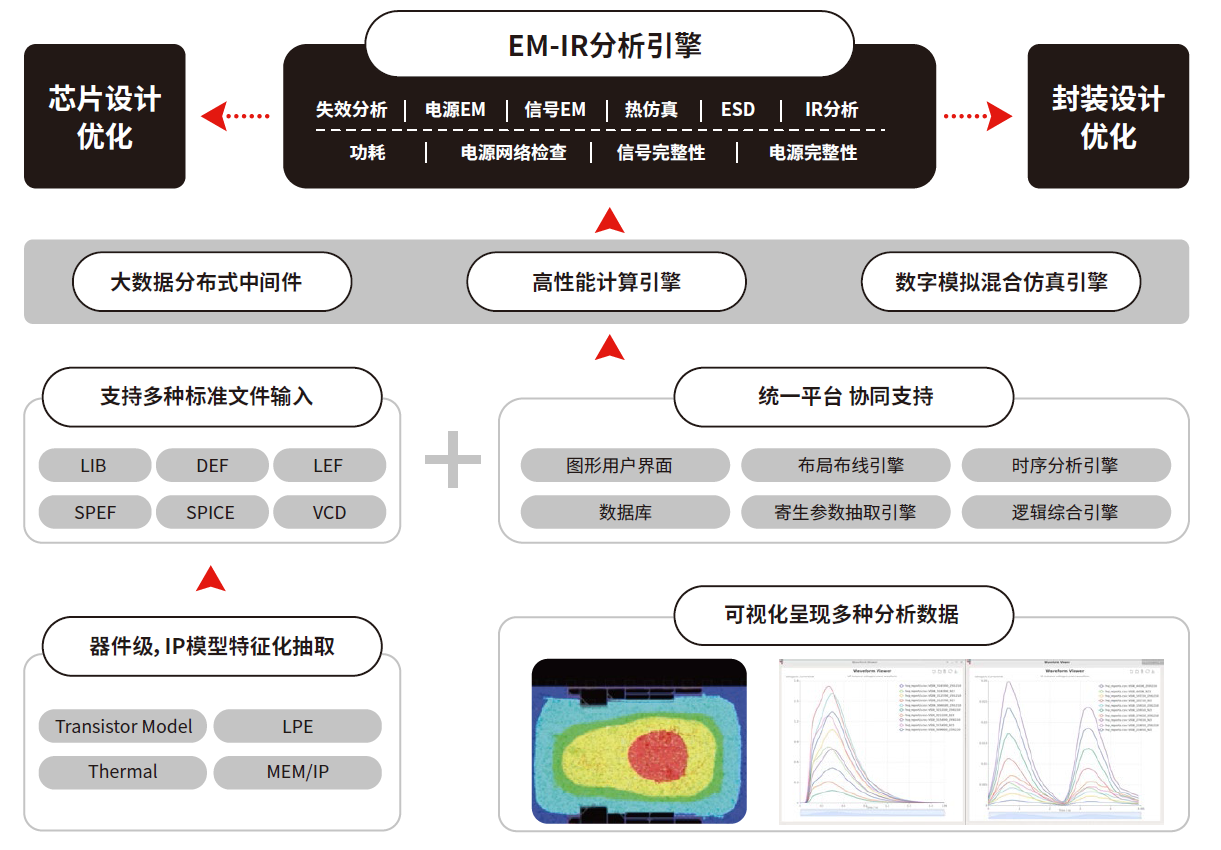

HesVesPower®是一款数字芯片系统的功耗签核工具,其分析结果用于优化芯片运行的稳定性和使用寿命,也可以用于电源信号方面的系统集成需求。功能涵盖功耗分析,电源网络阻抗分析,压降分析,电迁移分析,带封装分析,功耗模型抽取,信号模型抽取,特征化建模,ESD分析等方面。

具体来说,主流功能“功耗压降电迁移分析”经过PR流片验证,专利支持,功耗,压降,电迁移精度与主流工具一致性超过99.5%;核心功能“高性能计算引擎”支持十亿级别自由度的矩阵求解,支持分布式计算;扩展功能“从器件到系统级的功耗签核流程”器件特征化精度与SPICE误差小于3%,支持系统级压降分析和功耗建模,支持数字门级仿真和模拟时域频域仿真。

AI与EDA的inside与outside

今年是AI发展里程碑式的一年,ChatGPT这种AIGC(生成式AI)工具的问世,让越来越多人关注到AI技术,也代表着AI开始进入应用爆发期。那么AI与EDA能够碰撞出什么火花?

王宇成表示,实际上传统EDA应用AI并不多。在2019年左右,国外工具开始尝试在EDA中应用AI技术并开始建立专门的AI团队。

目前,鸿芯微纳几年的国产替代开发任务已经基本完成,现在更加关注如何形成更强的竞争力,AI就是不可或缺的技术之一。

按照鸿芯微纳的理解,EDA在AI领域分为两个方向,一是AI inside,即利用AI和ML(机器学习)加强EDA传统算法,可以让工具跑得更快,甚至让性能提升一个量级,鸿芯微纳在这方面已有一些研究与积累,目前处于扩大应用与深度探索的阶段;二是AI outside,比较明显的就是有一些设计空间优化的新产品问世,它们会在调参上辅助工程师进行优化,找到最好的那组参数。目前这方面的产品研发主要基于成熟的工具展开。目前鸿芯微纳经过三年的开发,主要产品已经非常成熟,计划今年年底进行一些尝试,如果有相应成果,可能后续步子会迈得更大。

“像现在Open AI的ChatGPT这种大语言模型可能带来一个更大的效果,我们希望EDA工具方不是提供一个工具给专家去使用,而是提供一个解决方案,对于应用企业来说,他不需要顾虑,就能达到他想要的效果。”王宇成这样强调。

国产EDA这三五年的发展有了一些积累,也逐渐形成一些规模化趋势,作为立足本土的EDA公司, 鸿芯微纳相信我们比国外同行更能敏捷快速开发出更适用国内设计客户需求的,有竞争力和差异化的产品和技术。王宇成在分享中这样总结道。

上一篇:芯原股份戴伟民:Chiplet会在AIGC和智慧驾驶领域率先落地

下一篇:C语言,如何颠覆芯片设计流程?

推荐阅读最新更新时间:2024-11-16 20:14

- 意法半导体披露 2027-2028 年财务模型及2030年目标实现路径

- 创实技术electronica 2024首秀:加速国内分销商海外拓展之路

- 欧洲三大芯片巨头,重新审视供应链

- 一场IC设计业盛宴!10场论坛 200位演讲嘉宾,300+展商亮相2万平米专业展会!

- 富昌电子于杭州举办技术日活动,聚焦新能源“芯”机遇

- 消息称铠侠最快明天获上市批准,市值有望达 7500 亿日元

- 美国政府敲定对格芯 15 亿美元《CHIPS》法案补贴,支持后者提升在美产能

- SK 海力士宣布量产全球最高的 321 层 1Tb TLC 4D NAND 闪存,计划 2025 上半年对外出货

- 三星电子 NRD-K 半导体研发综合体进机,将导入 ASML High NA EUV 光刻设备

- ADA4075-2ARZ-RL 平衡线路接收器运算放大器的典型应用电路

- FRDM-KE15Z: 面向Kinetis® KE1xMCU的Freedom开发平台

- st-linkv3mods-转接板

- 开源150M示波器差分探头

- EVAL-ADuC7026QSPZ,用于评估 ADuC7026 ARM7 MCU 微转换器的 QuickStart Plus 开发系统

- 涂鸦BT3L模组四路通断器

- LT3091EFE 产生极低输出电压的典型应用

- DK-DEV-3SL150NES,Stratix III 开发板为低功耗开发和原型设计提供硬件平台

- 电流电压表

- LT1172CQ、1.25A 高效恒流充电器的典型应用

电工学 中 电子技术 第2版 (杨世彦主编(哈尔滨工业大学电工学教研室))

电工学 中 电子技术 第2版 (杨世彦主编(哈尔滨工业大学电工学教研室)) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号