LUCT是什么?

第一层时钟树和第二层时钟树

时钟树设计及其设计方式是引起系统芯片性能差异的主要原因。

从历史角度看,ASIC时钟树设计人员利用商用自动化工具设计时钟树,以确保执行时间等性能取得预期结果,但是,这种方法的时钟偏差和插入延时等性能却不尽人意,另外,高复杂性、频率和尺寸设计使得传统方法完全没有可行性。

低不确定性时钟树[LUCT]设计及算法与在系统芯片上实现的第一层时钟树的物理定义有关,能够让设计人员克服传统设计方法的所有低效率问题。

从顶层的根时钟网络(通常是PLL输出)到中层时钟网络,LUCT是一个高质量的负载均衡的时钟树,其目标是将时钟信号从中央锁相环PLL送到芯片的大部分区域,详情参见参考文献[1]。该文献详细介绍了低不确定性时钟树[LUCT]方法和架构,概括了从规格定义到单元布局和时钟合成的全部相关设计流程。

按照参考文献[2]的定义,这种时钟分配方法属于结构化时钟树。文献[2]还概括了现有的不同的时钟设计方式。从时钟源到寄存器,整个时钟树由第一层时钟树和第二层(或本地)时钟树组成。商用EDA工具需要实现本地时钟树。

LuctGenKit是意法半导体数字ASIC产品部的设计方法小组研发的时钟设计工具,可完成LUCT架构的物理实现过程。

LUCT工具主要特性

LuCT时钟合成工具提供LuCT方法中的所有重要特性:

o 均衡的时钟树

- 长度均等和主动负载匹配

- 障碍感知

- 使用低电阻的高层金属层传输信号

- 屏蔽和寄生匹配

o 增强型订制单元库,满足各种信号强度需求

o 支持多种制造工艺,例如,32/28bulk,28fdsoi等

o 模块布局,障碍布局与避障

o 与布局布线环境完全集成

LuCT设计流程

LuCTgenKit设计流程分为四个阶段,本文下面章节将给予详细讨论。该工具可简化复杂ASIC设计,在有多个工程师参与整个项目的物理实现的设计环境中效果特别明显。在一个典型设计组织内,物理实现的初始阶段是数据库准备和规格定义,最后阶段的工作主要是由专门的LuCT工程师来完成。一旦数据库准备和规格定义都完成后,仅一名LuCT设计工程师在一个工作日内即可完成整个顶层时钟树(可能不只一个时钟树)的实现和定案工作。

LuCT tool 数据库准备

数据库准备包括必要的设计检查、布局规划合理性验证、读取电源网格形状属性和布局布线工具。其中,布局布线工具用于连接特殊的增强型时钟库,并通过LuCT创建算法确保时钟库布局连贯。本阶段还是使结构化时钟树利用现有技术取得最高性能的关键步骤,特别是在降低电压降和抗串扰方面。

LuCT tool LuCT规格定义

每一个时钟合成,都需要在该工具内输入下面信息:

o 技术节点

o 主要时钟树起点(PLL)

- X 和Y坐标

o 主要时钟树终点

- 每个叶子上的X和Y坐标

o 频率范围

o 工艺-电压-温度角

o 时钟单元参数选择

设计人员可通过图形用户界面输入所需的全部数据和设计方式。

LuCT tool 执行: 创建LuCT

低不确定性时钟树合成自动化工具捆绑下列对象:

- 设计规格

- 布局规划信息(包括布局障碍和布线障碍)

- 电源网格

- 设计和布局规则

- 网表

- 布局

- 图形用户界面

- 报告

- 定案

LuCT工具通过意法半导体独有的算法生成时钟树拓扑。该算法基于均衡的路径长度和等长同质布线。芯片布局规划建模和初始化以及路径计算需要Lemon C++图形函数库[4]。时钟树创建过程包含下列步骤:

o 网格生成: 在从布局规划读取数据后,生成障碍模型和电源网格形状模型。从这些模型开始计算一个代表LuCT算法定义的布局布线间距的点集合(网格)。

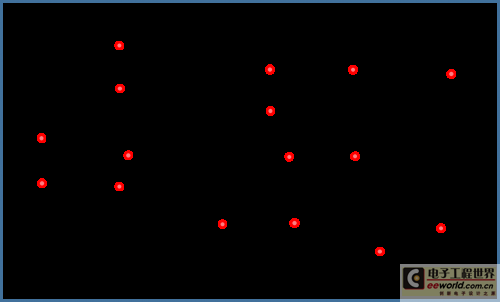

o 构建二进制树:使用意法半导体独有算法将叶子分组,每组一对。通过计算长度均等的包含避障点的路径和合并点(即该路径中间的一点)的方式将每对树叶合并。通过这种方法按照递归方式合并新的叶子(合并点),直到只剩下一个点(树根)为止,详见图4到图6。

o 插入时钟驱动器和布线:插入时钟驱动器和优化布线是采用一个自下向上的方法,分别考虑障碍布局和障碍布线。[page]

图7 :采用LuCT工具的设计流程

一旦生成时钟树结构,只要在布局布线CAD工具内使用脚本程序即可实现布局。对于多个并行时钟驱动器的高性能布线/走线、通孔布局和电源噪声感知布局,取得布局配置需要使用自定义规则。

通过修改几个对二进制树架构和创建有很大影响的参数,可以优调算法。

下面是一些参数示例:

o 叶子对生成:可自动或人工生成

o 路径距离计算:可以是纯Manhattan方式或能够感知障碍

o 弯折最小化:为布线网络选择适合的吸引力

o 通过在每个布线/合并阶段全局重映射中心,吸引合并区向现阶段的中心转移

o 时钟树性能指标:障碍强度、时钟偏差/插入延时性能与障碍的均衡性、时钟拥堵。

LuCT 工具 示例和结果

图8所示是按照上面讨论的方法使用LuCTgenKit设计 28FDSOI芯片的时钟树。1GHz时钟信号从时钟源分配到8个树叶,避绕障碍,平衡时钟偏差,查觉障碍。图9所示当连接高层叶子对时如何执行等长计算。

这个示例的主要结论是,按照基延迟(base delay)计算,时钟偏差是非常有限的,不过,出现大量的不常见路径。

上一篇:基于CC1110无线单片机的机器鱼控制系统设计

下一篇:智能控制令照明更加节能

推荐阅读最新更新时间:2024-03-16 13:46

设计资源 培训 开发板 精华推荐

- 2024年Automechanika Shanghai海量同期活动刷新历届记录,汇聚行业智慧,共谋未来发展

- 企业文化分享 如何培养稀缺的硅IP专业人员?SmartDV开启的个人成长与团队协作之旅

- 恩智浦发布首个超宽带无线电池管理系统解决方案

- 北交大本科生探秘泰克先进半导体开放实验室,亲历前沿高科技魅力

- 新帅上任:杜德森博士(Dr. Torsten Derr)将于2025年1月1日出任肖特集团首席执行官

- 边缘 AI 如何提升日常体验

- 苹果要首发!台积电宣布2nm已准备就绪

- AMD有望用上全新芯片堆叠技术:延迟大幅减少、性能显著提升

- 宁德时代发布10月战报

- 2024年10月电池行业:增长势头不减!

- 有奖直播|TI MSP430™民用超声波水表开发指南及其智能模拟组合模块在传感器检测中的应用

- 富士通白皮书有奖下载|FRAM高性能存储器优化车载电子系统

- 快速获取TI 工业电机驱动资源 答题赢好礼

- 【泰克注册观看有礼】 PCI-SIG 前主席解析:PCI Express5.0测试方案和测量挑战

- 阅读并了解是德科技 Power Supply 精彩专题,参与答题赢好礼!

- 春暖花开,我为TI C2000 LaunchPad“画”外围!

- 抢鲜体验| 两款GD RISC-V开发板

- TI“无线”风光可穿戴现场培训直播,诚邀参与,预注册赢好礼

- 【DIY数控电源】入围方案及后续活动安排!

- 领跑2021,你准备好了么?领取下载积分,点燃学习小宇宙!

ST意法半导体飞行时间(TOF)传感器在扫地机器人的应用

ST意法半导体飞行时间(TOF)传感器在扫地机器人的应用 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号