理解STM32的时钟是我们应用定时器等等的基础,根据最近的工作总结一下:

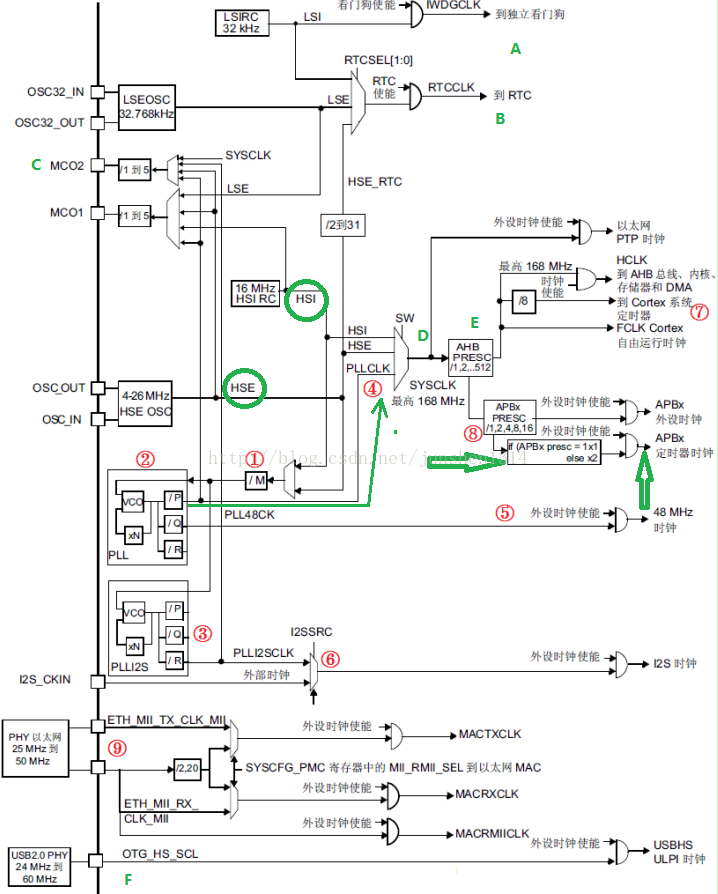

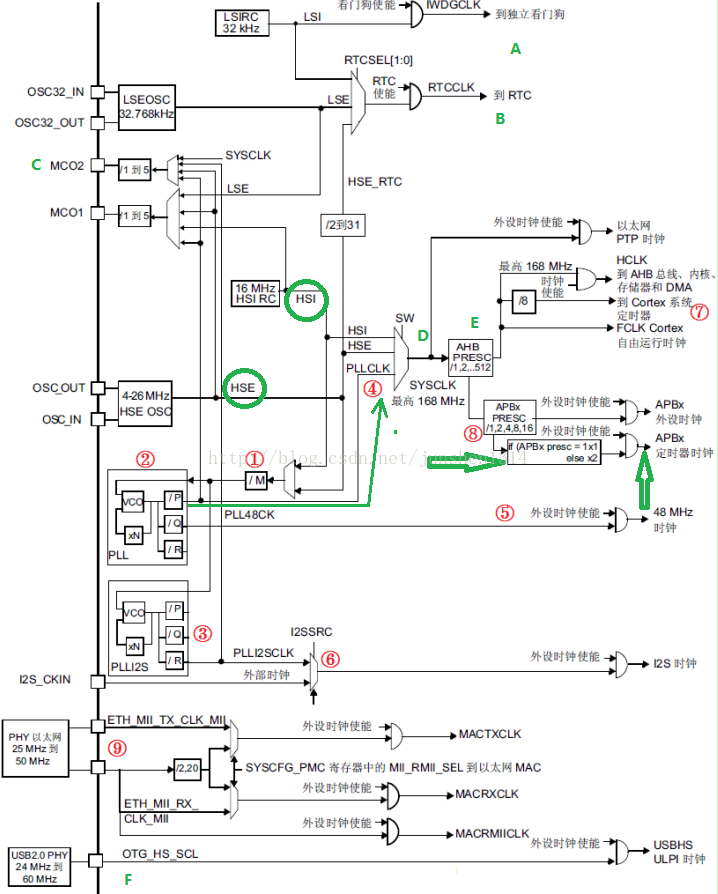

下面是STM32的时钟树:

1.首先注意的的是图中画绿色圈圈的两个,HSE和HSI分别表示外部时钟和内部时钟,其中HSE 是是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,HSE 也可以直接做为系统时钟或者 PLL 输入(从红圈4处可以看出),频率范围为 4MHz~26MHz。STM32默认为25Mhz,像原子的板子就是8Mhz的,所以移植时一定要格外注意。

2.注意红圈2代表的部分,这里是主锁相环倍频输出,用于产生系统需要的高速时钟信号,如图绿色箭头所示(STM32还有一个副锁相环,如红圈3)

主 PLL 时钟的时钟源要先经过一个分频系数为 M 的分频器,然后经过倍频系数为 N 的倍频器出来之后的时候还需要经过一个分频系数为 P(第一个输出 PLLP)或者 Q(第二个输出 PLLQ)的分频器分频之后,最后才生成最终的主 PLL 时钟。例如我们的外部晶振选择 8MHz。同时我们设置相应的分频器 M=8,倍频器倍频系数 N=336,分频器分频系数 P=2,那么主 PLL 生成的第一个输出高速时钟 PLLP 为:PLL=8MHz * N/ (M*P)=8MHz* 336 /(8*2) = 168MHz(来源:正点原子)

3.区分APB1和APB2

如红圈8表示的位置,STM32F4 很多外设的时钟来源,即两个总线桥: APB1 和 APB2,其中 APB1是低速总线(最高 42Mhz),APB2 是高速总线(最高 84Mhz)。另外定时器部分,如果所在总线( APB1/APB2)的分频系数为 1,那么就不倍频,如果不为 1(比如 2/4/8/16),那么就会 2 倍频( Fabpx*2)后,作为定时器时钟输入。

简单点说,举个APB1的例子,系统时钟是168Mhz,APB1分频系数为4(system_stm32f4xx.c配置),则APB1速度为42Mhz,但是挂靠在在该总线上的定时器,由于分频系数4而不是1,因此定时器输入频率为42Mhz x 2 =84 Mhz

关键字:STM32F4xx 时钟

引用地址:

STM32F4xx时钟理解

推荐阅读最新更新时间:2024-03-16 16:07

STM8 时钟修改

系统功能 对STM8的时钟修改,并用LED进行显示,观察LED的闪烁速度是否有变化。 硬件设计 LED控制电路原理图 软件设计 /********************************************************************* 微 雪 电 子 WaveShare http://www.waveShare.net 目标系统: 基于STM8单片机 应用软件: Cosmic CxSTM8 说 明: 若用于商业用途,请保留此段文字或注明代码来源 深 圳 市 微 雪 电 子 有 限 公 司 保 留 所 有 的 版 权 *******************************

[单片机]

分析器检测二极管的反向恢复行为

测试 二极管 的 反向恢复 特性通常需要复杂的测试设备。你必须能够建立正向传导条件、阻断状态和两者之间的转换。你还需要一种能够从结果的微波中提取特征的手段。总之,一个专家需要处理这个复杂的工作而不仅仅是例行公事。这个事实说明了为什么工程师们普遍倾向于依靠公布的数据。 你自己来检查反向恢复时间是有利的,不过,前提是要做的测试是简单明了的。这种格局将使你可以在相同的条件和试验装置下比较来自不同厂家的设备并且测试没有这种规格的设备,如衬底二极管驱动集成电路、齐纳二极管、整流标准。(由于测试参数联合的个数,一个数据的直接对比是基本不可能的)。注意使反向恢复时间变短不一定很好。慢速的二极管可以同样有用。它们可以产生小死亡时间、提

[测试测量]

多通道系统宽带宽信号测量及时钟架构设计方案

下一代航天和国防以及测试和测量系统带宽从10s到100s MHz横跨到GHz的瞬时带宽。相控阵雷达、5G无线测试系统、电子战以及数字示波器的发展趋势正在推动业内向更高带宽发展,并且大幅增加系统中的通道数量。 这些趋势使包括数据转换器、时钟和电源等组件的信号链设计变得复杂化。选择合适的数据转换器、同步多个通道以及优化电源,对于在多个通道上实现必要的带宽至关重要。 选择适合的数据转换器 每个系统架构都是从对系统性能影响最大的器件开始;在宽带系统中,最先开始的就是数据转换器。选择哪一款数据转换器取决于您对以下问题的回答: 您是否会使用零中频(IF)/复数混频器架构(如图1所示)? ● 优势:模数转换器(ADC)的输入带宽和采样率

[测试测量]

MSP430F5529 默认时钟频率(1.05MHz)的来源探究

相信很多小伙伴跟我一样好奇 MSP430FF5529的 初始时钟是哪里来的,是多少 接下来我和大家一起分析一下! 首先我认为比较可疑的是 那些默认的参数,一些Reset值不是0的参数 十分的可疑,我们着重的看看他想表达什么意思 我查找UCSCTL这个寄存器的第一个值是UCSCTL1 的DCOSEL位 这一位是2 在芯片的Datesheet里面我找到了这个,貌似是没什么太大的用处。 接下来一个比较让人感兴趣的寄存器就是这个 FLLD = 1 这个好理解 接下来 有意思的来了 : FLLN = 0x1F = 31 这是书册里面 很重要的一个公式! 暂且先不说作用,我们现在先追溯一下我们的时钟是从哪里来的

[单片机]

信号链基础知识:谁是音频时钟的“老板”

过去,我们在讨论音频话题时,偶尔会提及 I2S。我在以前的一些文章中提到过 I2S,其他人在做音频研究时也都会提到它。简而言之,它是一种将立体声数据从一端传输至另一端的同步方法。 大多数人认为 I2S 有三种信号: 1.数据:输入或者输出数据 2.位时钟 (Bitclock,BCK):确立数据流中两个相邻位之间边界的信号 3.左/右时钟 (LRCK)/字时钟 (Wordclock):一个在采样速率下运行、占空比为 50% 的慢时钟,它确立数据流中两条相邻通道(左和右)之间的边界。 I2S的幕后英雄是主时钟 (MCK),也称作系统时钟 (SCK),它常常被数字信号处理器 (DSP) 程序员和其他处理器爱好者

[模拟电子]

数字信号处理(DSP )系统测试和调试2

JTAG 技术简介 收缩技术(shrinking technology)的一个劣势在于,测试小型器件的复杂程度急剧升高。当电路板面积较大时,板的测试是通过采用钉床等技术来进行的。这种技术采用小型弹簧式测试探针来和板底部的焊盘进行连接。这种测试方案是定制的,不仅成本太高,而且效率低下,而且在设计完成之前很多测试都无法进行。 随着电路板面积的缩小,以及表面贴装技术的改进,钉床测试的问题不断增多。 而且,如果一块电路板两面都安插了器件,根本无法留下任何可使电路板安放到测试器件上的依附点。 边界扫描(Boundary scan) 1985 年,一个欧洲电子公司组织联合起来,试图寻找能够解决这些问题的方案。该组

[嵌入式]

高密度 低耗能,惠普取得FPGA技术新突破

惠普近日宣布在FPGA技术上取得了突破,能把现场可编程门阵列(FPGA)的密度较提高8倍,而且能耗还更低。这一技术要求将一个纳米级纵横交换结构置于传统CMOS制程的顶层,惠普将这一技术称为“现场可编程纳米线互联”技术,是当前的FPGA技术的一种变体。 研究人员展示了一款采用15纳米宽交叉线和45纳米半间距CMOS的芯片模型,并表示这款芯片将于2010年问世。此外,惠普还展示了一款采用4.5纳米宽交叉线的模型,而这一芯片则将于2020年问世。这个结合了45纳米CMOS的4.5纳米交叉结构将可以用来生产大小只有纯CMOS方案45纳米FPGA的4%的混合式FPGA。尽管时钟速度可能会下降,但是每次计算的能耗也会下降。 在FPNI方案

[焦点新闻]

TMS320C5402 在电视数字传输复用器中的应用

引言 随着信息技术的发展,电视信号的数字化编码、数字化存储、数字化处理已经越来越广泛。新开发的数字有限电视广播系统主要包括MPEG-2编码器、数字传输复用器、数字调制器以及机顶盒。复用器是该系统的重要组成部分,完成对多路符合MPEG-2系统层标准ITU-TREC.H.222.1|ISO/IEC13818-1的TS流(Transport Stream)的复用,经过64 QAM调制后,以便在1路6MHx的带宽中传送多路数字化节目。考虑到处理的实时性,我们使用美德州仪器公司(TI)的TMS320C5402(简称C5402)DSP作为主控芯片。本文首先介绍TS流的结构、C5402芯片、复有器的组成,然后重点介绍该芯片在复用器的应用

[手机便携]

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号