分三部分说明:

①2440地址空间

②内存与芯片硬件连接

③存储控制器寄存器

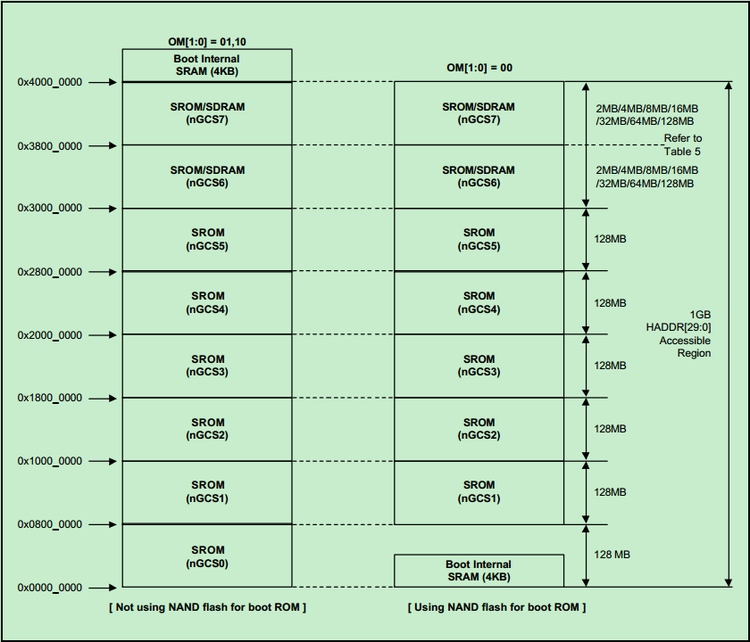

S3C2440地址空间

S3C2440对外提供27根地址线,单靠芯片上的27根引脚,它只能访问128M的外设空间。

为了扩大外设的访问范围,S3c2440芯片又提供了8个片选信号nGCS0~nGCS7,对应Bank0-Bank7。当某个片选信号nGCSx有效时,则可以通过27根地址线去访问对应这个片选的128MB空间。当访问BANKx的地址空间时,nGCSx引脚输出低电平来选中外接设备。由于有8个片选,所以2440芯片能访问的外设空间总为8*128MB=1GB.而1G(0x40000000)以上的空间,则安排给了2440内部的寄存器,访问这些内部的寄存器,则是通过32位的处理器内部总线来完成的。

S3C2440外设地址空间图:

一共8个片选,其中nGCS6,nGCS7为内存。

内存与芯片的硬件连接

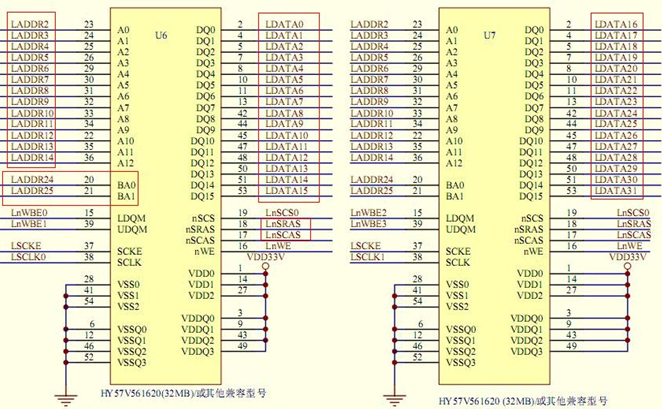

BANK0-BANK5的连接方式类似,BANK6连接SDRAM时复杂一些,SDRAM内部是一个存储阵列,指定一个行,再指定一个列,就可以准确找到所需要的单元格,而SDRAM有4个逻辑表格(L-BANK),那么SDRAM的访问步骤为:

1)CPU发出片选信号nSCS0(与nGCS6是同一引脚)有效,选中SDRAM芯片

2)SDRAM有4个L-BANK,需要两个地址信号来选中其中一个,即ADDR24、ADDR25,如下图

3)对被选中的芯片进行同一的行/列(存储单元)寻址

根据SDRAM芯片的列地址线数目设置CPU相关寄存器后,CPU会从32位地址中自动分出L-BANK选择信号、行地址信号、列地址信号,然后先后发出行地址信号、列地址信号。L-BANK选择信号在发出行地址信号的同时发出,并维持到列地址信号结束。

如上图:行地址、列地址公用地址线ADDR2-ADDR14,使用nSRAS(R=Row)、nSCAS(C=Column)两个信号来区分它们,当nSRAS信号有效时,ADDR2-ADDR14发出的是行地址,对应地址空间bit[23:11],当nSCAS信号有效时,ADDR2-ADDR14发出的是列地址,对应地址空间bit[10:2]。

4)找到存储单元后,被选中的芯片就要进行统一的数据传输。

开发板使用两片16bit的SDRAM芯片并联形成32位的位宽,与CPU的32根数据线DATA0-DATA31相连,BANK6的起始地址位0x30000000

存储控制器寄存器

存储控制器共有13个寄存器,BANK0-BANK5只需要设置BWSCON和BANKCONx两个寄存器,BANK6、BANK7外接SDRAM时,还要设置REFRESH,BANKSIZE,MRSRB6,MRSRB7,等4个寄存器,下面分别说明

1)位宽和等待控制寄存器BWSCON

BWSCON中每四位控制一个BANK,最高4位对应BANK7、接下来4位对应BANK6,依次类推。

STx:启动/禁止SDRAM的数据掩码引脚

WSx:是否使用存储器的WAIT信号

DWx:设置对应BANK的位宽,0b00对应8位,0b01对应16位,0b10对应32位,0b11表示保留

比较特殊的是BANK0,它没事ST0和WS0,DW0只读,由硬件跳线决定,0b01表示16位,0b10表示32位,BANK0只支持16、32两种位宽

所以可以确定BWSCON寄存器值为:0x22000000

2)BANK控制寄存器BANKCONx(x为0-5)

这些寄存器用来控制BANK0-BANK5外接设备的访问时序,使用默认0x0700即可

3)BANK控制寄存器BANKCONx(x为6-7)

MT[16:15]:设置BANK外接ROM/SRAM还是SDRAM,00=ROM/SRAM,01=保留,10=保留,11=SDRAM

MT=0b00时,与BANKCON0-BANKCON5类似

MT=0b11时,

Trcd[3:2]:RAS to CAS delay,从时序图可知为2 clocks,所以设为0b00

SCAN[1:0]:SDRAM的列地址数,本开发板使用的SDRAM列地址数为9,0b00=8位,0b01=9位,0b10=10位

所以本开发板,BANKCON6/7均设为0x00018001

4)刷新控制寄存器REFRESH

REFEN[23]: 0=禁止SDRAM的刷新功能,1=开启SDRAM的刷新功能

TREFMD[22]: SDRAM的刷新模式,0=CBR/Auto Refresh,1=SelfRefresh

Trp[21:20]: SDRAM RAS预充电时间 00=2 clocks,01=3clocks,10=4clocks,11=不支持

Tsrc[19:18]: SDRAM半行周期时间 00=4clocks,01=5clocks,10=6clocks,11=7clocks,SDRAM行周期时间Trc=Tsrc+Trp

Refresh Counter[10:0]: SDRAM刷新计数,刷新时间=(2^11+1-refresh_count)/HCLK,使用PLL后时,HCLK=100MHz,刷新周期为7.8us

refresh_count=2^11+1-100*7.8=1269

REFRESH=0x008C0000+1269=0x008C04F5

5)BANKSIZE寄存器

BURST_EN[7]: 0=ARM核禁止突发传输,1=ARM核支持突发传输

SCKE_EN[5]: 0=不使用SCKE信号令SDRAM进入省电模式,1=使用SCKE信号令SDRAM进入省电模式

SCLK_EN[4]: 0=时刻发出SCLK信号,1=仅在方位SDRAM期间发出SCLK信号

BK76MAP[2:0]: 设置BANK6/7的大小,0b010=128MB/128MB,0b001=64MB/64MB,0b000=32M/32M,0b111=16M/16M,0b110=8M/8M,0b101=4M/4M,0b100=2M/2M

本开发板外接64MB的SDRAM

则本开发板BANKSIZE设为0xB1

6)SDRAM模式设置寄存器MRSRBx(x为6-7)

CL[6:4]: 0b000=1clocks,0b010=2clocks,0b011=3clocks

本开发板取0b011,所以MRSRB6/7取值为0x30

PS:Trcd,Trp的值可通过芯片手册的时序图查的;Tsrc通常取7个时钟。寄存器地址通过芯片手册查询。

汇编代码(利用循环来对寄存器赋值):

#define mem_contrl 0x48000000init_sdram: ldr r0, =mem_contrl add r3, r0, #4*13 adrl r1, mem_data0: ldr r2, [r1], #4 str r2, [r0], #4 cmp r0, r3 bne 0b mov pc, lrmem_data: .long 0x22000000 .long 0x00000700 .long 0x00000700 .long 0x00000700 .long 0x00000700 .long 0x00000700 .long 0x00000700 .long 0x00018001 .long 0x00018001 .long 0x008c04f5 .long 0x000000b1 .long 0x00000030 .long 0x00000030123456789101112131415161718192021222324252627

ps:bne 0b表示不相等时跳回之前的0处。当标号为0~9的数字时,该标号是局部标号。局部标号可以重复出现,使用方法如下:

标号f: 表示往前跳,顺序执行的话是没有运行过的程序 ,front的意思。

标号b: 表示跳转到以前执行过的语句,第一个1标号处 ,back的意思。

上一篇:ARM中的中断向量表

下一篇:S3C2440 SDRAM寄存器初始化设置

推荐阅读最新更新时间:2024-03-16 16:09

设计资源 培训 开发板 精华推荐

- PC产业驶入创新超车道,英特尔蓉城撬动AI新引擎

- 与产业聚力共赢,英特尔举行新质生产力技术生态大会

- “新”享5G-A万兆网络前沿体验 高通携手产业伙伴亮相第二届链博会

- 英飞凌推出符合ASIL-D标准的新型汽车制动系统和电动助力转向系统三相栅极驱动器 IC

- 南芯科技推出80V升降压转换器,持续深耕工业储能市场

- 法雷奥与罗姆联合开发新一代功率电子领域

- 贸泽电子开售能为电动汽车牵引逆变器提供可扩展性能的 英飞凌HybridPACK Drive G2模块

- 德州仪器新型 MCU 可实现边缘 AI 和先进的实时控制, 提高系统效率、安全性和可持续性

- 瑞萨推出高性能四核应用处理器, 增强工业以太网与多轴电机控制解决方案阵容

- 研华全新模块化电脑SOM-6833助力5G路测设备升级

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 【得捷电子Follow me第4期 任务成果代码

【得捷电子Follow me第4期 任务成果代码 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号