频率计数器测量功能介绍

本文主要介绍频率计数器基本测量功能。先给出频率计数器简介,随后分别介绍常见测量功能,最后讨论频率计数器应用。

关键字:频率测量,频率计数器

一、频率计数器简介

电子工程师经常需要测量频率、时间间隔、相位和对事件计数,精确的测量离不开频率计数器或它的同类产品,如电子计数器和时间间隔分析仪。这些仪器为研发提供高精度和分析能力,为大批量生产提供高效率并为维修提供低成本和便携性。

最早的电子计数器是为了对诸如原子现象之类的事情进行计数而设计出来的。在发明计数器之前,频率的测量都是用频率计(一种精度很低的协调装置)完成。频率计数器是以数字方式对信号参数进行精密测量的首批仪器之一。

衡量频率计数器主要指标是测量范围、测量功能、精度和稳定性,这些也是决定价格高低的主要依据。随着电子测试技术的发展,频率计数器日趋成熟。目前,频率计数器已经能轻松测量射频、微波频段信号。除频率测量外,大多数频率计数器还综合了以下功能:频率比、时间间隔、周期、上升/下降时间、相位、占空比、正/负脉冲宽度、总和、峰值电压以及时间间隔平均等。频率计功能延伸的最高境界就是综合了调制域分析仪的功能。

本文从频率计数器基本功能出发,对测量参数分别做出介绍,最后介绍频率计数器的一些数学统计功能。

二、频率计数器测量功能

1、频率(f)

频率表示单位时间波形振动的次数,是周期的倒数,如图1所示。频率是最基本的测量参数。

图1 频率周期图

图1 频率周期图

根据频率的不同范围可把频率计数器分为两类:通用频率计数器和微波频率计数器。前者的测量范围一般在1GHz以下;而微波频率计数器提供从DC到数十GHz的高性能频率测量,可覆盖整个射频、微波频段。高频测量是频率计数器独特的优势,普通示波器很难达到。频率测量很简单,将信号接入频率计数器输入端后再调节功能键至频率测量,屏幕即显示当前频率值。单一的频率测量只需要一个输入通道即可。

2、周期(T)

周期为波形振动一次所需要的时间,是频率的倒数,如图1所示。大多数频率计数器都会提供这项功能。信号周期的测量方法和频率测量基本相似。

3、频率比(f1/f2)

频率比是对两个频率进行比较,它可用来测试倍频器或前置换算器(分频器)的性能。在许多仪器系统中,两个频率的比值远比两个独立的频率值有意义。例如在比率电容传感器研发中,工程师关心的重点是两个信号的频率比,如图2所示。

图2 频率比值

图2 频率比值

这时,用频率计数器频率比功能就能很直观快捷显示出两路输入信号频率比。免去了测量两路信号频率后再自行计算的不便。这项功能要求频率计数器至少有两个通道。如果是有三路输入信号时,可以测量任何两路信号的频率比。

4、时间间隔(ΔT)

时间间隔测量起始信号与终止信号之间所经历的时间。如图3所示,起始信号通常接入到一个通道A,而终止信号则通常接入到另一个通道B,这种功能通常称为世界间隔A到B。测量的分辨率一般为100ns或更佳,有时低到皮秒(10-12)级。

高分辨率时间间隔测量在时间频率传递和测量、航空航天、雷达定位、激光测距等领域具有十分重要的作用。这项功能同样要求频率计数器至少有两个通道。

图3 相位差、占空比、正负脉宽以及上升/下降时间

5、相位差(ΔΦ)

相位差又称为相位移,是指两个频率相等的信号相位之差,表示两信号再时间上的超前或滞后关系。如图3所示,A、B两个通道之间的相位差为72度。

6、上升/下降时间(tr)

上升时间通常定义为信号从其稳态最大值的10%到90%所用的时间,如图3所示。同样,下降时间对应着信号从稳态最大值的90%到10%所用的时间。上升/下降时间和脉宽在数字电路测量中特别有用。若上升时间和下降时间的触发点已知,根据测量出来的上升/下降时间便能显示转换速率(v/s)计算结果。例,图3中测量到上升时间为0.1μs,两个触发点的电平相差0.8V,转换速率为8V/μs。

7、脉冲宽度(tw)

脉冲宽度、脉冲幅度以及脉冲形状是脉冲信号的主要参数。脉冲宽度通常为脉冲幅值为50%时所对应前后两个点之间的时间差。如图3所示,脉冲宽度用来表示脉冲能量作用的持续时间。频率计数器一般都能测量正负脉冲宽度。

8、占空比(duty ratio)

占空比是指信号处于高\低电平的时间所占信号总时间的比率,也可表述为单个脉宽占周期的比例。图3中,正脉冲的宽度和周期的比值为42%,也就是占空比为42%。方波信号的占空比为50%。在其他参数相同的情况下,占空比越大,信号所携带的能量越高。

9、时间间隔平均()

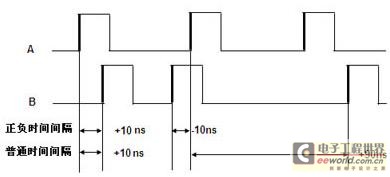

时间间隔平均是一种能给出高分辨率且可用于滤出信号抖动的功能,此功能可准确测量两路信号的时间间隔。这里有两种测量时间间隔的方法:普通时间间隔和正负时间间隔。普通时间间隔测量两个信号的绝对时间差,即两个信号相对应的上升沿时间差。而正负时间间隔测量两个信号之间的相对定时,在它们之间相互前后飘移的场合进行测量。这在调节定时偏移以保证两个信号之间重合一致时非常有用。

下面简要介绍这两种方法的差别。如图4所示,A、B为两路脉冲信号,利用正负时间间隔时,终止沿(B)相对起始沿(A)有+10ns和-10ns的预期结果前后变动。利用普通时间间隔时,当终止沿(B)向左变动时,便会呈现+90ns的未预料的结果。这里应该注意,某些计数器可以测量低到大约0~-5ns的普通时间间隔。

图4 普通时间间隔和正负时间间隔之间的差别

10、累计(count)

累计是对事件的简单计数。它在对电子事件或物理事件计数或自动测试需要数字化结果的场合十分有用。计数器在对事件数进行累加和显示同时,门电路开通。某些情况下,这个功能称为累计计数。

累计有时会有些变化。在正常测量情况下,为了将计数读入计算单元,门电路一开始必须关闭。这意味着在读入时可能丢失一些计数。某些计数器具有连续累计功能,能够在将计数读入计算单元的同时仍然进行计数。少数频率计数器还具有向上-向下计数的能力。一个通道内的事件引起计数增加,但第二个通道的事件引起计数减少。比如,在比较两个需要相互比较的独立轴杆旋转时,应用此功能就会很方便。

三、频率计数器的数学功能

1、标度和偏置

设定标度和偏置并打开数学功能后,显示数值将按以下公式定义:

显示结果=测量结果×标度+偏置设定

使用这种功能,能够让屏幕上显示对用户更有意义的频率值,在实际应用中往往比较方便。此功能的数学处理原理形象表述在图5中。其中,1为原始采样数据,2为经过数学运算后的数据。

2、统计功能

可以用来统计和显示当前输入数据的标准偏差,并能选择统计次数。标准偏差是描述信号一致性好环的参数。标准偏差越大,表示信号幅值相差比较大,一致性差;而较小的标准偏差表示信号的幅值都很接近,信号波动小。

标准偏差可用以下公式描述:

其中,S为样本标准偏差。i从1到n,是总和,是样本均值。

3、极限

可以为输入信号设置频率上下限,只捕获范围内的数据。从图5中能看出,3中设定极限后,根据设定的极限对2中的数据进行筛选,得到4中的数据。当用户需要过滤掉一定范围外的信号时,这个功能提供了很大的帮助。

图5 数学运算和极限处理示意图

四、频率计数器应用

频率计数器功能是根据其应用来设计的。频率计数器最常见的应用是确定发射机和接收机的特性。发射机的频率必须进行检验和校准,才能符合有关规章制度的要求。频率计数器能对输出频率和一些关键的内部频率点(如本振)进行测量,查明无线电发射时候是否满足技术指标。

频率计数器的另一些应用包括计算机领域,在此领域中的数据通信、微处理器和显示器中都使用了高性能时钟。对性能要求不高的应用领域包括对机电产品进行测量。频率计数器的早期应用之一是作为信号发生器的一部分。在信号发生器信号输出之前,先通过频率计数器部件测量该信号,测量到的结果被转换为模拟信号用于反馈控制信号发生器的频率,直到达到所需要的数值,从而能得到稳定的信号输出。目前,很多信号发生器中都集成了频率计数器的简单功能。例如OI1842信号发生器也集成了测量范围为0.1Hz~50MHz的频率计功能。

五、总结

随着频率计数器计数发展,频率计数器的功能不断延伸。频率计数器即具有了时域、频域的功能,更具有了调制域和统计域的仪器测试功能。例如,HM8123可编程多功能计数器就具有最小、最大,平均,标准偏差等统计功能。

在测试技术日新月异的今天,频率计数器功能也在不断完善和丰富来满足不同测试领域的需求。面对不同功能不同规格的仪器,工程师需要根据自己的需要来选择符合自己的仪器,这样才能为测试工作带来最大的效率。

参考文献

【1】(美)库姆斯著, 张伦等译. 电子仪器手册(第三版).科学出版社.2006.5.

【2】Agilent, 53131A 通用计数器操作指南.

【3】Hameg, Products 2007.

【4】北京海洋兴业科技发展有限公司, 频率计基础知识.

上一篇:万用表的设计原理与测量计算方法

下一篇:逻辑分析仪测试在基于FPGA的LCD显示控制中的应用

推荐阅读最新更新时间:2023-10-12 20:34

- 3小时实战+剖析:TI工程师手把手带你全面入门MSP430(限量售$4.3开发套件,助你参与动手实验)

- 【6本精选 ADI 电子书】免费下载 ing

- 【温故喝新之单片机版块】温2016年MCUs,喝2017年版块新篇章

- 有奖直播:联咏安防监控方案及未来技术方向 报名开始啦!

- ST AMG SensorTile开发大赛驾到,重磅大奖与知识兼得,速来~

- 【社区大讲堂】揭秘ADI实验室电路!

- 您的电路保护有足够的空间吗?Littelfuse的881系列保险丝迎接这一挑战

- 有奖直播:5G和边缘计算发展和技术应用

- 2019东芝PCIM在线展会:会一会 电力领域中的高能晶体管们

- MM32F103开发板测评等你来

电气控制与可编程序控制器应用技术(FX_3U系列)

电气控制与可编程序控制器应用技术(FX_3U系列) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号