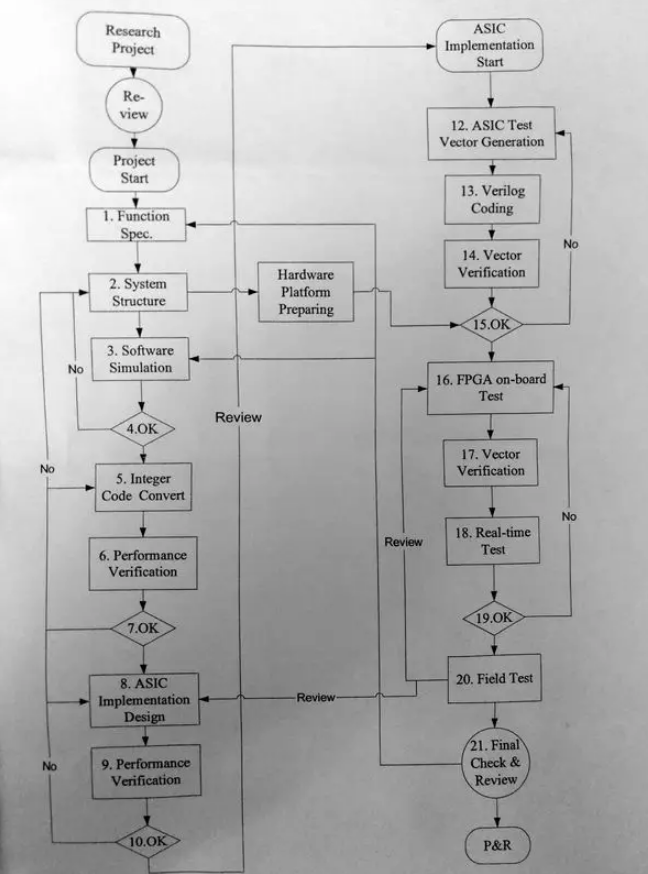

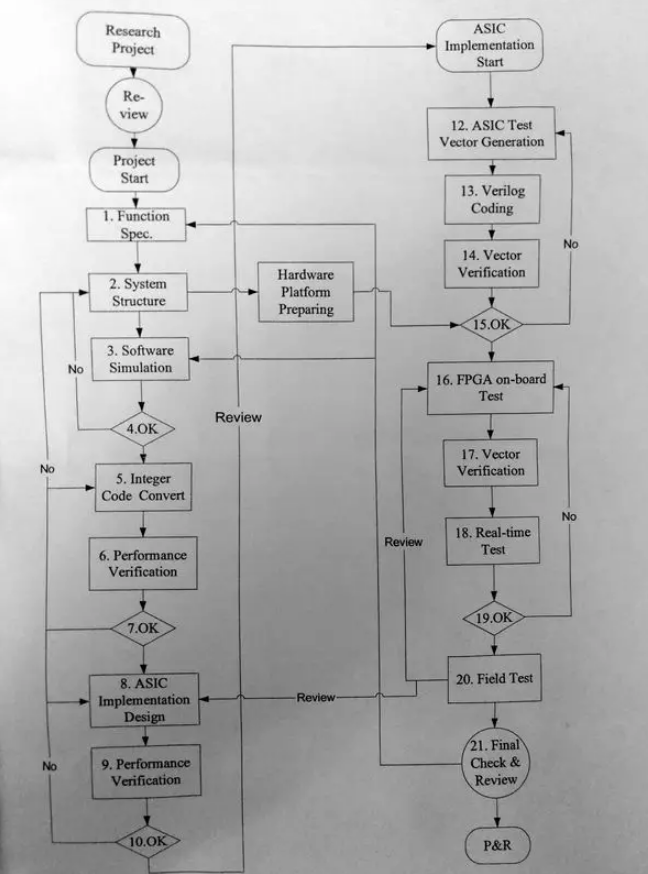

最近收拾书架,翻出一张多年以前的ASIC项目开发流程图,一起回顾一下。典型的瀑布式开发流程:

以算法设计为主导

算法C代码手工转换为RTL

RTL与算法C代码生成的测试向量对比进行验证

依赖FPGA做大量实时、现场测试

适合通信信号处理,音视频处理产品

1. 算法预研

确定了产品方向之后,算法工程师开始进行调研。

要学习研究行业内最新的研究成果、论文,提出创造性的方法来获得最好的性能。要使用真实的测试数据和仿真结果进行评估。最终交付为算法描述的C语言源码。

算法调研结束后需要进行审核(review):确定算法性能,确定系统架构设计,确认是否可以正式立项。审核过程需要算法设计、RTL设计、软件、硬件系统、市场、管理层共同参与。

正式立项时,需要提供功能spec,以及算法C代码功能仿真环境。与此同时,硬件组需要根据项目需求开始搭建硬件FPGA测试平台。

2. 算法优化

接下来进行算法的优化,主要考虑以下几个方面:

算法最终确定需要通过审核:算法架构,算法功能仿真,算法定点化和性能验证。

3. 面向ASIC的C代码实现

在此阶段,算法C仿真代码改变为模块结构代码,分解为若干ASIC功能模块,代码的接口与RTL接口接近:

容易实现

高效率

节省逻辑

重用现有模块

对带有反馈的模块中增加仿真延时

在接口增加仿真延时

最终的C代码中:

主函数只包含连接关系和子模块

所有子模块以各自的时钟速率调用

接口采用cycle based timing

需要准备以下review和文档:

ASIC模块和接口设计指导

性能验证报告

接口变量的时序图和精度描述

4. C到RTL的实现

RTL设计工程师完成从C代码到verilog的实现。算法工程师负责产生相应的测试向量,包括子模块测试和系统联调测试。要使用各种典型的测试场景数据,以及一些子模块级别的随机测试数据。

根据RTL设计以及综合结果,可以获得整个系统的时序信息,gate count和die size预估。

5. FPGA on-board test

由于RTL仿真的速度较慢,可以借助FPGA来进行测试加速。硬件工程师准备FPGA平台,FPGA工程师进行RTL到FPGA的代码移植,软件工程师协助相关测试软件的开发与使用。

在FPGA上可以做到与RTL仿真一样的效果,比如从内存中提供输入,并抓取输出结果,与算法C产生的数据进行比对。需要测试尽可能多的测试用例。

6. FPGA field test

如果项目代码可以在FPGA上跑到与真实应用同样的速度(full speed),就可以用FPGA代码直接做实时现场测试。在现场测试的任何问题,需要反馈给算法组进行分析解决。

7. Final Check and Review

现场测试通过后,需要做最后的检查和review全部代码,然后开始芯片后端设计。

站在今天(2018年)的角度看过去上述流程有存在一些问题:

采用算法C到Cycle C再到RTL实现的流程,迭代长,易出错

RTL验证以直接定向测试为主,缺少随机验证,覆盖率不够

依赖FPGA实时测试作为验证主要手段,FPGA平台开发需要专门的人力资源和硬件平台,而且FPGA平台不够灵活,且容易出现不稳定的问题。

现在已经有很多新技术可以借鉴,比如

最后,以上开发流程简单,投资少,对于算法(大牛)主导的创业型公司,或者以IP开发为主的小型团队,还是可以使用的。

关键字:ASIC

引用地址:

ASIC开发流程一览,全是干货

推荐阅读最新更新时间:2024-05-03 03:26

面对下一代ASIC验证 英特尔发布全球最大容量FPGA产品

“正是因为英特尔在IC工艺技术、制造和封装等领域的创新,让英特尔得以设计、制造并交付目前世界上密度最高(代表计算能力)的 FPGA—— Stratix® 10 GX 10M FPGA。最大容量FPGA对于客户来说是具有非常重要的技术领导地位,这能向客户展示自己的最大技术实力。”近日,在2019英特尔FPGA技术大会上,英特尔公司网络与自定义逻辑事业部副总裁兼FPGA电源产品营销总经理Patrick Dorsey先生,向EEWorld记者介绍了英特尔世界上密度最高的 FPGA产品。 英特尔公司网络与自定义逻辑事业部副总裁兼FPGA电源产品营销总经理Patrick Dorsey先生 世界上密度最高的FPGA产品 “今天英

[嵌入式]

超低功耗ASIC惊艳ISSCC 让机器人小车跑几分钟和几个小时的差别

近日,科学家研发成功一款超低功耗混合信号芯片,该芯片的设计灵感来自对人类大脑的认识,可以帮助手掌大小的机器人协同工作,并从经验中学习。结合新一代的低功耗电机和传感器,该ASIC以毫瓦功率运行,从而可以将单节干电池供电智能机器人的运行时间从几分钟提高到数小时。 佐治亚理工学院的研究人员研发成功一款超低功耗混合信号芯片,该芯片的设计灵感来自对人类大脑的认识,可以帮助手掌大小的机器人协同工作,并从经验中学习。 为了节省功耗,该芯片使用了混合了数字模拟信号的时域处理器,采用信号的脉冲宽度对信息进行编码。该神经网络IC不仅可以适用于基于模型的编程应用,也具备协作能力,可以强化自我学习。它赋予了小型机器人更大的侦查、搜救以及执行其它任务的能

[机器人]

机器学习成长速度惊人,FPGA和ASIC芯片有望成为新主力

在2016年初,机器学习仍被视为科学实验,但目前则已开始被广泛应用于数据探勘、计算机视觉、自然语言处理、生物特征识别、搜索引擎、医学诊断、检测信用卡欺诈、证券市场分析、语音和手写识别、战略游戏与机器人等应用领域。在这短短一年的时间内,机器学习的成长速度超乎外界预期。 DeloitteGlobal最新的预测报告指出,在2018年,大中型企业将更加看重机器学习在行业中的应用。和2017年相比,用机器学习部署和实现的项目将翻倍,并且2020年将再次翻倍。 目前,有越来越多的类型开始丰富“AI芯片”这个新名词,包括GPU、CPU、FPGA、ASIC、TPU、光流芯片等。据Deloitte预测,2018年,GPU和CPU仍是机器学习领域的主

[嵌入式]

可编程系统芯片更像平台式ASIC

电子子工程世界: ASIC的现状有人并不看好,有人预测DSP将出现负增长,您认为FPGA的市场需求以及应用领域的发展现状是什么? Hezi Saar:首先提一个有趣的问题:“如今的ASIC是什么?”,市场分析人士指出,ASIC市场是巨大的,而且正在增长,但是,我们看到传统的AISC设计开始减少。为什么?抽丝剥茧仔细查看,你可以发现从一个平台 (如开放式多媒体应用平台(OMAP)) 演变而来的非常有名的ASSP,来自供应商 (TI) 的产品采用先进的技术 (如DSP),瞄准重要的应用领域 (如手机)。通过硅产品和系统供应商的高效合作,批量应用正在增加。因此,其它产品如何呢?ASIC原来的价值在于大批量定制优势,

[新品]

奥地利微电子为代工用户扩展CMOS、高压、高压FLASH和RF多项目晶圆服务

针对高压CMOS、高压 CMOS 嵌入式 FLASH、SiGe-BiCMOS 和 CMOS 专业工艺的原型时间表将更加全面 中国 —— 奥地利微电子的全方位服务晶圆代工厂业务部推出一份更加全面的 2008 年度时间表,扩展了其具有成本效益的、快速的专用集成电路(ASIC)原型服务,即所谓以多项目晶圆 (MPW) 或往复运行(shuttle run)。该服务将来自不同用户的若干设计结合在一个晶圆上,有助于众多不同的参与者分摊晶圆和掩膜成本。 奥地利微电子的 MPW 服务包括基于 TSMC(台积电)0.35μm CMOS 工艺的全程0.35μm尺寸工艺。兼容 SiGe BiCMOS 技术的 CMOS 有助于在一个 ASIC 中以

[新品]

Altera和Synopsys合作,为ASIC设计提供Nios II处理器内核

新的DesignWare Star IP为处理器设计提供了更多的芯片选择 2007年11月14号,北京 ——Altera公司(NASDAQ: ALTR)和Synopsys有限公司(NASDAQ: SNPS)今天宣布,Altera流行的Nios II处理器内核可通过DesignWare Star IP包提供许可给客户使用。这一新品扩展了Altera现有的FPGA和HardCopy结构化ASIC产品供给,帮助Nios II用户将设计移植到标准单元ASIC。Nios II处理器内核是应用最广泛的FPGA处理器,其客户群有5,000多家电子设备生产商,包括世界上排名靠前的OEM。 Lionic公司总裁Eric Lu评论说:“多年以来我

[新品]

彩色TFT液晶显示控制电路设计/其ASIC实现

1引言 通过彩色液晶显示器(LCD)取景是数码相机优于传统相机的重要特性之一,它解决了使用取景框取景带来的各种不便,而且可以在拍摄现场用液晶显示器回放刚拍的相片来查看拍摄效果 ,从而决定是否留下这张照片,这样能使摄影者更好地控制照片的质量。所以用液晶显示器进行取景和回放是数码相机两大必不可少的功能。同时液晶显示器还用来显示菜单,提供良好的人机交互界面。目前市场上出售的数码相机使用的液晶显示器都是彩色TFT液晶显示器,这种液晶显示器解决了一般液晶显示器中相邻像素串扰的现象 ,所以可用来显示真正的活动图像。 数码相机专用集成电路芯片中的液晶显示控制电路主要实现的功能是向液晶显示模块(LCM)和数模转换器提供所有必需的控制时

[电源管理]

嵌入式系统中IP协议用ASIC器件电路设计

摘 要: 设计并实现一个能完成IP协议功能的ASIC器件;讨论器件的稳定工作条件。任何数字化的工业设备都可以使用这个IP协议器件直接连接到基于IP的网络中。

关键词: 嵌入式系统 IP ASIC

引 言

为了实现网络信息处理,嵌入式系统中必须具有强大的网络连接功能。嵌入式系统的网络连接功能不仅需要传输信息,同时还必须具有相应的信息识别能力,以提高系统的网络安全性。

近年来在嵌入式系统和SOC(片上系统)技术发展的推动下,嵌入IP协议的微处理器或单片机系统已经出现 ,为嵌入式网络技术的应用奠定了基础。但对于工业设备

[嵌入式]

数字逻辑与数字系统 (李景宏 王永军 等编著)

数字逻辑与数字系统 (李景宏 王永军 等编著) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号