了解多线程程序、使用 XOS 实时操作系统开发应用程序、与信号量共享资源,以及 NXP 的 i.MX RT500 系列微控制器如何帮助工程师设计支持 DSP 的智能设备。

当今的智能消费设备需要能够处理大量数据的组件,以满足各种安全和信号处理应用的需求。这些组件(包括微控制器)必须能够快速有效地处理这些数据,这就需要高度优化的数字信号处理器。

本文介绍了 Cadence Tensilica Fusion F1 音频处理器的一些特性,这是一种指定的协处理器,可帮助 i.MX RT500 MCU 的主 CPU 执行信号处理计算。

多线程的核心概念

乍一看,现代处理硬件给人一种同时执行多个线程的错觉。实际上,单个CPU内核一次只处理一个线程。当线程数超过可用CPU核数时,需要操作系统来调度线程。

操作系统需要跟踪所有启动的线程及其状态,并为每个线程分配CPU时隙,以便各种应用程序可以高效地并行运行。

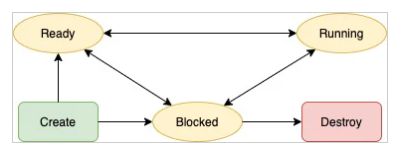

图 1. 不同线程状态

操作系统调度器为准备运行的线程维护一个队列,为阻塞线程维护一个队列,它需要存储当前正在运行的线程的信息,以实现CPU的公平分配:

就绪队列中的线程当前正在等待操作系统在CPU上调度它们。通常,操作系统调度程序知道不同的优先级,它在选择即将在 CPU 上运行的线程时会考虑这些优先级。

阻塞线程等待外部事件发生,例如引脚中断或文件操作。调度这些线程意味着 CPU 浪费处理能力来等待外部操作完成。一旦阻塞操作完成,相关的等待线程返回到就绪队列的末尾。

当前运行的线程可能会执行阻塞操作,或者操作系统可能会根据其调度策略调度不同的线程。在这种情况下,调度程序会将当前运行的线程分别移动到阻塞线程列表或就绪队列的末尾。

操作系统开发人员可以根据具体要求选择实施一种或多种不同的调度策略。除了调度,不同线程之间的同步和通信是多线程系统的其他重要方面。

XOS 中的条件和事件

XOS RTOS(实时操作系统)中的条件允许开发人员指示线程阻塞,直到指定的条件变为真。系统使用应用程序开发人员定义的条件函数来评估每个条件。每当另一个线程向条件对象发出信号或中断处理程序触发一个时,XOS 就会执行评估。

另一方面,XOS 中的事件代表一组位,开发人员可以利用这些位来同步不同的线程或线程和中断处理程序。XOS允许多个线程等待事件并同时向它们发出信号。

XOS 中的中断

XOS 提供了一组丰富的功能来处理运行时发生的中断和异常。XOS中的中断机制为程序员提供了安装自定义处理程序的灵活性,同时确保调度中断在系统内尽可能快地工作。XOS 还支持嵌套中断处理,这意味着如果发生更高优先级的中断,操作系统会暂停当前的中断处理程序。一旦系统处理完高优先级中断,它会自动恢复服务低优先级中断。

线程还可能具有时间相关的服务,例如 XOS 中的定时延迟和周期性定时器回调。DSP 协处理器最多支持三个内部定时器,程序员可以根据需要对其进行配置。

了解信号量

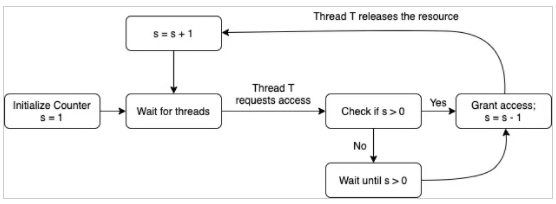

在多线程编程中,信号量提供了一种控制和协调对共享资源的访问的方法。信号量通过同步不同的线程来帮助避免并发系统中的临界区问题。信号量是一种简单的结构,它跟踪一个内部计数器,它具有预定的起始值,程序员可以在源代码中自由设置该值。存在不同的实现,但计数器通常表示仍有多少线程可以访问共享资源。

每当线程想要访问共享资源时,系统都会检查关联的计数器是否大于零。如果是,操作系统授予对资源的访问权限并减少信号量的内部计数器。如果一个线程在给定的时间可能无法访问资源,则该线程切换到阻塞状态并等待,直到它收到对资源的访问。每当线程释放资源时,操作系统都会增加信号量计数器,新线程可能会进入临界区。

图 2. 说明信号量工作原理的流程图

i.MX RT500 MCU 和 DSP 概述

i.MX RT500 是一个双核微控制器系列,基于强大的 Arm® Cortex®-M33 内核,时钟速度高达 275 MHz,支持高达 5 MB 的 SRAM。

i.MX RT500 MCU 提供保护功能,例如 Arm TrustZone 和内置内存保护单元 (MPU),最多支持八个区域。CASPER 加密协处理器支持硬件加速,以提升非对称加密算法所需的各种功能。一组节能功能允许设计人员将 i.MX RT500 的功耗与其应用要求相匹配。

各种专用硬件加速器帮助主 CPU 执行 DSP 计算。额外的 Cadence® Tensilica® Fusion F1 音频 DSP、具有矢量图形加速功能的 2D GPU 和各种显示接口使 i.MX RT500 适用于各种安全和低功耗的嵌入式应用。典型用例包括 HMI 应用程序、IoT 设备、耳戴式设备、语音激活的个人助理和其他类似的消费设备。

音频 DSP 概览

i.MX RT500 包含各种特殊的协处理器,可以通过执行复杂的数学计算来帮助减轻 CPU 内核的负载,同时让处理内核可以自由执行其他任务。比如集成的融合DSP,它包括一个 Cadence® Tensilica® Fusion F1 音频处理器和一个硬件浮点单元。

该音频处理引擎以高达 200 MHz 的频率运行,旨在支持始终在线的语音触发设备,例如虚拟助手。此外,音频 DSP 结合了各种模块,用于使用众多音频编解码器的典型预处理和后处理任务。

DSP 和主 CPU 内核可以通过各种方式相互通信。开发人员在使用融合 DSP 时可以使用整个 SRAM,除非 RAM 受到保护并且某些部分被标记为只能安全访问。

使用 DSP 进行编程

Tensilica DSP 支持各种实时操作系统 (RTOS),包括 FreeRTOS™、Zephyr™、Linux® 和 XOS。 Cadence 开发了 XOS 嵌入式内核作为参考设计。

轻量级 XOS 内核功能包括任务调度程序、自适应上下文切换、同步机制、中断和异常管理以及关键资源管理。内核的源代码主要是用标准 C 语言编写的,并不特定于 Xtensa 处理器和 DSP。

满足智能设备要求

i.MX RT500 系列跨界 MCU 具有各种旨在激发未来智能消费设备的功能。不同的协处理器帮助 MCU 的主要处理内核为安全和信号处理应用执行复杂的数学计算。其中一个协处理器是高度优化的 Cadence® Tensilica® Fusion F1 音频 DSP,可实现虚拟助手等始终在线的语音触发设备。程序员可以利用 XOS 和 Xplorer IDE 为专用 Cadence 处理器设计应用程序。

上一篇:国产开源RISC-V处理器“香山”发布,7月流片

下一篇:蓝洋智能推出高性能低功耗AI芯片

推荐阅读最新更新时间:2024-11-17 15:57

- 超级电容保护板6串[未验证]

- AM2G-2407DZ ±7.2V 2 瓦 DC/DC 转换器的典型应用

- AD9269-65EBZ,用于 AD9269BCPZ-65、2 通道、16 位、65 MSPS 模数转换器的评估板

- LM2931AZ5低压差稳压器典型应用电路

- LT6654AMPS6-3.3、16 位 ADC 电压基准的典型应用

- ZR431 可调精密齐纳并联稳压器的典型应用

- KIT17XS6500EVB: 评估套件 - MC17XS6500,五通道高边开关

- pt4205小功率横流驱动 (未验证)

- LTC1759 的典型应用 - 智能电池充电器

- 使用 Microchip Technology 的 TC33163 的参考设计

无线通信的MATLAB和FPGA实现

无线通信的MATLAB和FPGA实现 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号