1 引言

JPEG2000是新一代静止图像压缩国际标准,具有优越的图像压缩性能和高的图像质量,不仅克服了传统JPEG静止图像压缩标准在高压缩时出现方块效应的缺点,还提供了图像渐进传输、图像质量可伸缩及感兴趣区域编码等特性,可以应用于数码相机、医疗图像、网络传输等方面。

2 JPEG2000标准基本原理

2.1 JPEG2000编解码框架

JPEG2000编码器编码主要有预处理、小波变换、量化和熵编码等步骤,相对于编码过程,该系统的解码过程比较简单[1]。JPEG2000编解码器框图如图1和图2所示。

图1 JPEG2000编码器框图

图2 JPEG2000解码器框图

2.2 JPEG2000编码的核心算法

1) DWT变换

通过离散小波变换多级小波分解,小波系数既能表示图像片中局部区域的高频信息也能表示图像片中的低频信息。这样,即使在低比特率的情况下,也能保持较多的图像细节,另外,下一级分解得到的系数所表示图像在水平和垂直方向的分辨率只有上一级小波系数所表示的图像的一半,所以通过对图像的不同级进行解码,就可以得到具有不同空间分辨率的图像。

2) EBCOT算法

EBCOT算法的基本思想是将小波变换以后的子带划分为大小固定的码块,对码块系数量化,按照二进制位分层的方法,从高有效位平面开始,依次对每个位平面上的所有小波系数位进行三个通道扫描建模(重要性传播编码通道、幅度精炼编码通道、清除编码通道),即位平面编码,生成上下文和0、1符号对,然后对这些上下文和符号对进行上下文算术编码,形成码块码流,完成第一阶段编码块编码;最后根据一定参数指标如码率、失真度,按率失真最优原则在每个独立码块码流中截取合适的位流组装成最终的图像压缩码流,完成第二阶段码流组装过程[2]。

2.3 EBCOT算法中块编码算法的改进研究及实现

在JPEG2000编解码系统中,EBCOT算法是其重要的组成部分。而EBCOT算法中的第一阶段块编码又是整个算法的核心,它占用了大量的编码时间,无论是无损压缩还是有损压缩,EBCOT算法中的位平面编码时间都占到整个编码耗时的50%以上[3][4]。所以,自从EBCOT算法提出后,由于第一阶段块编码的运算量比较大、编码速度较慢,针对这种情况的优化改进研究很有必要。

图3为barbara图像(256×256)在位平面编码时三个通道系数编码数量变化示意图。图中通道1表示重要性通道,通道2表示幅度精练通道,通道3表示清除通道。由图可以看出,在最高位平面MSB,所有系数都只在清除通道进行编码。重要性传播通道中编码的系数数量先是增加,然后由于在重要性传播通道中的系数已变为重要的,所以在重要性传播通道中编码的系数数量又逐渐减少。在低位平面(0、1、2)大部分系数在幅度精练通道中编码,只有一少部分在重要通道中编码,没有系数在清除通道中编码。在整个扫描编码过程中,三次扫描要形成三次上下文并判断其所属编码通道,这样就会使编码时间大幅度增加。

图3 位平面编码三个通道系数编码数量变化示意图

根据对图3的数据分析研究,本文给出两种针对于位平面编码的改进方法[5]。

(1)位平面0、1、2清除通道编码省略法。由图3可以看出在较低位平面(即位平面0、1、2)上清除通道实际编码的像素是很少的,几乎为零。所以花费时间对较低位平面上的清除通道进行扫描编码是无意义的。本论文就此给出一种改进方案即省略较低位平面的清除通道编码,达到改进标准算法的目的。该编码模块与标准算法此部分代码相近,只是对编码条件进行了改变。

(2)位平面6、7一次扫描法。由图3可以看出在高位平面(位平面6和位平面7)重要性传播通道和幅度精练通道的编码量都很低,趋近于零,而清除编码通道编码的像素量相反却很高。在标准算法的扫描机制下,对图像质量影响很小的高频子带像素编码,扫描算法必须从最高平面由高向低分三次完整的扫描。本文给出一次扫描法对较高位平面进行改进,即在一次扫描过程中对最高位平面和次高位平面所有系数进行编码。在一次编码一个系数时,通过上下文的形成,先确定此系数属于哪个通道。然后,此系数按所属通道马上进行相应编码。这样就能减少两次扫描,节约了编码时间,从而能够提高编码效率。本文处理的对象主要是8比特的灰度图像。有损压缩采用9/7小波变换。

通过对压缩性能研究发现,在压缩比较小时本文改进算法比标准算法的压缩性能约低0.4db左右,在压缩比较大时两者的压缩性能相一致,保留了JPEG2000优异的压缩性能;从编解码时间来看,在有损压缩编码执行时间上,本文所给出的改进算法比标准算法时间缩短8%到12%,解码时间缩短2%到5%,提高了编码效率,达到了改进的目的。

3 JPEG2000标准中改进算法的DSP实现

3.1 DSP硬件开发平台

本文使用评估板是北京闻亭公司的TDS642,板上的DSP芯片是TMX DM642,BGA548封装,内部工作时钟为600M,外部总线时钟为100M,计算能力高达4.8亿指令每秒。

该平台提供了丰富的外围接口。板上有两个复合视频(PAL/NTSC/SECAMS)输入和1个复合视频输出端口;立体声输入/出或单一麦克风输入端口;提供两个UART、以太网接口、子板接口、PC104接口和JTAG接口[6][7]。板上还提供了4M Bytes的Flash存储器,位于DM642的CE1地址空间,宽度为8bits,FPGA扩展了3根地址线,把Flash分成8页,Flash 的第0页的前半页存放用户的自启动程序,后半页存放FPGA程序,第1页尾用户存放数据空间,第2页至第8页用于存放用户程序。

3.2 核心算法的DSP实现

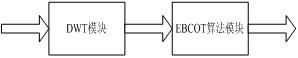

(1)算法总体框架。本文算法基于DM642EVM实现时主要分为两个大的模块(如图4),第一部分为DWT变换模块,它将输入图像数据变换为一系列的小波系数;第二部分为EBCOT算法模块,将量化后的的小波系数编码生成压缩码流。硬件开发平台结构框图如图5所示。

图4 算法框架图

图5 算法硬件开发平台结构框图

(2)内存分配。对于图像数据的处理,往往涉及到大量的复杂的数据寻址计算,对于复杂的寻址计算,其耗费CPU的计算量可能比实际数据操作的计算量还大。所以要加快CPU对数据的访问速度,不但要求存储器本身的速度快,而且还需要一个合理的数据结构来简化CPU对地址的计算。另外,DM642对数据的访问技术,如Cache、EDMA和宽bit数据直接读写等,都是基于存储地址的连续性。基于以上考虑,本文在内存分配及定位时,依据以下大的原则:第一,在满足精度要求的情况下,使用较短的数据类型;第二、大的数据块,如原始图像、重构图像存储在片外SDRAM;第三、关键数据、小的数据块,比如运算时的系数、系统堆栈、三个通道扫描都需要频繁的访问数据区和上下文标志区等,存放到片内存储器;第四、对L2级配置足够的Cache以便CPU对数据的快速读写;第五、对于具有运算相关性的数据,应在内存中按序连续排放。当涉及到片内外数据块的搬移操作时,可由DM642的EDMA单元去完成,它可与CPU并行工作,不占用CPU的计算周期[8]。

(3)图像数据的读写。由于本文工作主要完成针对图像的压缩功能,不涉及图像采集,所以在图像数据的输入输出上做了适当的处理。考虑到CCS的Simulator完全支持C/C++语言,因此原始图像数据的输入采用C语言中的头文件形式,小波变换模块,EBCOT算法模块采用存放在PC机的数据文件形式。本文主要采用头文件和二进制数据文件的形式,将图像的非文件头部分的所有数据通过“fprintf(fp,“%3d,”,image_in [i][j])”语句写到.h文件中。

(4)DWT的实现。由于DM642为定点处理器,不适合于浮点运算,所以本文选择LeGall(5,3)整数滤波器完成JPEG2000中的小波变换。在进行小波变换时,首先定义两个与图像块大小相等的存储缓冲器,一个是图像片数据的输入缓存Buf,一个是用来临时存放图像片数据经小波变换后的结果缓存TempBuf。每经过一级小波变换,图像片数据都要先后两次经过integer(5,3)的低通和高通滤波。TempBuf中保存的高通滤波数据经integer(5,3)滤波器处理后,得到HL子带和HH子带的小波变换系数。最后将变换结果存放到输入缓存Buf中。若要进行下一级分解,只需对Buf中LL子带进行同样处理。

(5)EBCOT算法的实现。EBCOT算法是JPEG2000编码系统中耗时最大的一个部分,因此对这一部分进行优化实现对整个系统的性能提高很有意义。在PC机上,EBCOT编码中的每个通道都是被独立处理的。因此,在DM642上实现的时候,本文采用并行性技术来优化代码,加快程序的执行速度,比如在取位平面数据的时候可以和构造上下文模型并行处理,但是并不是简单的并行处理,当要形成通道二的上下文模型时,其邻域的数据在处理通道一的时候己经被改变。这样做可以增加DM642功能单元的利用率,充分发挥出它的并行计算能力。

3.3 实验结果

本文实验基于Windows XP操作系统、CPU Intel Pentium(R)4 2.4GHz、512M内存、CCS编译环境,程序通过USB仿真器下载到DM642EVM开发板上进行,采用LeGall(5,3)小波,处理图像为512×512的lena和barbara图像。经测试,压缩比为16:1时编码器编码相应耗时如表1所示。

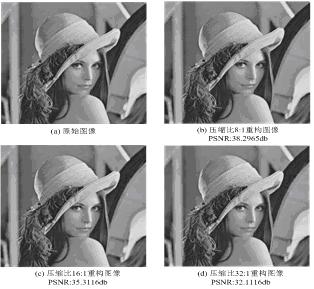

实验给出了lena图像在8:1、16:1、32:1三种压缩比下的重构图像,并分别给出了与原始图像的峰值信噪比,如图6所示。

图6 barbara图像编码图

表1数据表明,编码器基于DSP的编码耗时相比基于PC的耗时有所增加,是因为代码在DM642EVM硬件平台上运行时需要持续的通过USB仿真器和PC机交换数据,从而增加了时间的开销。从图6中的PSNR值可知,lena图像在较高压缩比下的重构图像仍具有较高的图像质量。就主观评价来讲,压缩比为8:1和16:1的重构图像与原始图像差别细微,视觉效果好;压缩比为32:1的重构图像略有失真。实验结果表明,移植到DSP上的JPEG2000编码算法代码仍具有良好的压缩性能。

4 结束语

为了实现对图像的高效压缩,在这里使用了DWT变换和EBCOT算法,并给出两点改进方法。通过将改进的算法移植到DSP开发板上,可以看出图像在高压缩比的重构图像仍具有较高的图像质量,结果表明移植到DSP上的JPEG2000编码算法代码仍具有良好的压缩性能,在图像压缩处理中有较好的尝试应用。

上一篇:Altera在亚洲16城市举办2009 AP技术巡展

下一篇:联电65纳米曝良率问题 Xilinx受损

推荐阅读最新更新时间:2024-05-02 20:50

深度学习核心技术与实践 (猿辅导研究团队)

深度学习核心技术与实践 (猿辅导研究团队) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号