1 引言

数据采集系统常需要进行异步串行数据传输。目前广泛使用的RS232异步串行接口,如8250、 NS16450等专用集成器件,虽然使用简单,却占用电路板面积、布线复杂等缺点。片上系统SoC(System on Chip)是以嵌入式系统为核心,以IP复用技术为基础,集软、硬件于一体的设计方法。使用IP复用技术,将UART集成到FPGA器件上,可增加系统的可靠性,缩小PCB板面积;其次由于IP核的特点,使用IP核可使整个系统更加灵活,还可根据需要实现功能升级、扩充和裁减。这里采用VHDL语言编写 UART模块,将其集成到FPGA上,与器件其他功能模块构成片上系统SoC。

2 异步串行口模块设计与实现

2.1 UART结构

图1为完整的UART接口,包括由发送锁存器、发送移位寄存器和逻辑控制组成的发送模块(txmit),以及由接收锁存器、接收移位寄存器和逻辑控制组成的接收模块(rxcver)。发送模块和接收模块除共用复位信号、时钟信号和并行数据线外,各自分别有输入输出和逻辑控制单元。

2.2 UART的帧格式

图2为UART的帧格式。该帧格式包括线路空闲状态(idie,高电平)、起始位 (start bit,低电平)、5~8位数据位(databit)、校验位(parity bit,可选)和停止位(stop bit,位数可为1、1.5、2位)。该格式是由起始位和停止位实现字符同步。UART内部一般有配置寄存器,可配置数据位数(5~8位)、是否有校验位和校验的类型、停止位的位数等设置。

2.3 波特率时钟的控制

由于数字量接口、工作模式选择、实时监测接口的波特率都不同,UART核包含一个可编程的波特率发生器,可灵活配置波特率。波特率发生器给发送模块和接收模块提供发送数据和接收数据的基准时钟,波特率发生器产生的时钟mclkx16是串行数据波特率的16倍。它对系统时钟n分频,n=系统时钟/波特率×16,针对不同波特率设定相应数值可得到所期望的波特率时钟。[page]

2.4 发送模块设计

发送模块分为空闲、载入数据、移位等3种模式。如图3所示。当并行8位数据从总线写入发送模块后,发送模块将并行数据装入锁存器thr中,然后在移位寄存器tsr中将数据移位,产生完整的发送序列(包括起始位,数据位,奇偶校验位和停止位),以相应波特率从tx发送。发送模块的输入时钟mclkx16是串行数据波特率的16倍,模块内部将其16分频后得到波特率时钟txclk。

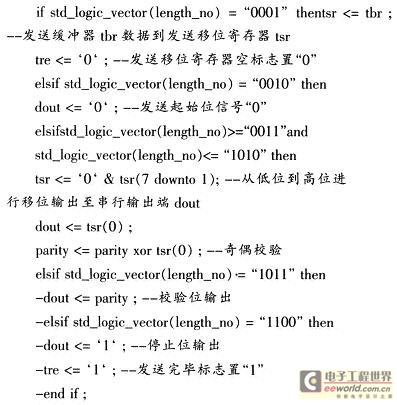

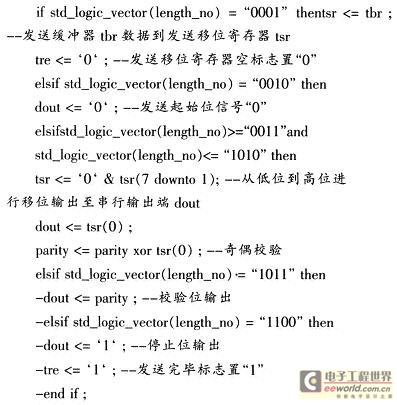

发送模块部分VHDL程序如下:

2.5 接收模块设计

接收模块也分为空闲、检测起始位、移位等3种模式。如图4所示。首先捕捉起始位,在 mclkx16时钟下不断检测从rx端输入数据的起始位,当检测到起始位后,接收模块由空闲模式转换为移位模式,并且16分频mclkx16产生 rxclk波特率时钟。此时rxclk时钟的上升沿位于串行数据每一位的中间,这样接下来的数据在每一位的中点采样。然后由rxclk控制在上升沿将数据位写入移位寄存器rgr的rsr[7]位,并且rsr右移1位,依次将8位数据全部写入rsr,并且停止产生rxclk波特率时钟。判断奇偶校验、帧结构和溢出标志正确后,rsr寄存器中的数据写入rhr数据锁存寄存器中,最后由8位数据总线输出转换完成的数据。

接收模块部分VHDL程序如下:

[page]

[page]

3 硬件电路设计

UART IP核设计完成后需要嵌入FPGA系统中才能运行,该系统选用Xilinx公司Spartan-IIE XC2S50型FPGA和与其配套的EPROM XC18V01组成,如图5所示。该系统已实现设计要求的功能,实现IP核的验证。

4 结果分析

程序经仿真验证后,须综合生成IP核并嵌人FPGA中。使用Xilinx公司的Xilinx ISE工具综合UART模块,FPGA选用Xilinx公司Spartan-IIE XC2S50,系统时钟40 MHz。经Xil-inx ISE后,资源使用结果如表1所示。表明使用少量FPGA的Slice和LUT单元就可生成UART核,节省资源UART核可灵活分成接收和发送两部分,可根据需要选择使用。节省系统资源;一些控制标志字也可根据需要自行删减和扩充。最后将集成有UART核的FPGA数据采集系统与测试台进行异步串行通信实验,检测通信数据表明使用UART核传输数据稳定可靠。

5 结束语

数据采集系统经常采用UART异步串行通信接口作为系统的短距离串行通信。相对于传统的UART器件来说,把具有UART功能的IP核集成在FPGA中的更有利于提高数据采集系统的可靠性和稳定性,减小电路板面积。该系统设计的UART IP核通过仿真验证,经综合、编译、嵌入FPGA,成功实现系统通信。

关键字:FPGA RS232 IP核

引用地址:

基于FPGA的RS232异步串行口IP核设计

推荐阅读最新更新时间:2024-05-02 21:03

基于FPGA的Cadence Protium S1原型验证平台

物联网跨越多个应用领域,根据最终应用领域的不同,设计团队的要求可能会大相径庭。功率,性能和成本是芯片设计的优先事项,而汽车和航空航天/国防等应用领域则还需要考虑功能安全性,在其他领域,信息安全性是关键或现场可升级性的需求。 验证,原型设计和软件开发是这些领域和设计要求中的共同点。为了允许进行嵌入式软件开发,通常认为早期的验证技术太慢,而使用虚拟平台(例如QEMU)进行的抽象有时不够准确。 长期以来,基于FPGA的原型设计一直是芯片诞生前软件开发的首选平台。以Cadence Palladium Z1企业仿真平台之类的工具中的硬件仿真相类似,它可以将执行性能从MHz级别扩展到100 MHz,而且成本更低,从而可以将其交给软件团

[嵌入式]

自制无源RS232转485转换器

一、RS-232、RS-422与RS-485的简单介绍 RS-232、RS-422与RS-485都是串行数据接口标准,最初都是由电子工业协会(EIA)制订并发布的。RS-232在1962年发布,命名为EIA-232-E,作为工业标准,以保证不同厂家产品之间的兼容。其传送距离最大约为15米,最高速率为20kb/s,并且RS-232是为点对点(即只用一对收、发设备)通讯而设计的。所以,RS232只适合于本地通讯使用。 调频FM发射话筒制作套件

RS-422由RS-232发展而来,它是为弥补RS-232之不足而提出的。为改进RS-232通信距离短、速率低的缺点,RS-422定义了一种平衡通信接口,将传输速率提高到10

[嵌入式]

Stratix II FPGA系统电源设计

0 引言 Stratix II是ALTERA公司生产的一款高性能FPGA器件。它采用TSMC的90 nm低k绝缘工艺技术生产,等价逻辑单元(LE)高达180 k,嵌入式存储器容量达到9 MB。该器件不但具有极高的性能和密度,而且还针对器件总功率进行了优化,同时可以支持高达1 Gbps的高速差分I/O信号,因而是一款超快的FPGA。该芯片中所含的高性能嵌入式DSP块的运行频率高达370 MHz。另外Stratix II还有12个可编程PLL,并具有健全的时钟管理和频率合成能力。能实现最大的系统性能。 MAX1951是MAXIM公司的一款高效的DC-DC电源转换芯片,主要用于DSP、FPGA、ASIC的内核及I/O口供电。其高达9

[电源管理]

球形检测器在MIMO通信系统中的应用及FPGA实现

空分复用 (SDM) MIMO 处理可显著提高频谱效率,进而大幅增加无线通信系统的容量。空分复用 MIMO 通信系统作为一种能够大幅提升无线系统容量和连接可靠性的手段,近来吸引了人们的广泛关注。 MIMO 无线系统最佳硬判决检测方式是最大似然 (ML) 检测器。ML 检测因为比特误码率 (BER)性能出众,非常受欢迎。不过,直接实施的复杂性会随着天线和调制方案的增加呈指数级增强,使 ASIC 或 FPGA 仅能用于使用少数天线的低密度调制方案。 在 MIMO 检测中,既能保持与最佳 ML 检测相媲美的 BER 性能,又能大幅降低计算复杂性的出色方法非球形检测法莫属。这种方法不仅能够降低 SDM 和空分多接入系统的检

[模拟电子]

S2C现可提供DDR2和DDR3原型就绪IP

S2C公司,领先的快速SoC原型解决方案供应商,宣布S2C的客户现在可以购买工作在S2C第四代S4 TAI Logic Module上的DDR2和DDR3原型就绪IP。该IP允许用户在S2C基于Altera Stratix IV的FPGA原型硬件运行即开即用的2G DDR2到533Mbps,2G DDR3到800Mbps。FPGA上DDR2和DDR3运行在如此高的频率需要大量的工程工作,S2C公司已预先完成这些设计工作,让工程师能够快速创建SoC原型。 DDR2和DDR3原型就绪IP利用Altera Quartus软件提供的存储控制器,使用选定的经过S2C测试的DDR2和DDR3 SO - DIMM内存,经过预映射和良好

[嵌入式]

FPGA或将成为电子系统制造商救命利器

根据赛灵思的分析,2007年可编程逻辑芯片市场约为36亿美元,2012年将快速增长到140亿美元。推动这一巨幅增长的因素来自以下三个方面:智能视频分析和监控、更高带宽网络通信、高清视频广播、HDTV和互联网音视频流传输等数字多媒体融合市场的需求、FPGA的性能、成本、功耗和容量已经接近甚至超过此前ASIC或ASSP的水平、以及当前金融和经济危机导致的快速、量小和多变的客户需求趋势。 今年二月初赛灵思(Xilinx)为庆祝其新LOGO诞生和25周年生辰而在北京举办的庆典活动上,赛灵思新任CEO Moshe Gavrielov在其致贺视频片断中用短短的四个英文单词“Do more with less”就非常到位地概括了当

[嵌入式]

推动数据中心重构,服务数字经济时代

于日前举行的英特尔数据中心事业部专场上,英特尔高级副总裁兼数据中心事业部总经理柏安娜女士探讨了数据中心将如何被重新架构,这在很大程度上是受到数字服务经济崛起的推动。在此次会议上,柏安娜女士描述了日益扩大的工作负载优化、软件定义基础设施转移以及行业向高级分析的变革等趋势将如何定义未来的数据中心。

新闻要点

在IDF上,七家公司展示他们利用即将推出的英特尔硅光子光学模块开发的早期原型设备。这项英特尔技术把光子模块的速度(100Gbps)和范围(目前最高300米,未来将达到2000米)与CMOS制造具体的批量和可靠性等优势相结合。今年年末将发布有关英特尔硅光子技术的更多信息。

F5 Networks公司表示,它是首批评估英特

[嵌入式]

超高数据流通量FPGA新品类中的Block RAM级联架构

概述 随着数据中心、人工智能、自动驾驶、5G、计算存储和先进测试等应用的数据量和数据流量不断增大,不仅需要引入高性能、高密度FPGA来发挥其并行计算和可编程硬件加速功能,而且还对大量数据在FPGA芯片内外流动提出了更高的要求。于是,在FPGA芯片中集成包括片上二维网络(2D NoC)和各种最新高速接口的新品类FPGA芯片应运而生,成为FPGA产业和相关应用的新热点。 拉开这场FPGA芯片创新大幕的是全球最大的独立FPGA技术和产品提供商Achronix半导体公司,其采用7nm工艺打造的Achronix Speedster7t FPGA不仅拥有诸多高性能外围Hard IP,而且是全球首次在FPGA的逻辑阵列上集成了2D N

[嵌入式]

[page]

[page]

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号