使用嵌入式微处理器的FPGA设计不断增长。根据Dataquest的统计,一年大约启动10万个FPGA设计项目,其中约30%包含某种形式的微处理器。

形成这种趋势有几个方面的原因。首先,数据流应用更适合可编程硬件,同时嵌入式微处理器更适合于执行控制流的应用。第二,要改变设计时,嵌入式处理器呈现更大的灵活性。最后,用软核的嵌入式微处理器消除了处理器过时的风险。从传统上而言,对嵌入式FPGA微处理器有一些限制,包括成本,速度和设计性能。随着工艺技术和设计技术的进步,这些限制正在不断改善,现在设计人员更有可能在他们的应用中考虑使用嵌入式FPGA微处理器。

与过去相比,现成的微处理器已经大大比嵌入式微处理器便宜。但是,今天的低成本FPGA被证明是一个节约成本的解决方案。如果设计中已经使用了FPGA,处理器可以整合到现有的FPGA架构,节省了分立器件或新的FPGA成本。设计周期也是一个重要的因素。将硬件与微处理器子系统构成相关的架构并进行实施能有多快?编写,测试和在微处理器上调试运行的代码需要多久?在过去几年中,在整体功能和易用性方面,针对嵌入式微处理器开发的软件工具也有了明显的改善。因此,现在可以在几分钟内运行设计,并且进行测试。产品上市的时间缩短了,因为现在用软件实现功能比硬件更快,更简单。

用现成的微处理器达到的性能有良好的历史记录。随着技术的改进,FPGA在功能和整个系统的速度方面有了显著的进步。由于现在的FPGA能够处理更大的带宽,嵌入式处理器对于许多设计有很大的吸引力。此外,由于FPGA与其他专用模块的紧密配合,软IP核的扩展性提供了一个系统接口,就性能和吞吐量方面而言,现在一个片上处理器可以提供卓越的设计方案。

当评估诸如LatticeMico32这样的特殊处理器时,使用嵌入式软处理器的优点非常清楚。

一个典型的嵌入式处理器子系统

让我们来看看一个典型的嵌入式处理器子系统,例如,LatticeMico32软处理器。该处理器需要有能与外界通信的功能,因此通常核连接到一个片上总线系统,在此情况下是WISHBONE开放源代码总线。然后还需要一个存储系统,用来保存处理器程序代码以及处理器核使用的数据。对外部通信而言,在一个典型的系统中有各种接口,从简单的通信接口和连接、更复杂的协议到应用中的专用硬件模块。现在该处理器总线架构需要连接外设和存储器系统。一个典型的系统如图1所示。

图1 典型的嵌入式RISC处理器子系统

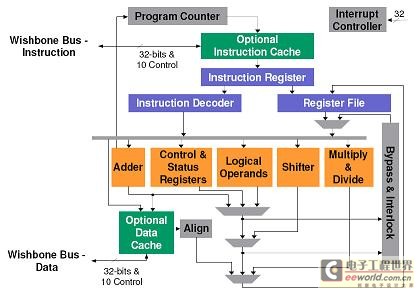

让我们来看看处理器核本身:LatticeMico32是基于哈佛总线结构的RISC架构的微处理器(图2)。 RISC体系结构提供了一个简单的指令集和更快的性能。哈佛总线架构提供独立的指令和数据总线,能够执行单周期指令。该处理器拥有32个通用寄存器,可处理多达32个外部的中断。定制的处理器可以插入乘法器或桶形移位器,以及不同的调试功能。

图2 LatticeMico32:一个可配置的RISC处理器核

Mico32可以用于各种存储系统,同时使用内嵌存储器用于存储指令和数据。内嵌存储器可以建立一个本地哈佛结构,并允许单周期访问指令和数据。对于更大的存储器需求,处理器通过一个仲裁器连接到其他的存储器模块或接口。这可以是用FPGA的存储器资源来实现的 “片上”存储器,或接口至外部存储器,诸如SSRAM、Flash和DRAM。处理所有访问协议至外部存储器的合适接口模块是由MSB提供的。提供可选的指令和数据高速缓存,能够配置成各种选择(高速缓存的大小,高速缓存块的大小等等)。

通过一个开放源码Wishbone总线接口,该处理器连接到各种外围元件。针对快速周转周期,图形用户界面可以轻松和快速地创建处理器平台。除了标准存储器控制器,这可能包括各种接口,不仅支持I2C、通用IO、定时器,UART以及SPI,还能支持更复杂的模块,如PCI接口或TriSpeed以太网MAC。

直接存储器访问(DMA)控制器是可用的,添加主器件(master)至Wishbone总线,以免除处理器的数据传输工作。这也允许有DMA功能的外设高效地直接传输数据到存储系统,从而节省了片上总线的带宽。

除了外围元件和DMA,用户可以自定义仲裁方案。总线结构产生器支持主器件(master)方和从器件(Slave)方的总线仲裁。如果能够满足系统性能的要求,主器件方总线仲裁提供了一个简单的低成本解决方案。然而,如果在设计中有多个总线主器件和多个从器件,在任何时间主器件方总线仲裁限制与单总线主器件通信。在许多设计中,通过两个或两个以上的总线主器件同时与独立的从器件进行通信,从器件方仲裁改进了性能。图3展示了可用的仲裁方案。

图3 仲裁方案

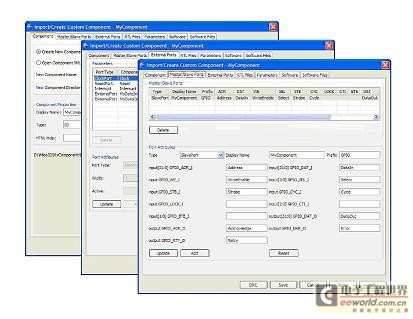

用户还可以创建自己的基于Wishbone总线的外设元件,然后通过整合到MSB自动连接到总线。因此,LatticeMico32的架构提供了两种可能性:第一,人们可以创建定制的元件,将它放人MSB中的可用元件列表(图4)。第二,可以构建出所谓的Passthru元件,可以将Wishbone接口引出到核的外面,因此,用户可以在FPGA的其他部分添加任何逻辑块。

图4 创建定制的外围组件

这些配置选项能够针对不同的应用定制LatticeMico32。带宽范围从小的和片内或片外存储器面积优化的控制器到具有多个接口的全功能平台,以及访问更大的存储器(可能是片外)。从FPGA访问其他的逻辑模块还允许处理器系统和FPGA专用模块之间的密切互动,以便进一步改进性能。取消了传统上使用并行于FPGA的外部控制器的复杂访问机制。

可扩展性

由于处理器代码是可读的Verilog RTL代码,用户可以轻松识别IP功能块,诸如取指令单元,指令译码或ALU,以及各种流水线阶段。因此,通过定制指令,这些也可以修改和增强。用户也可以执行操作码。因此,在指令字中,LatticeMico32提供了备用的操作码域。

遵照以下一些基本的步骤,可以构建自定义指令:

- 增强的指令译码器。这是一个简单的情况,提取内部操作码的功能,并生成需要整合此命令至LatticeMico32的所有必须的控制信号。

- 写功能的实现并将其整合至LatticeMico32 的ALU。

- 对于多周期命令,构建必要的拖延信号,以便妥善处理处理器流水线。

- 如果需要其他的专门逻辑(例如额外的专用寄存器),这可以单独的添加到核。

通过定制指令和添加定制外设,扩展处理器核是一个非常有效的方式,用来定制处理器的核以便实现系统的性能要求。通常情况下,一些专门的功能用硬件实现比软件更好。或并行处理可以获得额外的性能。这种机制能够无缝集成硬件加速模块至处理器架构。这将保持用同样的方式处理这些部件的功能,如同正常的软件代码或使用标准外设。

对于需要数据/信号处理功能的应用,往往需要组合RISC处理器的功能和DSP,以达到系统的性能和吞吐量。添加扩展和定制元件还可以包括信号处理单元。可以用硬件非常有效地实现,使用专用的DSP块,诸如乘/累加,用各种FPGA的硬件都可以实现这些功能。

设计环境

LatticeMico32系统拥有三个集成工具:

- MicoSystem Builder(MSB)

针对硬件实现,MSB产生平台描述和相关的硬件描述语言(HDL)代码。设计人员可以选择连接到微处理器的外围组件,以及指定它们之间的连接。

- C/C++软件工程环境(SPE)

C/C++ SPE调用编译器,汇编器和连接器,使代码的开发针对运行于用MSB构建的平台。可以通过C/C++ SPE来完成,用MSB构建的平台可以作为参考。

- 调试器和Reveal逻辑分析器

在C/C + +源代码调试器提供汇编中的调试功能,并能够观察处理器的寄存器和存储器。设计人员还可以使用莱迪思的Reveal逻辑分析器观察和控制硬件中代码的执行情况。

所有的工具和IP已完全纳入莱迪思的ispLEVER FPGA软件设计环境,这使得通过整个FPGA设计流程快速的进行设计。这些工具也有利于有效地使用FPGA的资源。

在构建过程中,用完全可读的RTL Verilog源代码创建处理器的代码及其外围设备。提供用于综合和仿真的脚本,约束文件关注硬件的设置和引脚。

目前有3种操作系统: Theobroma Systems的uClinux 和U-Boot、Micriμm的μC/OS-II RTOS和TOPPERS/JSP的μITRON RTOS。

LatticeMico32提供了一个开放源码许可证。莱迪思的开放IP核许可协议将与MSB工具生成的HDL代码一起使用。大部分图形用户界面将在Eclipse的授权许可下使用,同时对软件的内部运作,如编译器、汇编器,连接器和调试器,许可协议将遵循GNU-GPL。

因为这是开放源码软IP,这个处理器的IP核还可以免费迁移到其他技术并加以实现。

性能和资源利用

LatticeMico32提供高性能和尽可能高的资源利用率。对于关心资源的设计人员,基本配置不使用任何指令或数据高速缓存,单周期移位器,也没有乘法器。对于那些更关注性能的设计人员,全配置使用8KB的指令高速缓存,8K字节的数据高速缓存,3个周期的移位器和一个乘法器。对于需要采用折衷方法的用户,标准配置类似于完整的配置,但没有8K字节的高速数据缓存。表1展示了针对LatticeECP3 FPGA的资源利用率和性能。

表1 LatticeMico32资源利用率和使用LatticeECP3的性能

总结

LatticeMico32是一个完整的嵌入式微处理器设计方案。它提供了一个灵活的架构,并允许用户定制处理器系统以满足系统的要求(性能、成本、功耗)。处理器的IP和专用硬件的密切配合提供了一个易于使用的环境,这也可显著提升系统的性能,使设计拥有很大的灵活性。

LatticeMico32开发工具可以很容易地在FPGA中实现一个微处理器和与之连接的外围元件。易用性确保最少的设计时间,从而使得产品能够更快的上市。

根据开放源代码许可证和软件开发工具各自的开放源代码许可证,如Eclipse和GNU - GPL,提供生成的HDL,莱迪思可以让用户完全控制其设计。开放源代码为设计人员提供所需要的可视性,灵活性和便携性。

上一篇:由DSP构成的红外线实时监视报警系统

下一篇:基于四核DSP的视频交通检测系统设计

推荐阅读最新更新时间:2024-05-02 20:54

汽车电子的革新与FPGA-24页

汽车电子的革新与FPGA-24页 模拟集成电路设计与仿真

模拟集成电路设计与仿真

京公网安备 11010802033920号

京公网安备 11010802033920号